(54) УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ КАСКАДНОГО КОДА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство декодирования каскадного кода | 1976 |

|

SU633156A1 |

| Способ декодирования длинного блокового кода с помощью алгоритма Витерби | 2020 |

|

RU2747881C1 |

| Выходное устройство декодера Витерби | 1990 |

|

SU1775858A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ЛИНЕЙНЫХ КОДОВ | 1992 |

|

RU2035123C1 |

| СПОСОБ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ В СИСТЕМАХ ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2310273C2 |

| Способ декодирования линейного каскадного кода | 2017 |

|

RU2667370C1 |

| Способ кодирования и декодирования блокового кода с использованием алгоритма Витерби | 2015 |

|

RU2608872C1 |

| СПОСОБ ДЕКОДИРОВАНИЯ СВЕРТОЧНЫХ КОДОВ | 2012 |

|

RU2516624C1 |

| ПАРАЛЛЕЛЬНЫЙ КАСКАДНЫЙ СВЕРТОЧНЫЙ КОД С КОНЕЧНОЙ ПОСЛЕДОВАТЕЛЬНОСТЬЮ БИТОВ И ДЕКОДЕР ДЛЯ ТАКОГО КОДА | 1997 |

|

RU2187196C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОЦЕНКИ ОТНОШЕНИЯ СИГНАЛ-ШУМ ПРИ ДЕКОДИРОВАНИИ СВЕРТОЧНЫХ КОДОВ | 2010 |

|

RU2446448C1 |

Изобретение относится к передаче ийформации по каналам связи, где для повышения эффективности канала применяется каскадное кодирование со сверточными кодом в качестве внутреннего кода, декодируемого по алгоритму Витерби.

Известно устройство декодирования KackaAHof б кода.содержащее последовательно соединенные декодер внутреннего кода и декодер внешнего кода ll.

Однако в качестве внутреннего кода в этом устройстве применяется блоковый код и соответственно для его декодирования используется алгебраический декодер, который недостаточно эффективен в гауссовом канале СЁЯЗ.

Наиболее близким по технической сущности и достигаемому результату к изобретению является устройство для декодирования каскадного кода, содержашее декодер Витерби сверточного кода,; состоящий из мажоритарного элемента и триггеров, входы которых соединены с информационными входами устройства, выходы со входами мажоритарного.

элемента, выход которого через матрицу памяти соединен с первьил входом декодера алгебраического кода L2.

Для noBbmieНИН помехоустойчивости устройства декодирования каскадного KOJда предлагаемое устрсЛство содержит блок определения отношения числа единиц к числу нулей на его входах и дополнительную матрицу памяти, вылод которой подключен ко второму входу декодера алгебраического кода, вход - к вь коду лока определения отнмиения чиоtia единиц к числу нулей, входы которого подключены к выходам триггеров декодера Витерби сверточвого кода. Декодер алгебраического кода выполнен по схеме, позволяющей использовать весовую информацию о символах.

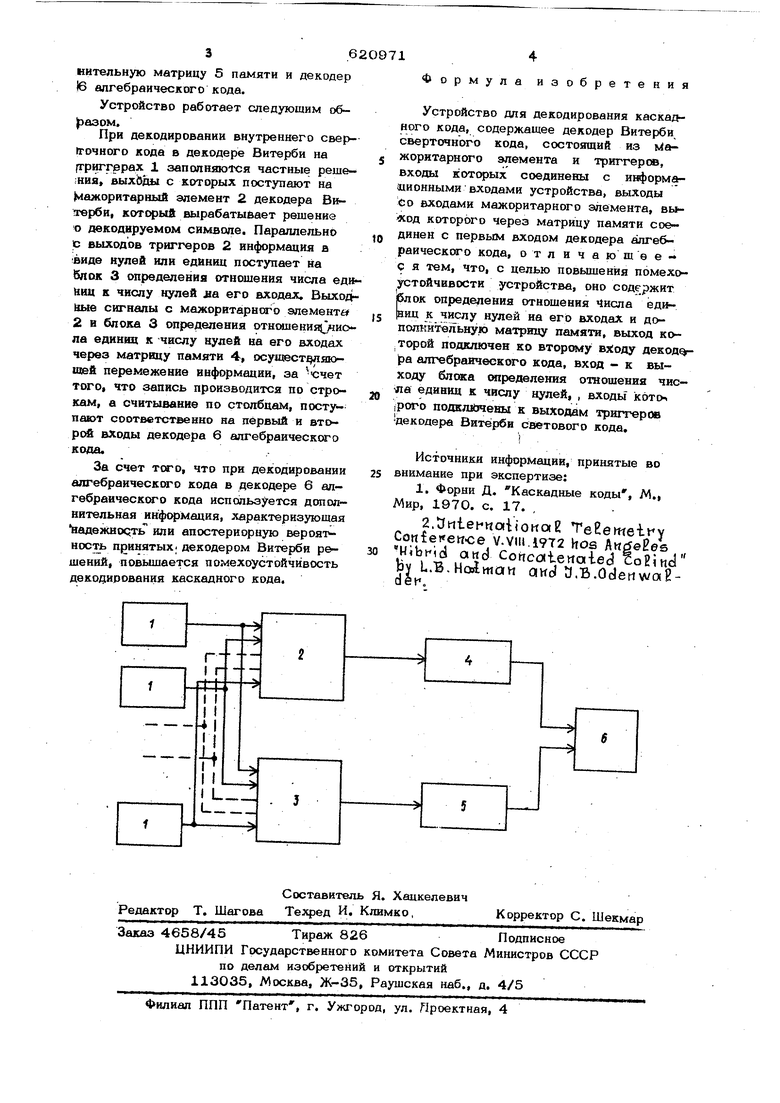

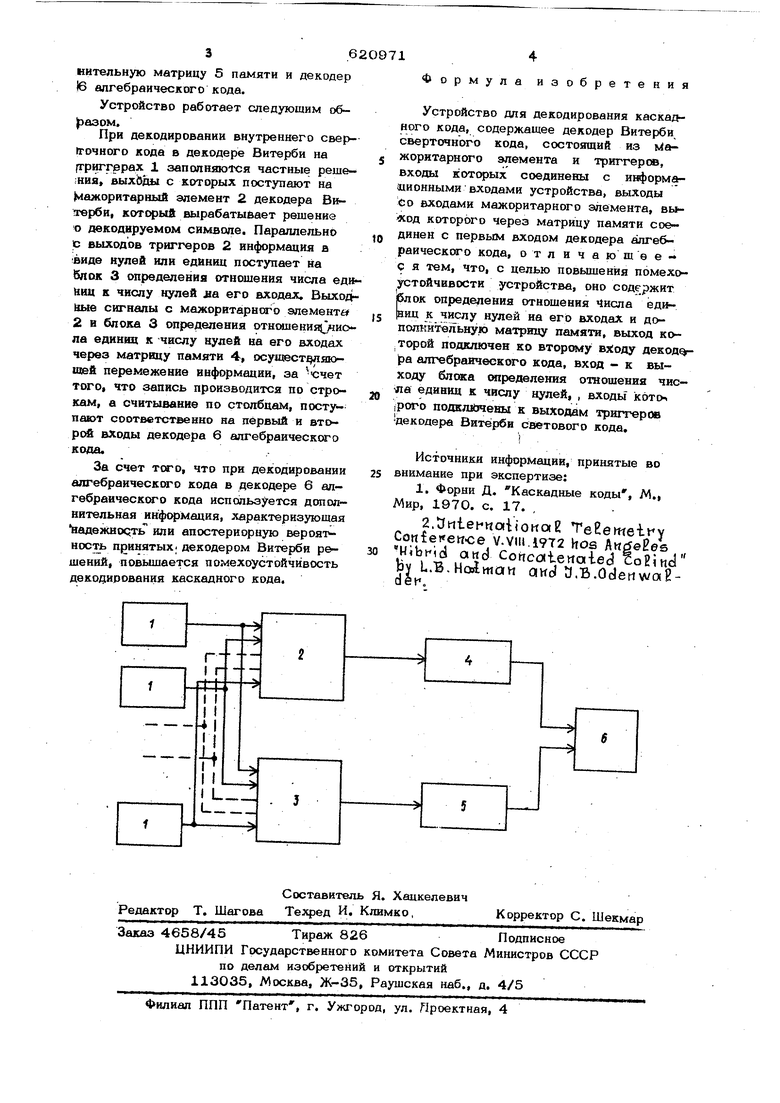

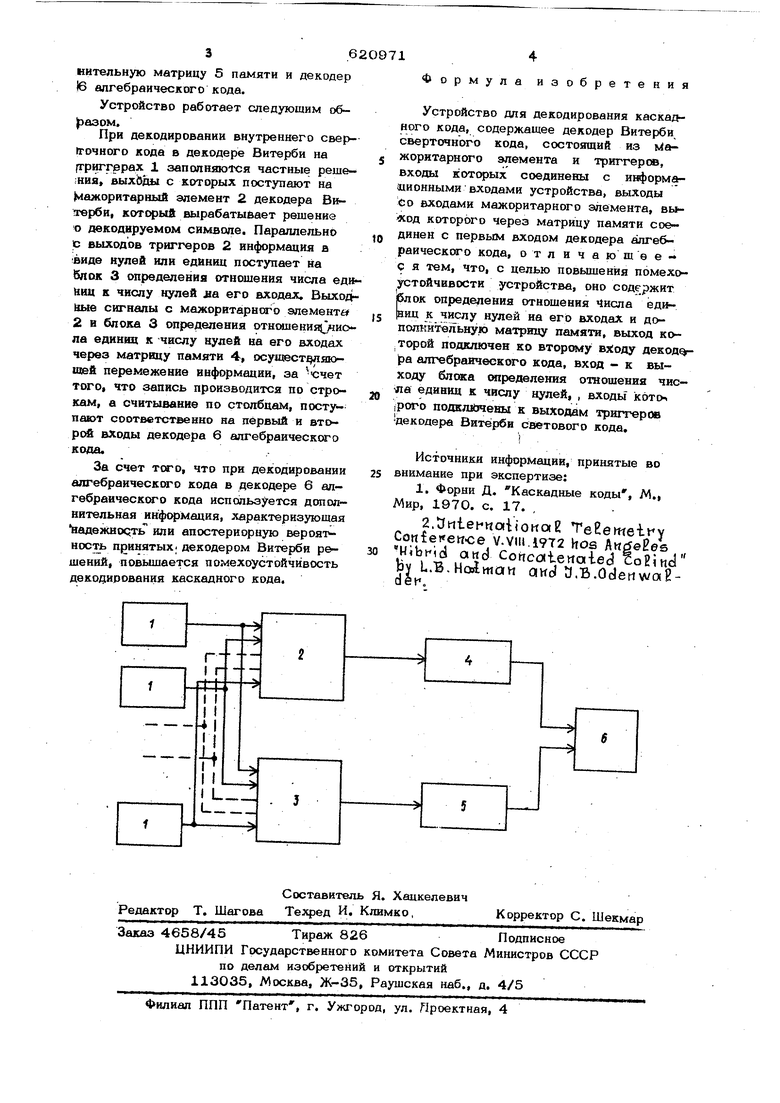

На чертеже дана блок-схема предлагаемого устройства.

Оно имеет триггеры 1 декодера Витерри, мажоритарный элемент 2, блок 3 определения числа единиц к числу нулей на его входах, матрицу 4 памяти, допо№нительную матрицу 5 памяти и декодер 16 алгебраического кода.

Устройство работает следующим образом.

При декодировании внутреннего свер(гочного кода в декодере Витерби на /триггерах 1 заполняются частные реше;ния, выходы с которых поступают на Мажоритарный элемент 2 декодера В торб и, который вырабатывает решение о декодируемом символе. Параллельно с выходов триггеров 2 информация в :виде нулей или единиц поступает на блок 3 определения отношения числа единиц к числу нулей ла его входах. Выходные сигналы с мажоритарного элементе 2 и блока 3 определения отнсинения чиола единиц к числу нулей на его входах через матрицу памяти 4, осущест яюшей перемеже ние информации, за счет того, что запись производится по строкам, а считывание по столбцам, поступают соответственно на первый н второй входы декодера 6 алгебраического кода.

За счет того, что прн декодировании алгебраического кода в декодере 6 алгебраическсяО кода используется дополнительная информация, характеризующая надеяшорть или апостериорную вероятность принятых; декодером Витерби решений, повышается п04мехоустойчивость декодирования каскадного кода.

Формула изобретения

Устройство для декодирования каскадного кода, содержащее декодер Витерби сверточного кода, состоящий из viaжоритарного элемента и триггере, входы koTqpHx соединены с информационными входами устройства, выходы Со входами мажоритарного элемента, вы«од которого через матрицу памяти соединен с первьо входом декодера алгебраического кода, о т л и ч а ю ш е е С я тем, что, с целью повьпиенйя помехоустойчивости устройства, оно содержит |блок определения отношения числа едириц к числу нулей на его входах и дополкйтвльную матрицу памяти, выход ко торой подключен ко второму взЯоду декод%|ра алгебранческого кода, вход - к выходу блока определения отношения числа единиц к числу нулей, , входы кото iporo подключены к выходим триггеров декодера Витерби светового кода, j

Источники информации, принятые во внимание при экспертизе:

Авторы

Даты

1978-08-25—Публикация

1973-12-10—Подача