Изобретение относится к вычислительной технике и технике связи и может быть использовано в аппаратуре передачи цифровых данных.

Известно выходное устройство декодера сверточного кода по алгоритму Витерби, которое содержит блок памяти, информационные входы которого являются одноименными входами устройства, буферный регистр, выходы которого соединены с соответствующими информационными входами устройства, блок синхронизации, первый вход которого является выходом устройства, блок синхронизации, первый выход которого подключен к входам синхронизации блока памяти и буферного регистра, второй - четвертый выходы блока синхронизации соединены с управляющим входом блока памяти, с управляющим входом и входом синхронизации выходного регистра, мультиплексор, информационные входы которого соединены с соответствующими выходами блока памяти, а выход и управляющие входы мультиплексора подключены

соответственно к информационному входу и первым (К-1)-м выходам буферного регистра, где К - кодовое ограничение сверточного кода.

Недостатком данного устройства являются большие аппаратурные затраты из-за регистровой организации блока памяти и большое количество связей, что уменьшает надежность устройства.

Наиболее близким по технической сущности является выходное устройство декодера сверточного кода по алгоритму Витерби, содержащее блок тактовой синхронизации, тактовый вход которого обьеди нен со входом формирователя адресов памяти путей и тактовым входом решающего блока и является тактовым входом устройства, первый выход блока тактовой синхронизации соединен со входом формирователя адресов записи, тактовыми входами формирователя адресов прослеживания путей, решающего блока, блока памяти, путей, блока прослеживания путей и управляющими входами первого и второго

(Л

С

N| VJ СЛ

00 СЛ 00

коммутаторов, выходы формирователя адресов памяти путей подключены к первым информационным входам второго коммутатора и установочным входам формирователя адресов прослеживания путей, первые выходы которого соединены со вторыми информационными входами второго коммутатора, выходы формирователя адресов записи подключены к первым информационным входам первого коммутатора и управляющим входам блока тактовой синхронизации, второй выход которого соединен с управляющим входом формирователя адресов прослеживания путей, второй выход которого подключен к управляющему входу решающего блока, выходы первого и второго коммутаторов соединены с первыми и вторыми информационными входами блока памяти путей, выходы которого подключены к информационным входам блока прослеживания путей, первые выходы которого соединены с информационными входами решающего блока и вторыми информационными входами первого коммутатора.

Недостатком данного устройства является отсутствие информации о достоверности информационных символов на выходе устройства, и следовательно снижение помехоустойчивости устройства при применении его в системах связи, использующих каскадное кодирование с внешними боковыми кодами,и внутренними сверточными кодами.

Цель изобретения - повышение помехоустойчивости аппаратуры передачи данных.

Для достижения указанной цели в выходное устройство декодера Витерби, содержащее блок тактовой синхронизации, тактовый вход которого, объединенный с тактовыми входами формирователя адресов памяти путей и решающего блока, является тактовым входом устройства, первый выход блока тактовой синхронизации соединен с тактовыми входами формирователя адресов записи, формирователя адресов прослеживания путей, блока прослеживания путей и управляющими входами первого и второго коммутаторов и блока памяти путей, информационный вход которого является входом устройства, а выход соединен с входом блока прослеживания путей, второй выход блока тактовой синхронизации соединен с управляющим входом формирователя адресов прослеживания путей, информацион- . ный вход которого, объединенный с первым входом второго коммутатора, подключен к выходу формирователя адресов памяти путей, второй выход формирователя адресов

прослеживания путей подключен к управляющему выходу решающего блока, а первый выход - ко второму входу второго коммутатора, выход которого соединен со старшими

разрядами адресного входа блока памяти путей, к младшим разрядам которого подключен выход первого коммутатора, первый вход которого, объединенный со вторым входом блока тактовой синхронизации, сое0 динен с выходом формирователя адресов памяти путей, а второй вход, объединенный с входом решающего блока - с выходом блока прослеживания путей, введены второй решающий блок и блок сравнения, при5 чем тактовый и управляющий входы второго решающего блока объединены с тактовым и управляющими входами первого решающего блока, вход соединен со вторым выходом блока прослеживания путей, а выход уст0 ройства - со вторым входом блока сравнения, первый вход которого соединен с выходом первого решающего блока, тактовый вход с тактовым входом первого решающего блока, а выход является вторым

5 выходом устройства. .

Сравнение основных методов повышения помехоустойчивости систем связи пока- зывает, что наиболее эффективным является каскадное соединение внешних

0 блоковых кодов и внутренних сверточных кодов с декодированием последних по алгоритму Витерби. Так, при вероятности ошибки р максимальный энергетический выигрыш кодирования (ЭВК) составляет 5-6

5 дБ как для блоковых,так и для сверточных кодов. Применение же каскадной системы с внешним кодом Рида-Соломона и внутренним сверточным кодом позволяет получить ЭВК 6,5-7,5 дБ, Максимальный ЭВК дости0 гается в случае, если на вход декодера внеш- него кода помимо информационных символов поступают символы стираний (метки надежности, указывающие на наименее надежные информационные символы).

5 Такой подход позволяет дополнительно уве- личить ЭВК каскадной системы на 1 дБ, и, следовательно, повысить ее помехоустойчивость или пропускную способность. Благодаря введению второго решающего блока и

0 блока сравнения обеспечивается прослеживание двух независимых непрерывных путей и формируются метки надежности, указывающие на недостоверно принятые символы, благодаря чему увеличивается по5 мехоустойчивость приема данных.

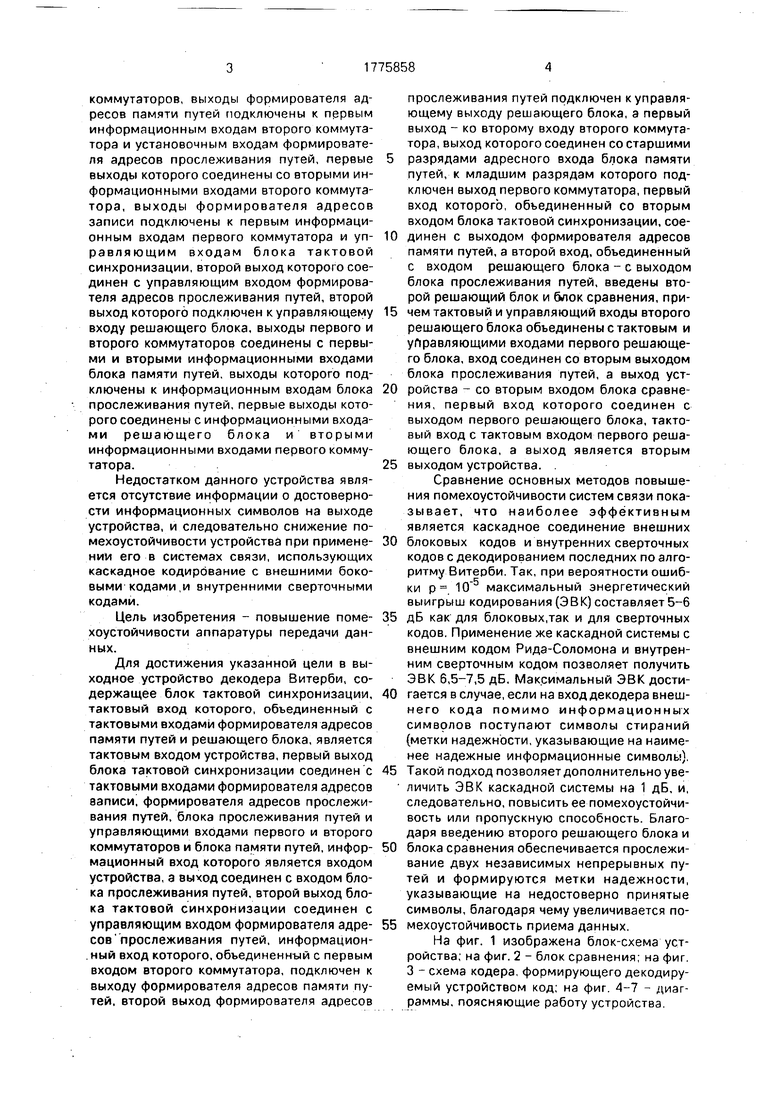

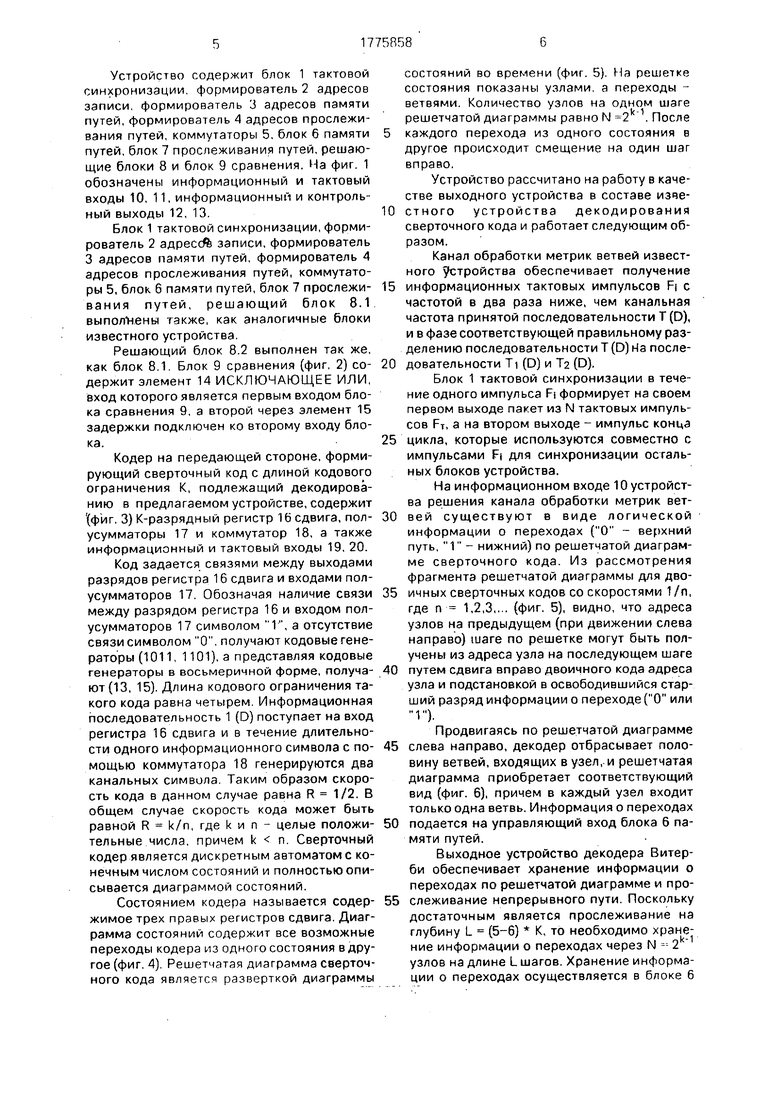

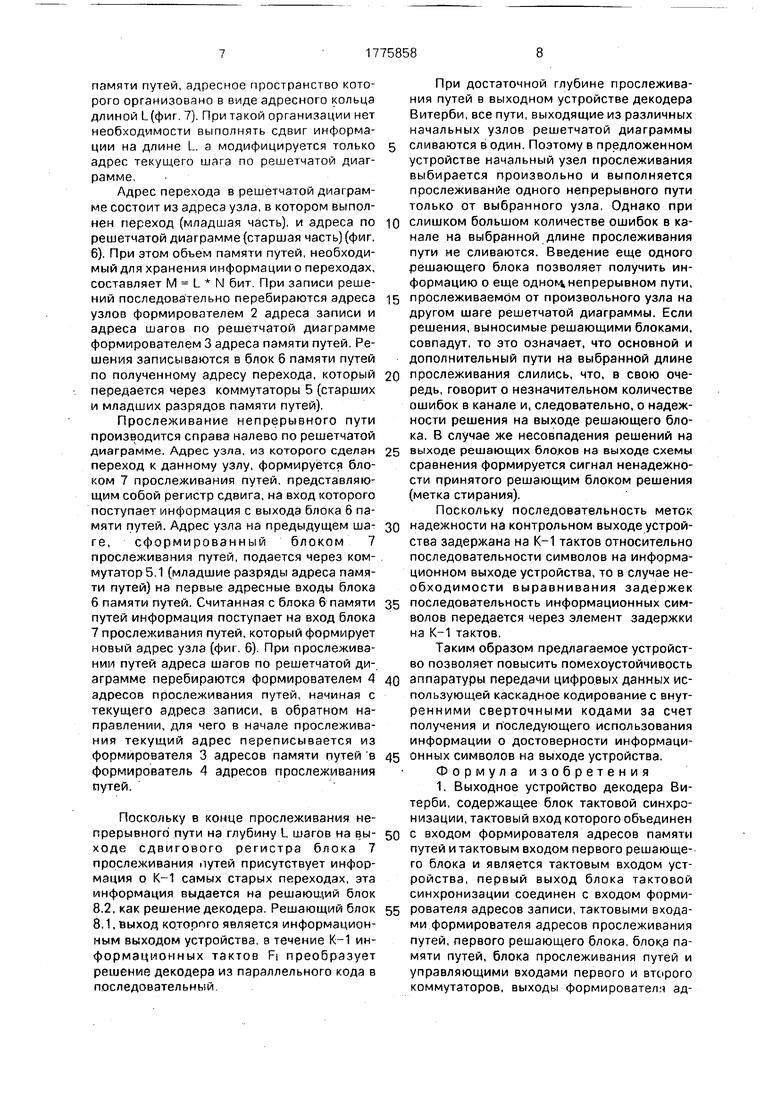

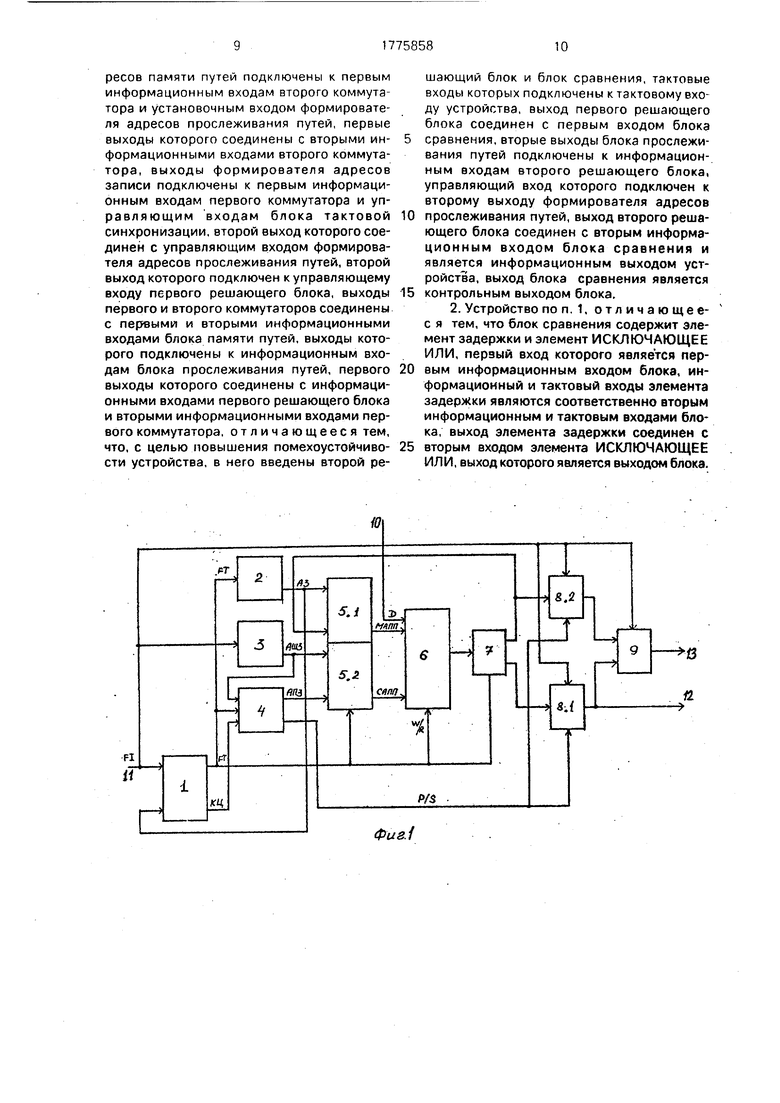

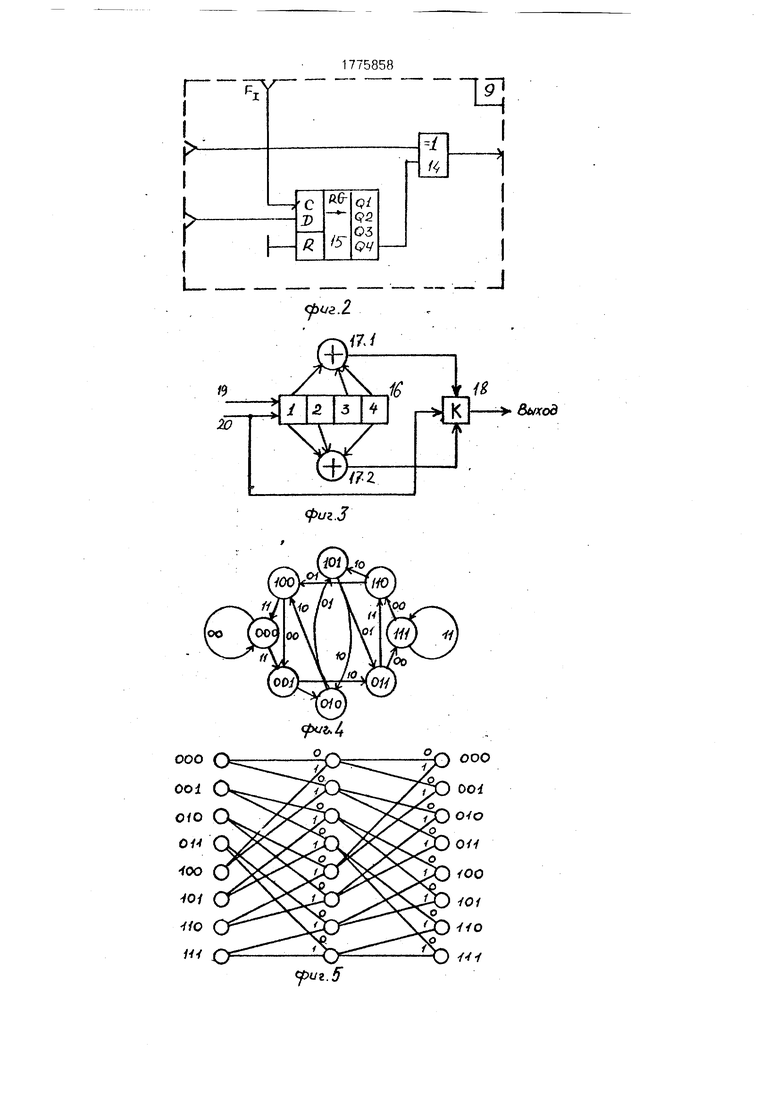

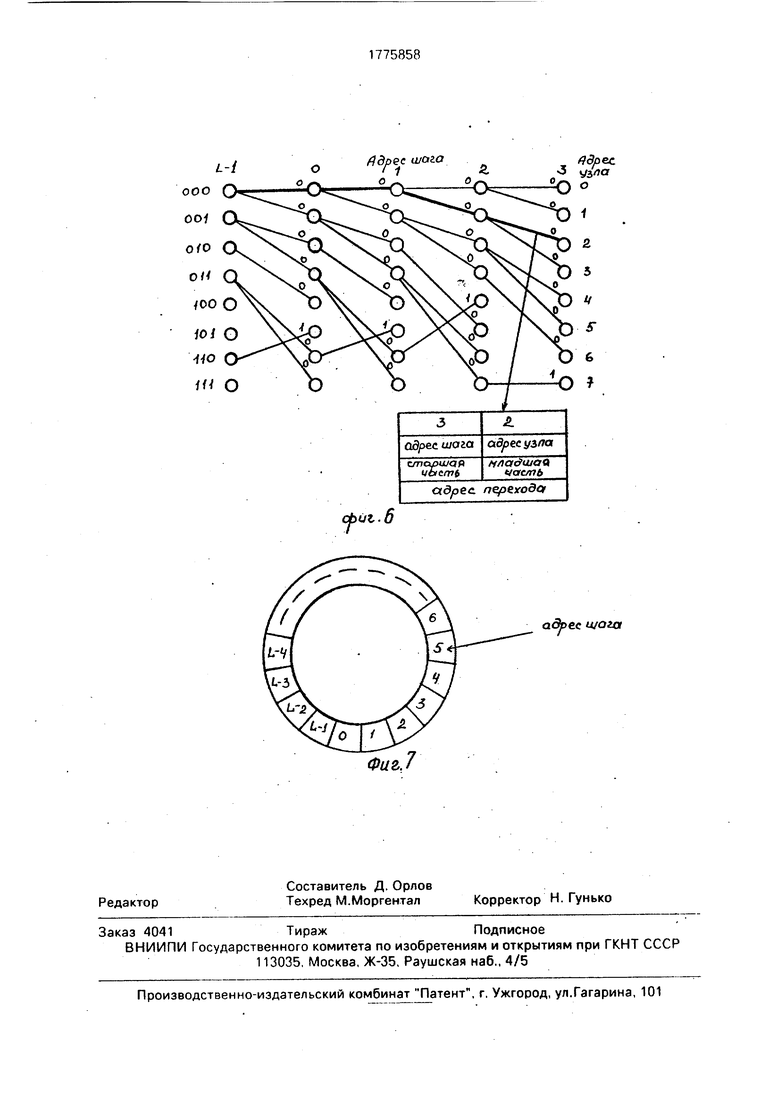

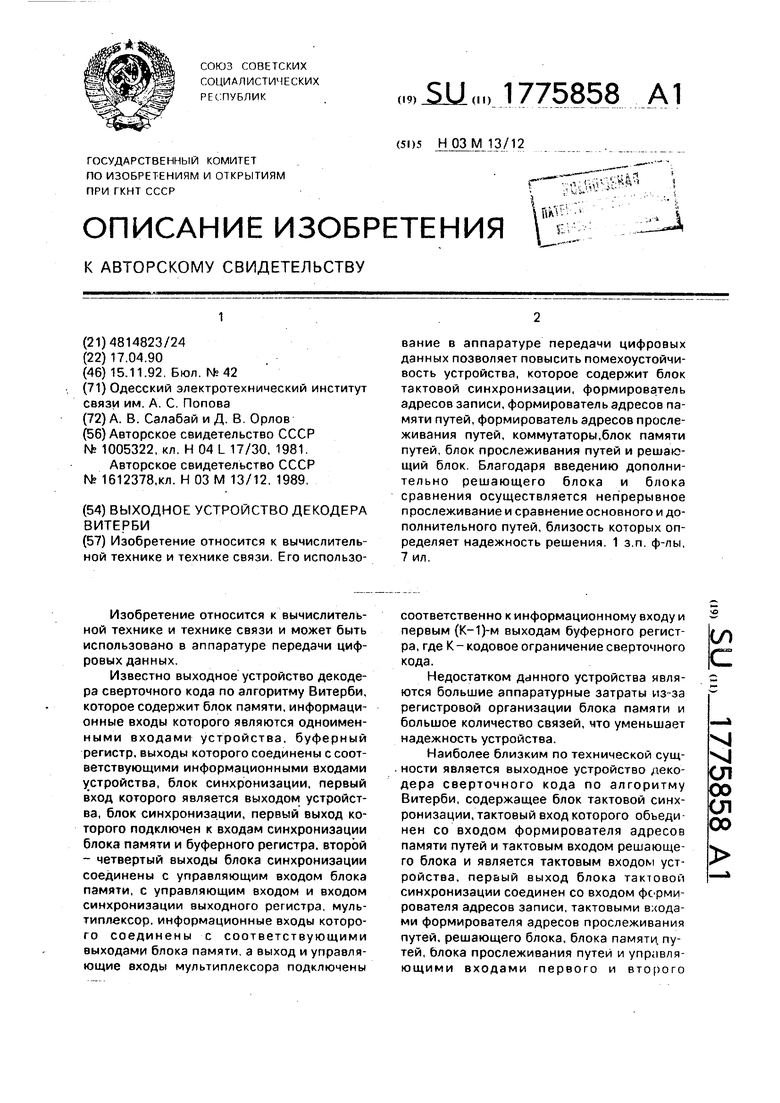

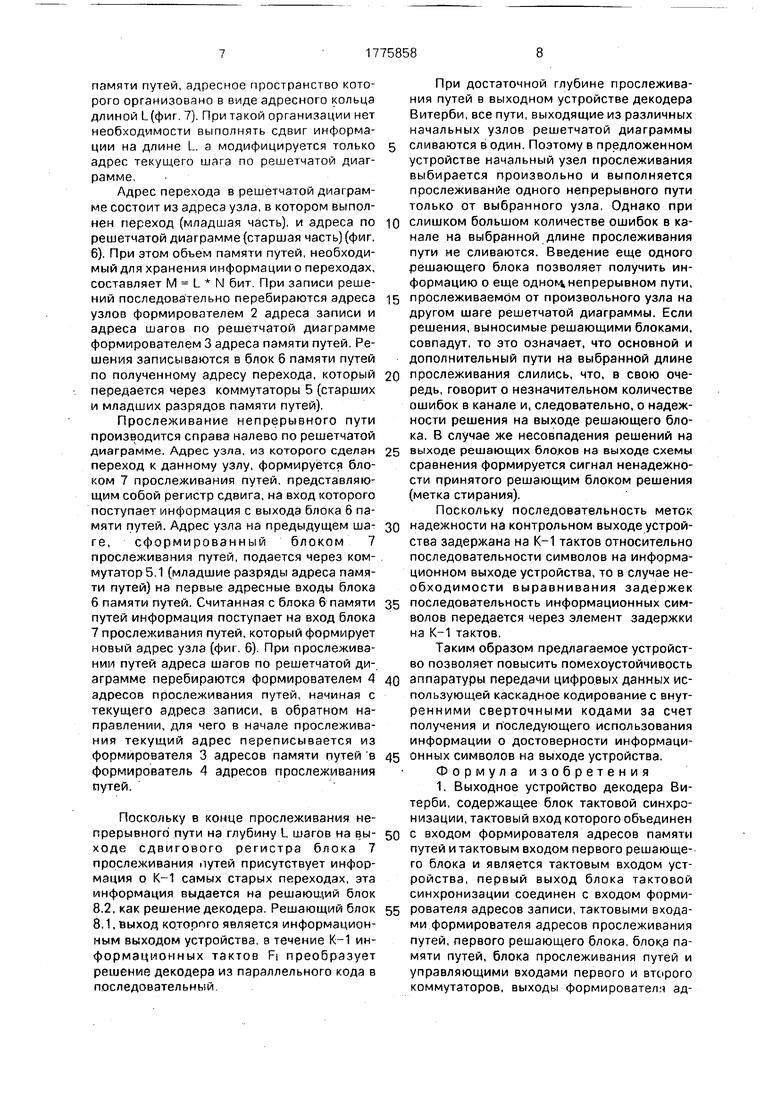

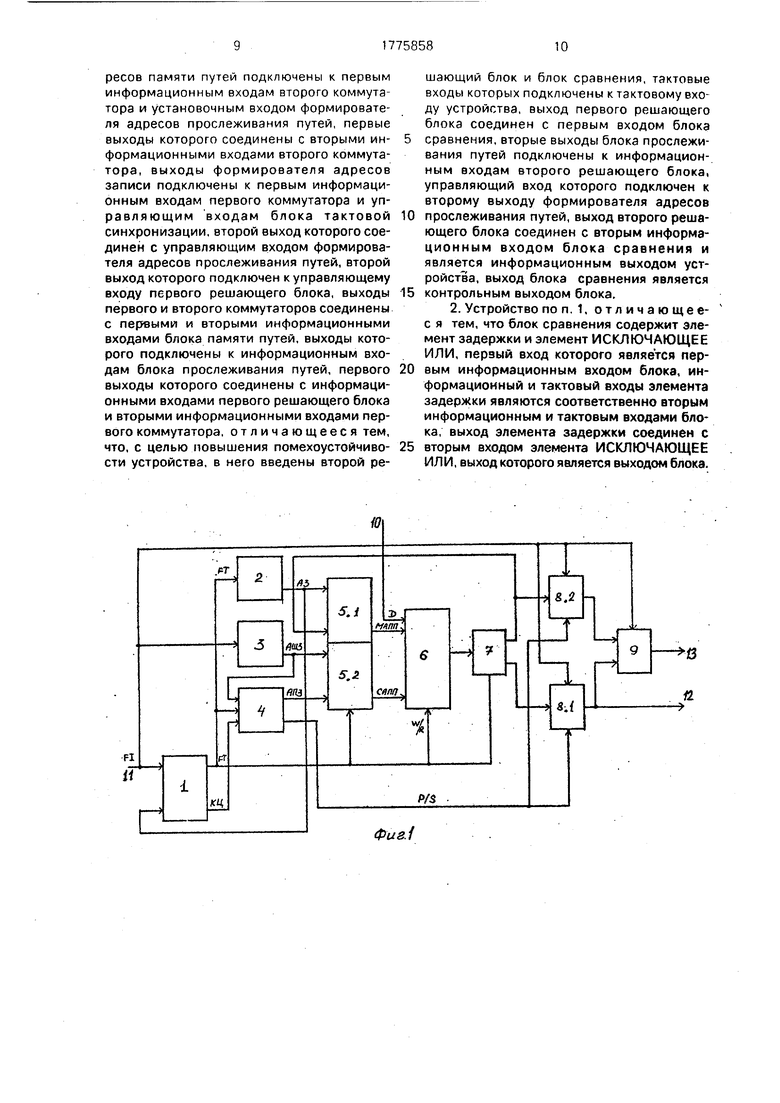

На фиг. 1 изображена блок-схема устройства; на фиг. 2 - блок сравнения; на фиг. 3 - схема кодера, формирующего декодируемый устройством код; на фиг. 4-7 - диаграммы, поясняющие работу устройства.

Устройство содержит блок 1 тактовой синхронизации, формирователь 2 адресов записи, формирователь 3 адресов памяти путей, формирователь 4 адресов прослеживания путей, коммутаторы 5, блок 6 памяти путей, блок 7 прослеживания путей, решающие блоки 8 и блок 9 сравнения. На фиг. 1 обозначены информационный и тактовый входы 10, 11, информационный и контрольный выходы 12, 13.

Блок 1 тактовой синхронизации, формирователь 2 адресов записи, формирователь 3 адресов памяти путей, формирователь 4 адресов прослеживания путей, коммутаторы 5, блок 6 памяти путей, блок 7 прослежи- вания путей, решающий блок 8.1 выполнены также, как аналогичные блоки известного устройства.

Решающий блок 8.2 выполнен так же, как блок 8.1. Блок 9 сравнения (фиг. 2) содержит элемент 14 ИСКЛЮЧАЮЩЕЕ ИЛИ, вход которого является первым входом блока сравнения 9, а второй через элемент 15 задержки подключен ко второму входу блока.

Кодер на передающей стороне, формирующий сверточный код с длиной кодового ограничения К, подлежащий декодированию в предлагаемом устройстве, содержит (фиг. 3) К-разрядный регистр 16 сдвига, полусумматоры 17 и коммутатор 18, а также информационный и тактовый входы 19, 20.

Код задается связями между выходами разрядов регистра 16 сдвига и входами полусумматоров 17. Обозначая наличие связи между разрядом регистра 16 и входом полусумматоров 17 символом 1, а отсутствие связи символом О, получают кодовые генераторы (1011, 1101), а представляя кодовые генераторы в восьмеричной форме, получают (13, 15). Длина кодового ограничения такого кода равна четырем. Информационная последовательность 1 (D) поступает на вход регистра 16 сдвига и в течение длительности одного информационного символа с помощью коммутатора 18 генерируются два канальных символа. Таким образом скорость кода в данном случае равна R 1/2. В общем случае скорость кода может быть равной R k/n, где k и п - целые положительные числа, причем k п. Сверточный кодер является дискретным автоматом с конечным числом состояний и полностью описывается диаграммой состояний.

Состоянием кодера называется содержимое трех правых регистров сдвига. Диаграмма состояний содержит все возможные переходы кодера из одного состояния в другое (фиг. 4). Решетчатая диаграмма сверточ- ного кода является разверткой диаграммы

состояний во времени (фиг. 5). На решетке состояния показаны узлами, а переходы - ветвями. Количество узлов на одном шаге решетчатой диаграммы равно N 2k 1. После

каждого перехода из одного состояния в другое происходит смещение на один шаг вправо.

Устройство рассчитано на работу в качестве выходного устройства в составе изве0 стного устройства декодирования сверточного кода и работает следующим образом.

Канал обработки метрик ветвей известного устройства обеспечивает получение

5 информационных тактовых импульсов FI с частотой в два раза ниже, чем канальная частота принятой последовательности Т (D), и в фазе соответствующей правильному разделению последовательности Т (D) На после0 довательности TI (D) и Та (D).

Блок 1 тактовой синхронизации в течение одного импульса F формирует на своем первом выходе пакет из N тактовых импульсов FT, а на втором выходе - импульс конца

5 цикла, которые используются совместно с импульсами FJ для синхронизации остальных блоков устройства.

На информационном входе 10 устройства решения канала обработки метрик вет0 вей существуют в виде логической информации о переходах (О - верхний путь, 1 - нижний) по решетчатой диаграмме сверточного кода. Из рассмотрения фрагмента решетчатой диаграммы для дво5 ичных сверточных кодов со скоростями 1 /п, где п 1,2,3,... (фиг. 5), видно, что адреса узлов на предыдущем (при движении слева направо) шаге по решетке могут быть получены из адреса узла на последующем шаге

0 путем сдвига вправо двоичного кода адреса узла и подстановкой в освободившийся старший разряд информации о переходе (О или 1).

Продвигаясь по решетчатой диаграмме

5 слева направо, декодер отбрасывает половину ветвей, входящих в узел, и решетчатая диаграмма приобретает соответствующий вид (фиг. 6), причем в каждый узел входит только одна ветвь. Информация о переходах

0 подается на управляющий вход блока 6 памяти путей.

Выходное устройство декодера Витер- би обеспечивает хранение информации о переходах по решетчатой диаграмме и про5 слеживание непрерывного пути. Поскольку достаточным является прослеживание на глубину L (5-6) К, то необходимо хранение информации о переходах через N - 2 узлов на длине L шагов. Хранение информации о переходах осуществляется в блоке 6

памяти путей, адресное пространство которого организовано в виде адресного кольца длиной Цфиг. 7). При такой организации нет необходимости выполнять сдвиг информации на длине L. а модифицируется только адрес текущего шага по решетчатой диаграмме.

Адрес перехода в решетчатой диаграмме состоит из адреса узла, в котором выполнен переход (младшая часть), и адреса по решетчатой диаграмме {старшая часть) (фиг. 6). При этом объем памяти путей, необходимый для хранения информации о переходах, составляет М L N бит. При записи решений последовательно перебираются адреса узлов формирователем 2 адреса записи и адреса шагов по решетчатой диаграмме формирователем 3 адреса памяти путей. Решения записываются в блок 6 памяти путей по полученному адресу перехода, который передается через коммутаторы 5 (старших и младших разрядов памяти путей).

Прослеживание непрерывного пути производится справа налево по решетчатой диаграмме. Адрес узла, из которого сделан переход к данному узлу, формируется блоком 7 прослеживания путей, представляющим собой регистр сдвига, на вход которого поступает информация с выхода блока 6 памяти путей. Адрес узла на предыдущем шаге, сформированный блоком 7 прослеживания путей, подается через коммутатор 5.1 (младшие разряды адреса памяти путей) на первые адресные входы блока

6памяти путей. Считанная с блока 6 памяти путей информация поступает на вход блока

7прослеживания путей, который формирует новый адрес узла (фиг. 6). При прослеживании путей адреса шагов по решетчатой диаграмме перебираются формирователем 4 адресов прослеживания путей, начиная с текущего адреса записи, в обратном направлении, для чего в начале прослеживания текущий адрес переписывается из формирователя 3 адресов памяти путей в формирователь 4 адресов прослеживания путей.

Поскольку в конце прослеживания непрерывного пути на глубину L шагов на выходе сдвигового регистра блока 7 прослеживания путей присутствует информация о К-1 самых старых переходах, эта информация выдается на решающий блок 8.2, как решение декодера. Решающий блок 8,1, выход которого является информационным выходом устройства, в течение К-1 информационных тактов FI преобразует решение декодера из параллельного кода в последовательный

При достаточной глубине прослеживания путей в выходном устройстве декодера Витерби, все пути, выходящие из различных начальных узлов решетчатой диаграммы

сливаются в один. Поэтому в предложенном устройстве начальный узел прослеживания выбирается произвольно и выполняется прослеживание одного непрерывного пути только от выбранного узла, Однако при

0 слишком большом количестве ошибок в канале на выбранной длине прослеживания пути не сливаются. Введение еще одного решающего блока позволяет получить информацию о еще одном,непрерывном пути,

5 прослеживаемом от произвольного узла на другом шаге решетчатой диаграммы. Если решения, выносимые решающими блоками, совпадут, то это означает, что основной и дополнительный пути на выбранной длине

0 прослеживания слились, что, в свою очередь, говорит о незначительном количестве ошибок в канале и, следовательно, о надежности решения на выходе решающего блока. В случае же несовпадения решений на

5 выходе решающих блоков на выходе схемы сравнения формируется сигнал ненадежности принятого решающим блоком решения (метка стирания).

Поскольку последовательность меток

0 надежности на контрольном выходе устройства задержана на К-1 тактов относительно последовательности символов на информационном выходе устройства, то в случае необходимости выравнивания задержек

5 последовательность информационных символов передается через элемент задержки на К-1 тактов.

Таким образом предлагаемое устройство позволяет повысить помехоустойчивость

0 аппаратуры передачи цифровых данных использующей каскадное кодирование с внутренними сверточными кодами за счет получения и последующего использования информации о достоверности информаци5 онных символов на выходе устройства. Формула изобретения 1. Выходное устройство декодера Витерби, содержащее блок тактовой синхронизации, тактовый вход которого объединен

0 с входом формирователя адресов памяти путей и тактовым входом первого решающего блока и является тактовым входом устройства, первый выход блока тактовой синхронизации соединен с входом форми5 рователя адресов записи, тактовыми входами формирователя адресов прослеживания путей, первого решающего блока, блока памяти путей, блока прослеживания путей и управляющими входами первого и второго коммутаторов, выходы формирователи адресов памяти путей подключены к первым информационным входам второго коммутатора и установочным входом формирователя адресов прослеживания путей, первые выходы которого соединены с вторыми ин- формационными входами второго коммутатора, выходы формирователя адресов записи подключены к первым информационным входам первого коммутатора и управляющим входам блока тактовой синхронизации, второй выход которого соединен с управляющим входом формирователя адресов прослеживания путей, второй выход которого подключен к управляющему входу первого решающего блока, выходы первого и второго коммутаторов соединены с первыми и вторыми информационными входами блока памяти путей, выходы которого подключены к информационным входам блока прослеживания путей, первого выходы которого соединены с информационными входами первого решающего блока и вторыми информационными входами первого коммутатора, отличающееся тем, что, с целью повышения помехоустойчиво- сти устройства, в него введены второй решающий блок и блок сравнения, тактовые входы которых подключены к тактовому входу устройства, выход первого решающего блока соединен с первым входом блока сравнения, вторые выходы блока прослеживания путей подключены к информационным входам второго решающего блока, управляющий вход которого подключен к второму выходу формирователя адресов прослеживания путей, выход второго решающего блока соединен с вторым информационным входом блока сравнения и является информационным выходом устройства, выход блока сравнения является контрольным выходом блока.

2. Устройство по п. 1, отличающее- с я тем, что блок сравнения содержит элемент задержки и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого является первым информационным входом блока, информационный и тактовый входы элемента задержки являются соответственно вторым информационным и тактовым входами блока, выход элемента задержки соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования сверточного кода | 1989 |

|

SU1612378A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА | 1991 |

|

RU2035124C1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМНО-ДЕМОДУЛИРУЮЩЕЕ УСТРОЙСТВО ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ СИСТЕМ СВЯЗИ | 2005 |

|

RU2305375C2 |

| УСТРОЙСТВО ВЫЧИСЛЕНИЯ МЕТРИК ПУТЕЙ ДЕКОДЕРА ВИТЕРБИ | 1990 |

|

RU2022473C1 |

| УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДИСКРЕТНЫХ СИГНАЛОВ В КАНАЛАХ С ГРУППИРОВАНИЕМ ОШИБОК | 1998 |

|

RU2127956C1 |

| Выходное устройство декодера Витерби | 1985 |

|

SU1367165A1 |

| Кодек для системы связи с многократной фазовой модуляцией | 1987 |

|

SU1629992A1 |

| СПОСОБ ПЕРЕДАЧИ ГОЛОСОВЫХ ДАННЫХ В ЦИФРОВОЙ СИСТЕМЕ РАДИОСВЯЗИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2005 |

|

RU2301492C2 |

| Кодек блочной сигнально-кодовой конструкции | 1989 |

|

SU1711337A1 |

| МНОГОСКОРОСТНОЙ ПОСЛЕДОВАТЕЛЬНЫЙ ДЕКОДЕР ВИТЕРБИ ДЛЯ ИСПОЛЬЗОВАНИЯ В СИСТЕМЕ МНОГОСТАНЦИОННОГО ДОСТУПА С КОДОВЫМ РАЗДЕЛЕНИЕМ | 1994 |

|

RU2222110C2 |

Изобретение относится к вычислительной технике и технике связи. Его использование в аппаратуре передачи цифровых данных позволяет повысить помехоустойчивость устройства, которое содержит блок тактовой синхронизации, формирователь адресов записи, формирователь адресов памяти путей, формирователь адресов прослеживания путей, коммутаторы,блок памяти путей, блок прослеживания путей и решающий блок Благодаря введению дополнительно решающего блока и блока сравнения осуществляется непрерывное прослеживание и сравнение основного и дополнительного путей, близость которых определяет надежность решения. 1 з.п. ф-лы, 7 ил.

Фиа.1

Nj 3

3

}

IV

i

S §

abut. 6

о уз ло

адрес и/ага

Фа&.7

| Устройство декодирования сверточного кода | 1981 |

|

SU1005322A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для декодирования сверточного кода | 1989 |

|

SU1612378A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-11-15—Публикация

1990-04-17—Подача