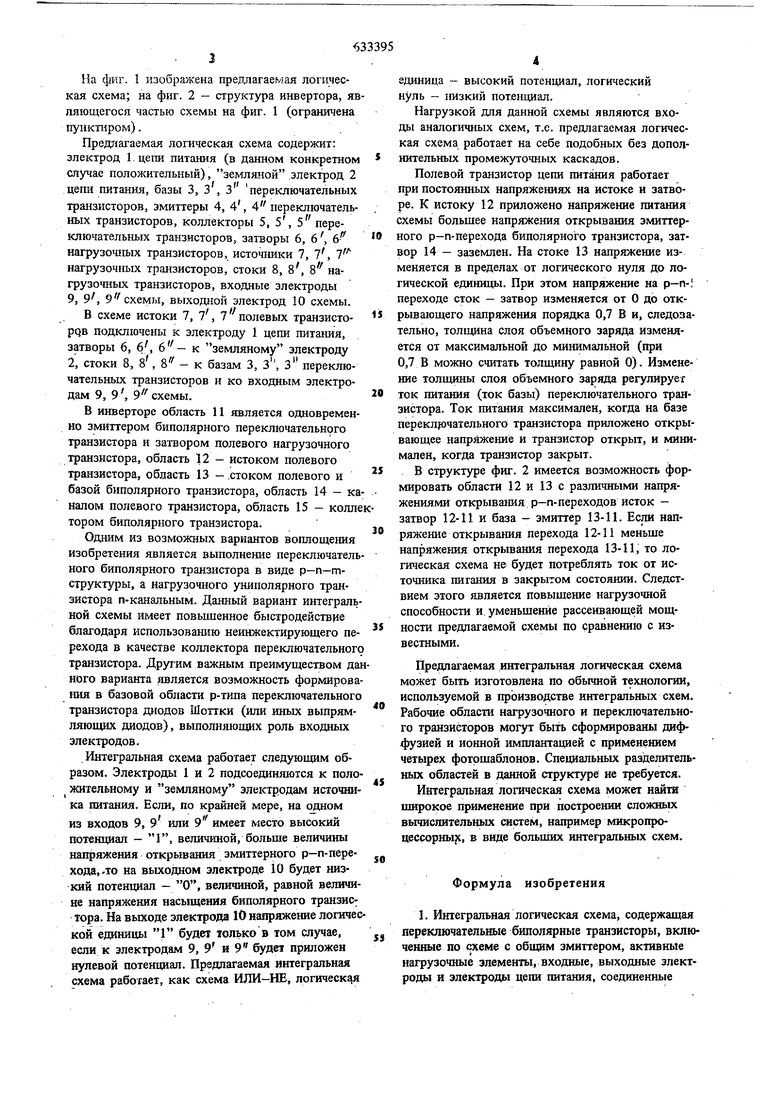

Настоящее изобретение относится к области микроэлектроники, а именно, к производству полупроводниковых интегральных схем высокой степени интеграции. Известны интегральные логические, схемы с непосредственными связями для цифровых устройств обработки и хранения дискретной инфор мации 1. Логические схемы данного класса содержат переключательные биполярные транзисторы, включенные по схеме с общим эмиттером, и нагрузочные элементы. В качестве последних в известных схемах используются пассивные и активные электронные элементы. Наиболее близкими к предлагаемой по техни ческой сущности являются схемы, которые содержат переключательные биполярные транзисто ры, включенные по схеме с общим эмиттером, активные нагрузочные элементы, входные, выходные электроды и электроды цепи питания, соединенные соответственно с базами, коллекторами и эмиттерами переключательных транзисторов 12. Однако эти схемы имеют неэкономичную цеп питания, представляющую собой биполярный тр зистор дополняющего типа проводимости, включенный по схеме с общей базой и имеющий резкий коэффициент передачи тока между эмиттером и коллектором. В связи с этим значительная часть мощности, потребляемой логической ;хемой от источника питания, рассеивается в схеме. Кроме того, нагрузочная способность схемы сравнительно невысока, что обусловлено коэффициентом усиления переключательного транзистора и необходимостью в открытом состоянии пропускать сравнительно больщой ток, равный сумме базовых токов транзисторов, подключенных к выходу схемы. Цель изобретения - уменьщение потребляемой мощности. Это достигается выполнением нагрузочных элементов в виде полевых транзисторов с затворами в виде р-п-переходов, соединением затворов и стоков соответственно с эмиттерами и базами переключательных транзисторов и подключением истоков к электроду цепи питания. Причем коллекторный переход переключательного транзистора выполнен в виде иеинжектирующего контакта. На фиг. 1 изображена предлагаемая логическая схема; на фиг. 2 - структура инвертора, яв ляющегося частью схемы на фиг. 1 (ограничена пунктиром). Предлагаемая логаческая схема содержит: электрод 1.цепи питания (в данном конкретном случае положительный), земляной электрод 2 цепи питания, базы 3, з, З переключательных транзисторов, эмиттеры 4, 4, 4 переключательных транзисторов, коллекторы 5, 5, 5 переключательных транзисторов, затворы 6, б , б нагрузочных транзисторов, истошшки 7, 7, нагрузочных транзисторов, стоки 8, 8, нагрузошых транзисторов, входные электроды 9, 9, 9 схемы, выходной электрод 10 схемы. В схеме истоки 7, 7, 7 полевых транзистоPQB подключены к электроду 1 цепи питания, затворы 6, 6, к земляному электроду 2, стоки 8, в , 8 - к базам 3, З, З переключательных транзисторов и ко входным электродам 9, 9, 9схемы. В инверторе область 11 является одновременно эмиттером биполярного переключательного транзистора и затвором полевого нагрузочного транзистора, область 12 - истоком полевого транзистора, область 13 - .стоком полевого и базой биполярного транзистора, область 14 - ка налом полевого транзистора, область 15 - колле тором биполярного транзистора. Одним из возможных вариантов воплоще1шя изобретения является выполнение переключатель ного биполярного транзистора в виде р-п-тструкту1зы, а нагрузочного униполярного транзистора п-канальным. Данный вариант интегральной схемы имеет повьииенное быстродействие благодаря использованию неинжектирующего нерехода в качестве коллектора переключательного транзистора. Другим важным преимуществом дан ного варианта является возможность формирова шш в базовой области р-типа переключательного транзистора диодов Шоттки (или иных выпрямляющих диодов), выполняющих роль входных электродов. .Интегральная схема работает следующим образом. Электроды 1 и 2 подсоединяются к положительному и земляному электродам источю ка питания. Если, по крайней мере, на одном из входов 9, 9 или 9 имеет место высокий потенциал - 1, величиной, больше величины напряжения открывания эмиттерного р-п-перехода,-то на выходном электроде 10 будет низкий потенциал - О, величиной, равной величине напряжения насыщения биполярного транзис тора. На выходе электрода 10 напряжение логичес кой едишщы 1 будет только в том случае, если к электродам 9, 9 и 9 будет приложен нулевой потенциал. Предлагаемая интегральная схема работает, как схема ЙЛИ-НЕ, логически единица - высокий потенциал, логический нуль - низкий потенциал. Нагрузкой для данной схемы являются входы аналогичных схем, т.е. предлагаемая логическая схема работает на себе подобных без дополнительных промежуточных каскадов. Полевой транзистор цепи питания работает при постоянных напряжениях на истоке и затворе. К истоку 12 приложено напряжение питания схемы большее напряжения открывания эмиттерного р-п-перехода биполярного транзистора, затвор 14 - заземлен. На стоке 13 напряжение изменяется в пределах от логического нуля до логической единицы. При этом напряжение на р-п-1 переходе сток - затвор изменяется от О до открывающего напряжения порядка 0,7 В и, следовательно, толщина слоя объемного заряда изменяется от максимальной до минимальной (при 0,7 В можно считать толщину равной 0). Изменение толщины слоя объемного заряда регулирует ток питания (ток базы) переключательного транзистора. Ток питания максимален, когда на базе переключательного транзистора приложено открывающее напряжение и транзистор открыт, и минимален, когда транзистор закрыт. В структуре фиг. 2 имеется возможность формировать области 12 и 13 с различными напряжениями открыва шя р-п-переходов исток - затвор 12-11 и база - эмиттер 13-11. Если напряжение открывания перехода 12-11 меньше напряжения открывания перехода 13-11, то логическая схема не будет потреблять ток от источника питания в закрытом состоянии. Следствием этого является повышение нагрузочной способности и уменьшение рассеивающей мощности предлагаемой схемы по сравнению с известными. Предлагаемая интегральная логическая схема может быть изготовлена по обычной технологии, используемой в производстве интегральных схем. Рабочие области нагрузочного и переключательного транзисторов могут быть сформированы диффузией и ионной имплантацией с применением четырех фотошаблонов. Специальных разделительных областей в данной структуре не требуется. Интегральная логическая схема может найти широкое применение при построении сложных вычислительных систем, например микропроцессорны, в виде больших интегральных схем. Формула изобретения 1. Интегральная логическая схема, содержащая переключательные биполярные транзисторы, включенные по схеме с общим эмиттером, активные нагрузочные элементы, входные, выходные электроды и электроды цепи питания, соединенные

соответственно с базами, коллекторами и эмиттерами переключательных транзисторов, отличающаяся тем, что, с целью уменьшения потребляемой мощности, нагрузочные элементы выполнены в виде полевых транзисторов с затворами в виде р-п-переходов, при этом затворы, стоки и истоки соединены соответственно с эмиттерами, базами переключательных транзисторов и электродом цепи питания.

1 Схема по п. 1, отличающаяся тем, что коллекторный переход переключательного транзистора выполнен в виде неинжектирующего контакта.

Источники информации, принятце во внимание при экспертизе

1.Патент Франции N 2017324, кл. Н 01 L 27/00, 1973.

2.Патент Франции № 2175752, кл. Н 01 L 27/00, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральный логический элемент | 1977 |

|

SU602055A1 |

| Интегральный инвертор | 1975 |

|

SU519102A1 |

| Функциональный преобразователь | 1978 |

|

SU750516A1 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ (ВАРИАНТЫ) | 1994 |

|

RU2076441C1 |

| Компенсационный стабилизатор постоянного напряжения | 1981 |

|

SU922698A1 |

| ФУНКЦИОНАЛЬНО-ИНТЕГРИРОВАННАЯ ЯЧЕЙКА ФОТОЧУВСТВИТЕЛЬНОЙ МАТРИЦЫ | 2012 |

|

RU2517917C2 |

| ИНТЕГРАЛЬНАЯ ТРАНЗИСТОРНАЯ MOS СТРУКТУРА | 2001 |

|

RU2207662C1 |

| ИНТЕГРАЛЬНАЯ СХЕМА СИЛОВОГО БИПОЛЯРНО-ПОЛЕВОГО ТРАНЗИСТОРА | 2015 |

|

RU2585880C1 |

| Генератор импульсов | 1990 |

|

SU1824667A1 |

| Одновибратор | 1978 |

|

SU764105A2 |

0 f f Jo Ь

11 U

I - 1

1

JS

Авторы

Даты

1979-05-25—Публикация

1977-01-10—Подача