Изобретение относится к микроэлектронике, а более конкретно к интегральным транзисторным структурам типа MOS.

Известны интегральные транзисторные структуры с каналами n и р типа проводимости и затворами в виде MOS структуры (см., например, пат. США 4149176, complementay MOSFET device, фиг. 10, 1979).

Наиболее близкой по технической сущности конструкцией, выбранной в качестве прототипа, является конструкция транзисторной структуры MOSFET типа SOI (см., например, Chenming Hu "Silicon nenoelectronics for the 21st century" Nenotechnology 10 (1999) 113-116. Printed in the UK. PII: S0957-4484(99)97402-0).

Существенным недостатком известных интегральных транзисторных MOS структур является их сравнительно низкое быстродействие в цифровых схемах типа CMOS. Этот недостаток обусловлен тем, что MOS структура способна коммутировать токи сравнительно небольшой величины.

В изобретении ставится задача увеличения быстродействия интегральных транзисторных MOS структур.

Другой задачей, решаемой изобретением, является уменьшение площади цифровых схем типа CMOS с использованием комплиментарных MOSFET Device.

Эти задачи решены в конструкции интегральной транзисторной MOS структуры, содержащей на полупроводниковой подложке первого типа проводимости диэлектрический слой, на котором расположены истоковая и стоковая области первого типа проводимости, разделенные подзатворной областью второго типа проводимости, перекрытой областью подзатворного диэлектрика с расположенным на нем затвором.

Отличия предложенной интегральной транзисторной MOS структуры заключаются в том, что дополнительно содержит область второго типа проводимости, примыкающую к стоковой области и образующую эмиттер биполярного транзистора, базой которого служит упомянутая область стока, а коллектором - упомянутая подзатворная область.

Повышение быстродействия в предложенной интегральной транзисторной структуре достигается благодаря наличию в ней биполярного транзистора, а экономия площади - за счет совмещения его областей базы и коллектора соответственно со стоком и подзатворной областью.

Изобретение поясняется приведенными чертежами

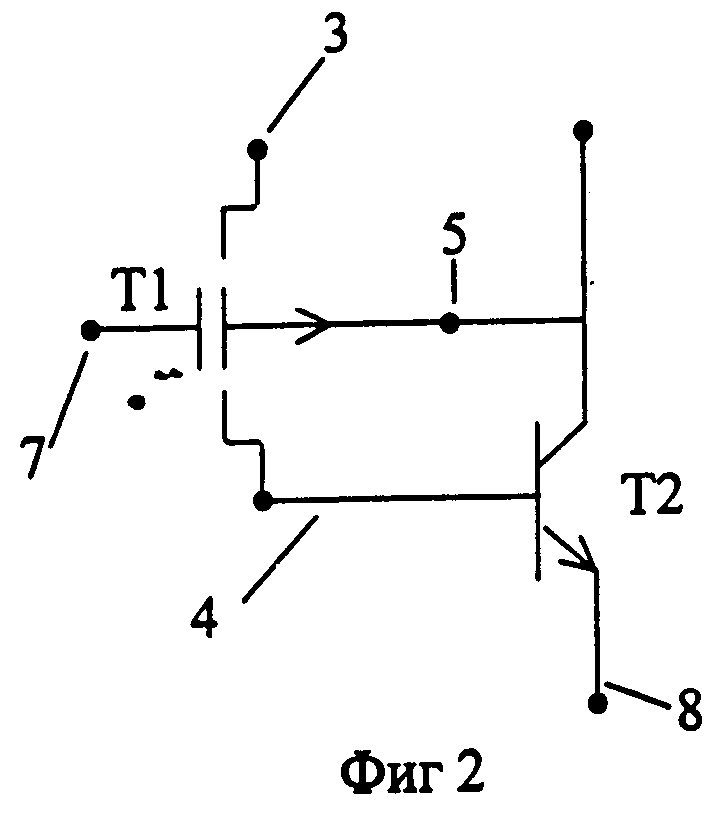

На фиг.1 приведен разрез интегральной транзисторной MOS структуры согласно изобретению.

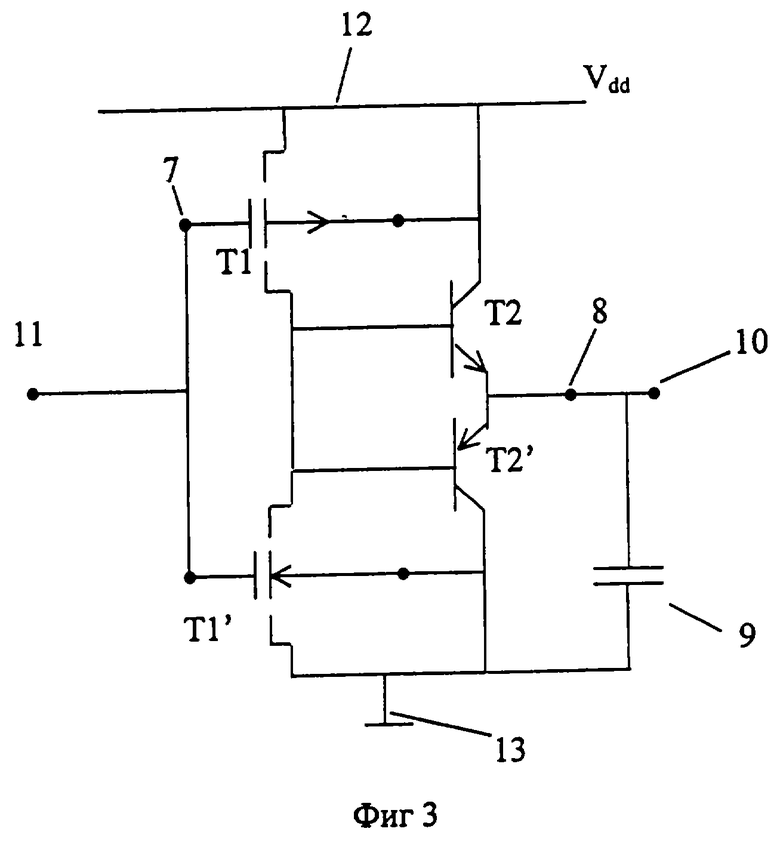

На фиг.2 приведена электрическая эквивалентная схема интегральной транзисторной MOS структуры согласно изобретению.

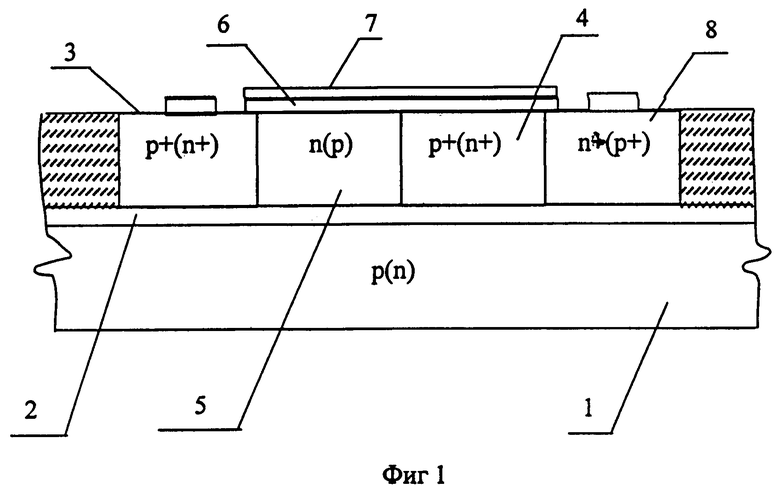

На фиг.3 приведена электрическая схема логического элемента типа BiCMOS с использованием изобретения.

Интегральная транзисторная МOS структура содержит на полупроводниковой подложке 1 первого типа проводимости диэлектрический слой 2, на котором расположены область истока 3 первого типа проводимости MOS транзистора Т1, разделенные подзатворной областью 5 второго типа проводимости, перекрытой областью 6 подзатворного диэлектрика, с расположенным на ней затвором 7, дополнительная область 8 второго типа проводимости, примыкающая к стоковой области 4 и образующая эмиттер биполярного транзистора Т2, базой которого служит область стока 4, а коллектором - подзатворная область 5.

Интегральные транзисторные MOS структуры согласно изобретению могут быть использованы для построения логического элемента ВiCMOS, электрическая схема которого приведена на фиг.3. При этом первая структура, электрическая схема которой приведена на фиг. 2, образует цепь заряда разгрузочной емкости 9 логического элемента BiCMOS типа, подключенной к его выходу 10. Эта структура подключена областями 3 и 5 к шине питания 12, а затвором 7 ко входу 11. Вторая транзисторная MOS структура, согласно изобретению, затвором n-канального MOS транзистора Т2 подключена ко входу 11 логического элемента, эмиттером биполярного р-n-р транзистора Т2' к выходу 10, а истоком - к общей шине 13 и образует цепь разряда нагрузочной емкости 9.

Интегральные транзисторные MOS структуры согласно изобретению работают следующим образом. При наличии на входе 11 напряжения равного напряжению общей шины (т.е. напряжения, равного нулю), транзистор Т1' закрыт, а транзистор Т1 открыт. При этом ток от шины питания 12, через открытый транзистор Т1 втекает в базу 4 транзистора Т2 и открывает его, начинает протекать ток от шины питания 12, который заряжает нагрузочную емкость 9. Заряд нагрузочной емкости при этом происходит сравнительно большим током, превышающим ток, протекающий через транзистор Т1 более чем в десять раз, что обуславливает меньшее время задержки переключения по сравнению с классической CMOS схемой. Когда напряжение на входе 11 увеличивается до величины, превышающей пороговое напряжение n-канального MOS транзистора Т1', открывается транзистор Т1' и закрывается транзистор Т1. Через открытый транзистор Т1' на базу транзистора Т2' передается потенциал общей шины 13. Транзистор Т2' открывается и происходит разряд нагрузочной емкости 9. При этом ток разряда, протекающий через биполярный транзистор Т2', значительно превышает ток, коммутируемый MOS транзистором Т1', что обуславливает меньшую величину задержки переключения логического элемента.

Интегральная транзисторная MOS структура может найти широкое применение при построении VLSI логических и запоминающих устройств благодаря ее высокому быстродействию в сочетании с высокой плотностью компановки, обусловленной совмещением рабочих областей полевого и биполярного транзисторов. Для изготовления интегральной структуры согласно изобретению не требуется каких-либо дополнительных технологических операций, она может быть изготовлена, например, по технологии типа SIO CMOS.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА ПАМЯТИ ДИНАМИЧЕСКОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2001 |

|

RU2216795C2 |

| МОП ДИОДНАЯ ЯЧЕЙКА МОНОЛИТНОГО ДЕТЕКТОРА ИЗЛУЧЕНИЙ | 2011 |

|

RU2494497C2 |

| ФУНКЦИОНАЛЬНО-ИНТЕГРИРОВАННАЯ ЯЧЕЙКА ФОТОЧУВСТВИТЕЛЬНОЙ МАТРИЦЫ | 2012 |

|

RU2517917C2 |

| ИНТЕГРАЛЬНАЯ СХЕМА СИЛОВОГО БИПОЛЯРНО-ПОЛЕВОГО ТРАНЗИСТОРА | 2015 |

|

RU2585880C1 |

| БиКМОП-ПРИБОР И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2003 |

|

RU2282268C2 |

| БИКМОП-ПРИБОР И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 1996 |

|

RU2106719C1 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ С УПРАВЛЯЕМЫМ ПОТЕНЦИАЛОМ ПОДЗАТВОРНОЙ ОБЛАСТИ | 2011 |

|

RU2465659C1 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ И СПОСОБ ЕЕ ПРОГРАММИРОВАНИЯ | 2009 |

|

RU2481653C2 |

| ДИНАМИЧЕСКОЕ ПОСЛЕДОВАТЕЛЬНОЕ ФУНКЦИОНАЛЬНОЕ УСТРОЙСТВО | 2005 |

|

RU2392672C2 |

| ЕМКОСТНАЯ МОП ДИОДНАЯ ЯЧЕЙКА ФОТОПРИЕМНИКА-ДЕТЕКТОРА ИЗЛУЧЕНИЙ | 2014 |

|

RU2583955C1 |

Использование: микроэлектроника. Сущность изобретения: интегральная транзисторная MOS структура содержит на полупроводниковой подложке первого типа проводимости диэлектрический слой, на котором расположены истоковые и стоковые области первого типа проводимости, разделенные подзатворной областью второго типа проводимости, перекрытой областью подзатворного диэлектрика с расположенным на нем затвором, и дополнительно введенную область второго типа проподимости, примыкающую к стоковой области и образующую эмиттер биполярного транзистора, базой которого служит упомянутая область стока, а коллектором - упомянутая подзатворная область. Техническим результатом изобретения является увеличение быстродействия и уменьшение площади интегральных транзисторных MOS структур. 3 ил.

Интегральная транзисторная MOS структура, содержащая на полупроводниковой подложке первого типа проводимости диэлектрический слой, на котором расположены истоковая и стоковая области первого типа проводимости, разделенные подзатворной областью второго типа проводимости, перекрытой областью подзатворного диэлектрика с расположенным на нем затвором, отличающаяся тем, что дополнительно содержит область второго типа проводимости, примыкающую к стоковой области и образующую эмиттер биполярного транзистора, базой которого служит упомянутая область стока, а коллектором - упомянутая подзатворная область.

| Chenming Hu | |||

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| Nanotechnology, 10(1999), 113-116 | |||

| СЕСОЮЗНАЯ МТЕНТНО-ТЕХКГГКДЯ!БИБЛИО-1^ИЛ5МЕШАЛКА | 0 |

|

SU251682A1 |

| US 4149176 А, 10.04.1979 | |||

| БИПОЛЯРНЫЙ ТРАНЗИСТОР С ИЗОЛИРОВАННЫМ ДИЭЛЕКТРИКОМ ЗАТВОРОМ | 1992 |

|

RU2065642C1 |

Авторы

Даты

2003-06-27—Публикация

2001-10-11—Подача