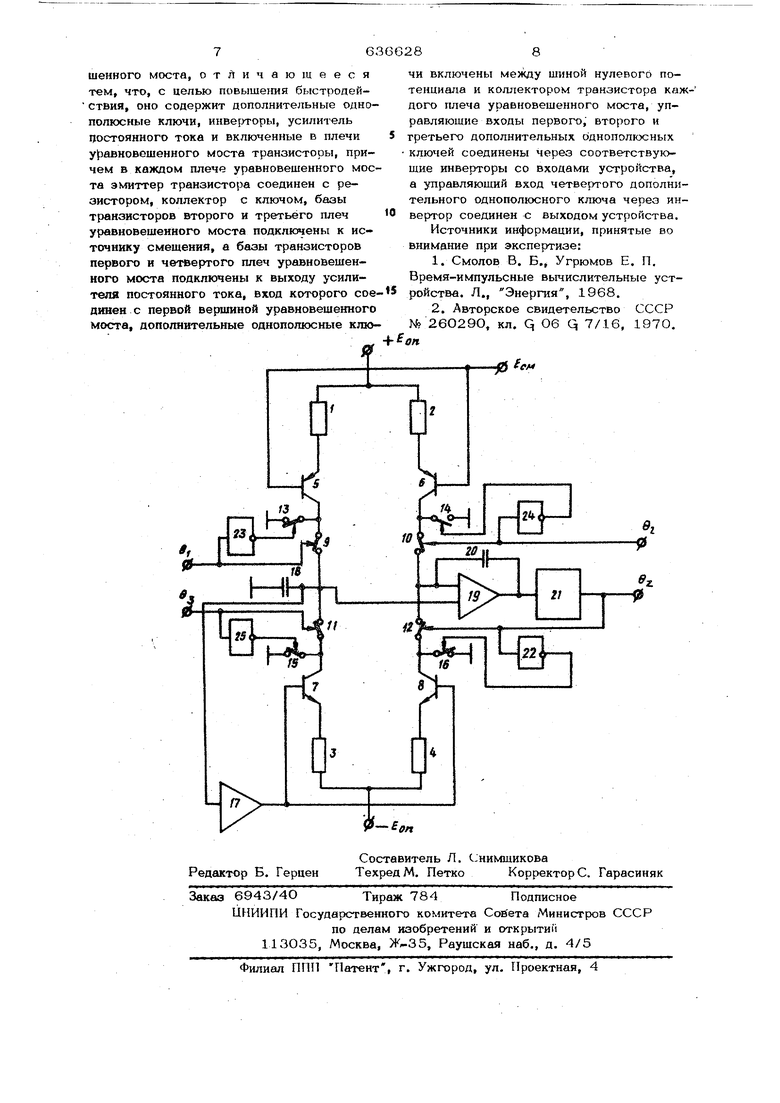

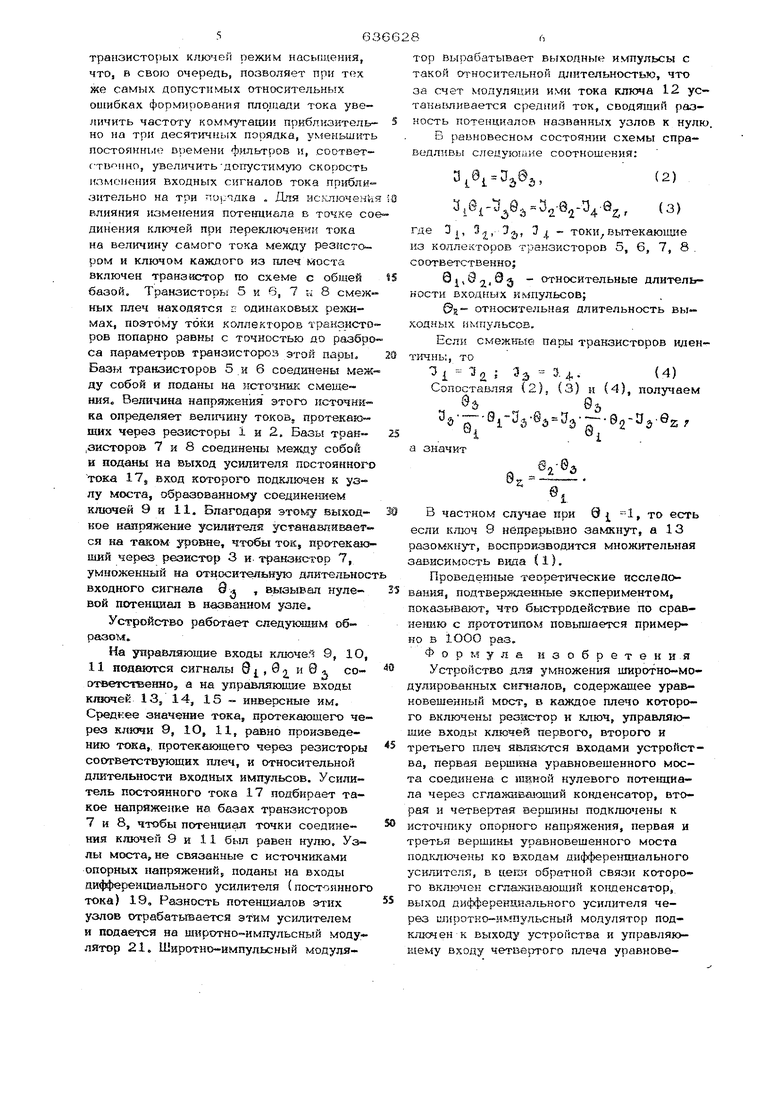

Недостатком этого устройства является малое быстродействие, связанное с йеобкодимостью фильтрации импульсных потоков при относительно небольшой частоте коммутации ключей, Целью предлагаемого изобретения является повышение быстродействия. Поставленная цель достигается тем, что устройство содержит дополнительные однополюсные ключи, инверторы, усилитель постоянного тока и включенные в пл чи уравновешенного моста транзисторы, причем в каждом плече уравновешенного моста эмиттер транзистора соединен с реэистором, коллектор с ключом, базы TpOHaiKyropOB второго и третьего плеч уравновешенного моста подключены к источнику смешения, а базы транзисторов . пв{шого и четвертого плеч уравновешенно го мос-ш яодключены к выкоду усилителя постоянйого тока, вход которого соеди нее с первой вершиной уравновешенного моста( дополнительные однополюсные клю чи включены между шиной нулевого потешшапа г коллектором транзистора кажSLoro ппеча уравновешенного цоста, управлшопше входы первого, второго и треть его дополнительных однополюсных ктоочей Соешгаены через соответствующие инверTOfHM со входами устройства, а управладЬ ашй вход четвертого дополнительного однополюсного ключа через инвертор соединен с выходом устройства. Сущность изобретения состоит в использовании в качестве коммутирукшшх элементов ненасьш1енных транзисторных кшочей, работающих в режиме переключения токов. Отсутствие рехшма насыШ1ения ноэволяет при тек же самых допустимых ошибках формирования плошади тока увеличить частоту коммутации приблизительно на три порядка, что, в свою очередь, позволяет уменьшить емкости сглаживающих конденсаторов и уве личить скорости изменения входных сигналов тоже приблизительно на три порядка. На чертеже изображена принципиальная схема устройства. Устройство состоит из уравновещенно го моста, все плечи которого содержат последовательно включенные резисторы 1, 2, 3, 4 (соответственно для четырех плеч моста), транзисторы 5, 6, 7, 8 (соответственно для четырех плеч моста и ключи 9, Ю, 11, 12 (соответственно для четырех плеч моста). Эмиттерные вы воды транзисторов 5, 6, 7, 8 соединяют ся с резисторами 1, 2, 3, 4 соответственно. Вторые выводы резисторов I и 2 подключены к источнику опорного напряжения (положительного), а вторые выводы резисторов 3 и 4 - к источнику опорного напряжения-Еоп (отрицательного). Коллекторные выводы транзисторов 5, 6, 7, 8 соединены с первыми выходами ключей 9, 1О, 11, 12 соответственно. Второй выход ключа 9 соединен с вторым выходом ключа 1 1, второй ключа 10 соединен с вторым выходом ключа 12. Однополюсные ключи 13, 14j 15, 16 первым выходом подключаются к общей точке схемы, а вторым - к коллекторам транзисторов 5, 6, 7, 8 соответственно. Базовые выводы транзисторов 5 и 6 подключаются к источнику смещенияЕрЛ14,а базовые выводы транзисторов 7 и 8 подключаются к выходу усигштеля постоянного тока 17. Вход этого усилителя подключен к точке соединения ключей 8 и 11. К этой же точке подключен сглаживающий конденсатор 18, второй выход которого соединен с общей точкой схемы, и неинверсирующий вход дифференанального (операционного) усилителя 19. К точке соединения ключей 10 и 12 подклк ен инвертирующий вход усилителя 19 и сглаживающий конденсатор 20, второй выход которого соединен с выходом усилителя 19. Выход усилителя 19 соединен с входом широтно-импульсного модулятора 21, выход которого является выходом всей схемы в целом, а также подается на управляющий вход ключа 12 и через инвертор 22 на управляющий вход ключа 16. Входной сигнал Q подается на управляккций вход ключа 9 и через инвертор 23 на управляющий вход ключа 13 Входной сигнал 0 у. подается на управляющий вход ключа 1О и через инвертор 24 ка управляющий вход ключа 14. Входной сигнал в подается на управляющий вход ключа 11 и через инвертор 25 на управляющий вход ключа 15. Принцип повышения быстродействия устройства состоит в следующем. Введение в каждое плечо моста допол нительного ключа 13, 14 15, 16 (соответственно для каждого кз четырех плеч моста), второй выход которого подключен к общей точке схемы, позволило при одновременном использовании ключей 9, 10, 11, 12 (соответственно для каждого из плеч моста) осуществить принцип переключения токов. Применение этого принципа позволяет не использовать при работе

транзисторых ключей реуким насыщения, что, в свою очередь, позволяет при тех же самых допусткмь х относительных оишбках формирования тока увеличить частоту коммутации приблизительно на три десятичных порядка, уменьшить постоянные времени фильтров н, соответfTBi HHo, увеличитьдопустимую скорость ппмоиения входных сигналов тока приблизительно на три , Для исключенй влияния изменения потенциала в точке содинения ключей при переключении тока на величину самого тока меиду резг1сто. ром и ключом каждого из плеч моста включен транзистор по схеме с общей базой. Транзисторы 5 и 6, 7 к 8 смежных плеч находятся с одинаковых режимах, поэтому токи коллекторов транзисторов попарно равны с точностью до разбро са параметров транзисторСЗ этой парьь Базы транзисторов 5 и 6 соедшюны между собой и поданы на источник смеще кия. Величина напряжения этого источника определяет величину . протекающих через резисторы 1 и 2, Базы тран- ,зиоторо 7 и 8 соединены между собой и поданы на выход усилителя постоянного тока 17j вход которого подключен к узлу моста, образованному соединением ключей 9 и 11. Благодаря этокдг выходное напряжение усилителя устанавяиваег- ся ка таком уровне, чтобы ток, протекающий через резистор 3 и- транзкс-тор 7, умноженный на отнсюительную длительнос входного сигнала О , выаьшал нулевой потенциал в названном узле.

Устройство работает следующим образом

На уиравляющие входы ключел 9, 1О, 11 подаются сигналь 9 , 9 2. ® Л ° ответственно, а на управляющие входы кгаочеЕ 13, 14, 15 инверсные им. Среднее значение тока, протекающего через ключи 9, 1О, 11, равно произведению тока,, протекающего через резисторы соответствующих плеч, и относительной длительности входных импульсов. Усилитель постоянного тока 17 подбирает такое напряженке на базах транзисторов 7 и 8, чтобы потенциал точки соединения ключей 9 и 11 был равен нулю. Узлы мсх:та, не связанные с источн1псами опорных напряжений поданы на входы дифференциального усилителя (постоянного тока) 19, Разность потенциалов этих

узлов отрабатывается эТим усилителем и подается на широтно-импульсньш модулятор 21. Широтно-импульсный модулятор вырабатывает выходные импульсы с такой от-носительной длительностью, что за счет К1одуля1ши тока ключа 12 устана1У1нвается средний ток, сводящий разность потенциалов названных узлов к нулю.

В равновесном состоянии схемы справедливы следующие соотношения:

- т А

з,в

(2)

3iSrVs 2M4-9z. (3)

i -f- токи, вытекаю1Щ1е

где из коллекторов транзисторов 5, 6, 7, 8 . соответственно;

.Э относительные длительности входных импульсов;

©j- относительная длительность выходных импульсов.

Если смежньш пары транзисторов нде тичны, то

(4)

i

3

3

Сопоставляя (2), (З) и (4), получаем 5 ... .QS

Эй. 3

7

0

Q:

значит

в частном случае при 9 j -1, то есть если ключ 9 непрерывно замкнут, а 13 разомкнут, воспроизводится множителышя зависимость вида 11).

Проведенные теоретические исследования, подтвержденные экспериментом, показывают, что быстродействие по сравнеш1Ю с прототипом повьплается примерно в 1ООО раз.

Формула изобретения Устройство длз умножения широтно-модулированных сипшлов, содержашее уравновешенный мост, в каждое плечо которого включены резистор и ключ, управляющие входы ключей первого, второго и третьего плеч являготся входами устройства, первая верш1ша уравновешенного моста соединена с ШЕКОЙ нулевого потенциала через сглажйвшоший конденсатор, вторая и четвертая вершины подключены к источнику опорного напряжения, первая и третья вершины уравновешенного моста под1шючены ко входам диффере1щиального усилителя, в цеш обратной связи которого включен сглаживающий конденсатор, выход дифференциального усилителя через шнротко-импульсный модулятор подключен к выходу устройства и управляющему входу четвертого плеча уравнове

| название | год | авторы | номер документа |

|---|---|---|---|

| Мостовое множительно-делительное устройство для широтно- модулированных величин | 1976 |

|

SU579627A1 |

| Устройство для нелинейного преобразования широтно-модулированных сигналов | 1977 |

|

SU636627A1 |

| Вычислительное устройство | 1977 |

|

SU690501A1 |

| Импульсный стабилизатор постоянногоНАпРяжЕНия | 1979 |

|

SU849170A1 |

| Время-импульсное множительно-делительное устройство | 1982 |

|

SU1032459A1 |

| Устройство для управления и защиты преобразователя напряжения | 1986 |

|

SU1339803A1 |

| Управляемый вентильный электродвигатель | 1987 |

|

SU1458961A1 |

| Управляемый вентильный электродвигатель | 1989 |

|

SU1700705A2 |

| Мостовое множительно-делительное устройство для широтно-модулированных величин | 1976 |

|

SU590761A1 |

| Устройство для управления и защиты преобразователя | 1988 |

|

SU1522345A2 |

Авторы

Даты

1978-12-05—Публикация

1976-05-17—Подача