Изобретение относится к области вычислительной техники, а именно, к электронным моделирующим устройствам, и звляется усовершенствованием известного Злстройства, описанного в авт. св. №422002.

В основном изобретении по авт.св. № 422ОО2 описано устройство для моделирования сетевых графиков, содержащее блок управления, первый выход которого подключен к первому входу первого элемента ИЛИ блока формирования топологии, блок моделей ветвей по числу работ сетевого графика, каждая из которых выполнена в виде эадатчйков адресов, выходами соединенных с элементами И, причем выход первого элемента И соединен с входом формиро-вателя временных интервалов, вход второго элемента И соединен через инвертор с первым входом элемента ИЛИ, к второму входу которого подключен выход второго элемента И, генератор импульсов, первый и второй выходы которого подключены соответственно ко второму входу первого элемента И каждой моде-

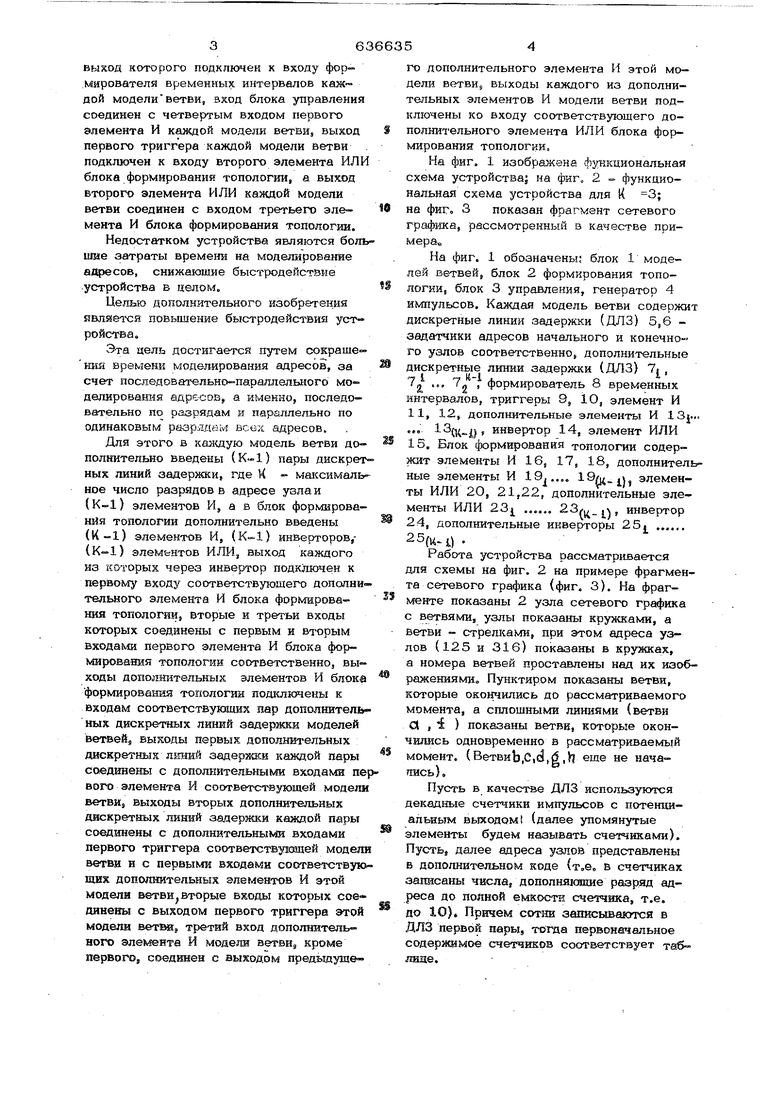

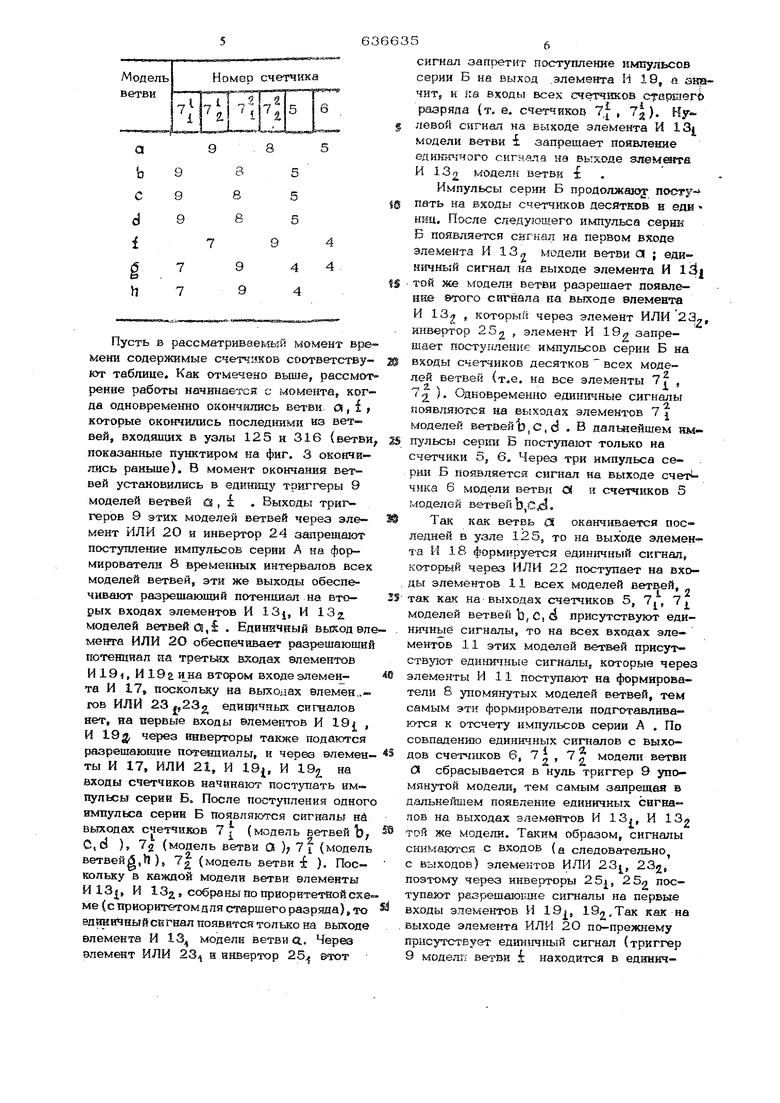

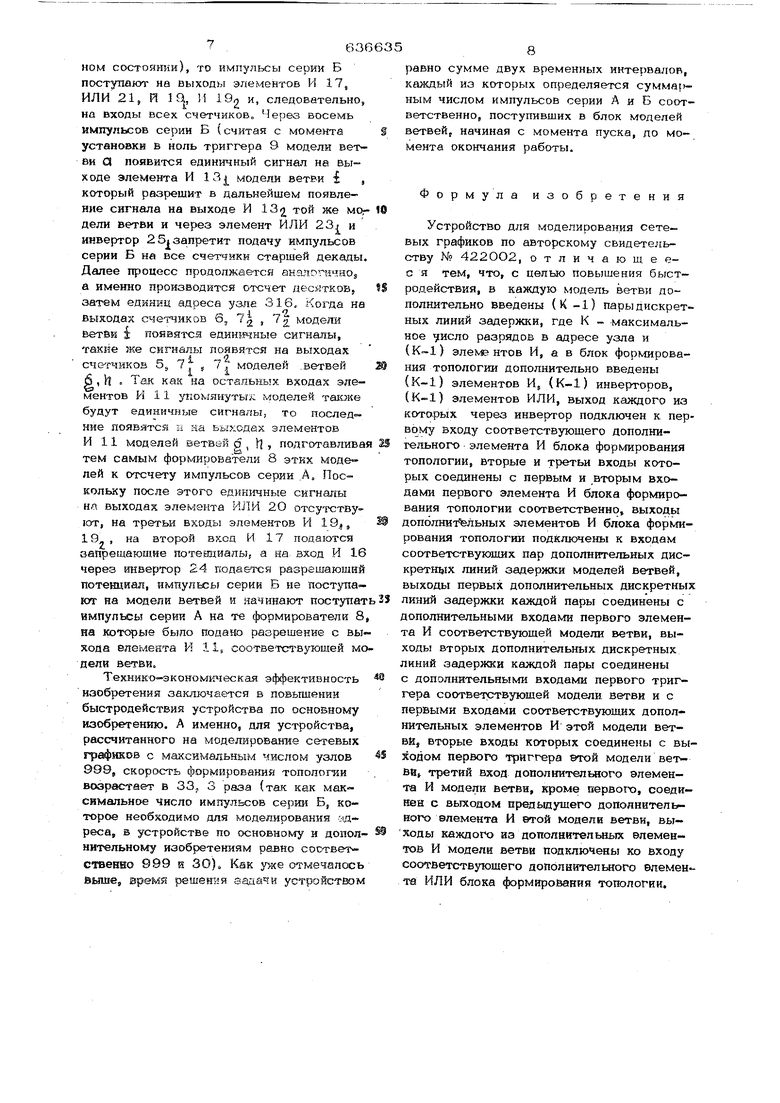

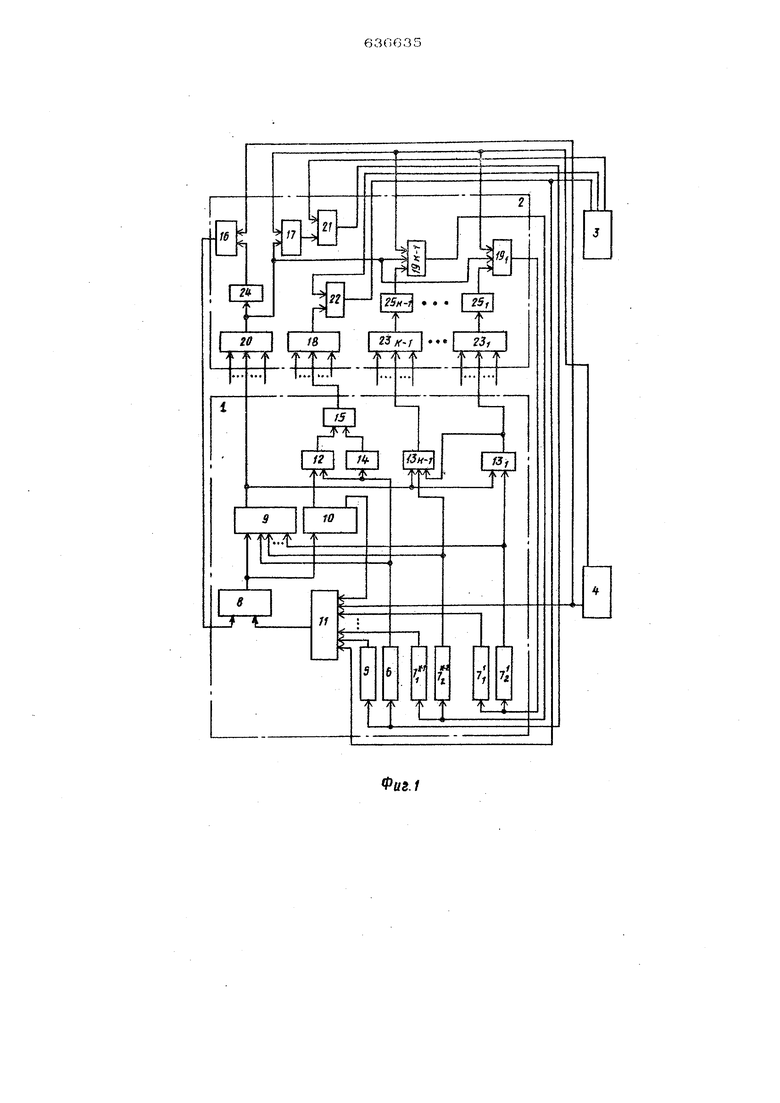

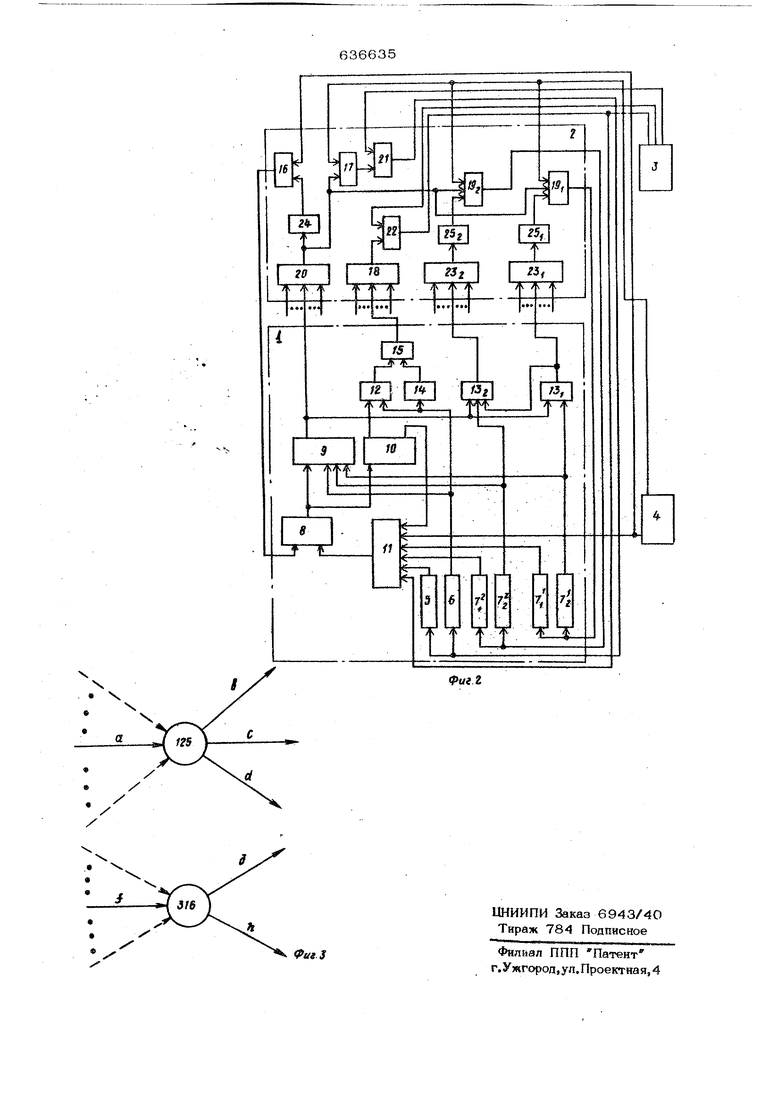

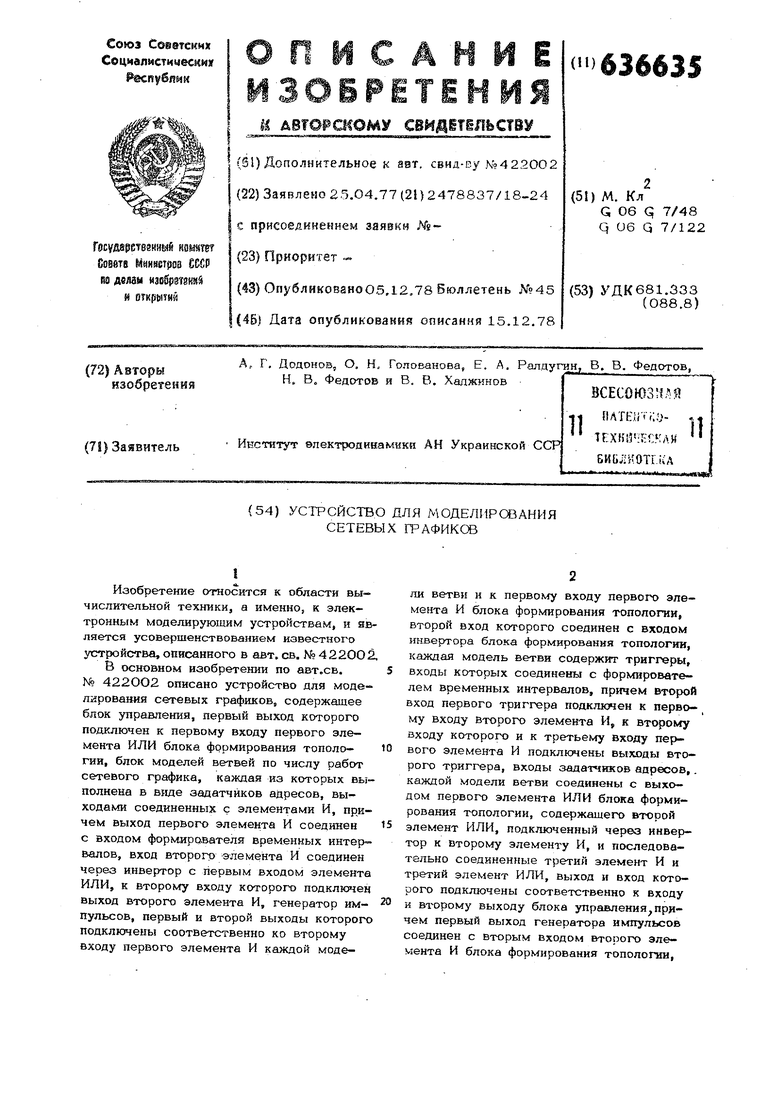

ЛИ ветви и к первому входу первого элемента И блока формирования топологии, второй вход которого соединен с входом инвертора блока формирования топологии, каждая модель ветви содержит триггеры, входы которых соединены с формирователем временных интервалов, причем второй вход первого триггера подключен к первому входу второго элемента И, к второму входу которого и к третьему входу первого элемента И подключены выходы второго триггера, входы задатчиков адресов, каждой модели ветви соединены с выходом первого элемента ИЛИ блока формирования топологии, содержащего второй элемент ИЛИ, подключенный через инвертор к второму элементу И, и последовательно соединенные третий элемент И и третий элемент ИЛИ, выход и вход которого подключены соответственно к входу и Bi-opoMy выходу блока управления причем первый выход генератора импульсов соединен с вторым входом второго элемента И блока формирования топологии. выход которого подключен к входу фор .мярователя временных интервалов каж™ дои моделиветви, вход блока управления соединен с четвертым входом первого элемента И каждой модели ветви, выход первого триггера каждой модели ветви подключен к входу второго элемента ИЛИ блока формирований топологии, а выход второго элемента ИЛИ кагвдой модели ветви соединен с входом третьего элемента И блока формирования топологии. Недостатком устройства являются боль шие затраты времени на моделирование адресов, снижающие быстродействие устройства в целом. Целью дополнительного изобретения являе1х:я повышение быстродействия устройства, Эта цель достигается путем сюкраше шш времени моделирования адресов, за счет последовательно-параллельного мо делировакия адресов, а именно, последо вательно по разрядам и параллельно по одинаковым раарлдвм всех адресов. Для этого в кшвдую модель ветви дополнительно введены (K-l) пары дискрет ных линий задержки, где К - максималь ное число разрядов в адресе узла и (К-1) элементов И, а в блок формирования топологии дополнительно введены (К-1) элементов И, () инверторов,() элементов ИЛИ, выход каждого из которых через инвертор подключен к nepsosvty входу соответствующего дополни тельного элемента И блока формирования ТОПОЛОГИИ, вторые и третьи входы которых соединены с первым и )pым входами первого элемента И блока формировааия топологии соответственно, выходы дополнительных элементов И блоки формирования топологии подключены к входам соответствующих пар дополнитель ных дискретных линий задержки моделей ветвейа выходы первых дополнительных дискретных Л1етий задержки каждой пары ссюдинены с дополнительными входами п вого элемента И соответствующей модел ветвИэ выкоиы вторых дополнительных дискретных линий за,аернски каждой пары соединены с дополнительными входами первого триггера соответствующей модел ветви и с первыми входами соответствую щих дополнительных элементов И этой модели ветви,вторые входы которых сое динены с выходом первого триггера этой модели ветШ, третий вход дополнитель ного элекданта И модели ветвНа кроме первого, соединен с выходом предьщуше64 го дополнительного элемента И этой мо дели ветвид выходы каждого из дополнительных элементов И модели ветви подключены ко входу соответствующего дополнительного элемента ИЛИ блока формирования топологии. На фиг. 1 изображена функциональная схема устройства; на фиг 2 - функциональная схема устройства для К 3; на фиг. 3 показан фрагмент сетевого графика, рассмотренный в качестве примераНа фиг. 1 обозначены; блок 1 моделей ветвей, блок 2 формирования топологии, блок 3 управления, генератор 4 импульсов. Каждая модель ветви содержит дискретные линии задержки (ДЛЗ) 5,6 задатчики адресов начального и конечного узлов соответственно, дополнительные дискретные линии задержки (ДЛЗ) 7i , 7 формирователь 8 временных 2. 2 интервалов, триггеры 9, Ю, элемент И 11, 12, дополнительные элементы И 13j... .,, 13(j/, инвертор 14, элемент ИЛИ 15. Блок формирования топологии содержит элементы И 16, 17, 18, дополнительные элементы И 19..,. i9{K-l)i элементы ИЛИ 20, 21,22, дополнительные элементы ИЛИ 23 (к.- О инвертор 24, дополнительные инверторы 25j ...... ) Работа устройства рассматривается для схемы на фиг. 2 на примере фрагмента сетевого графика (фиг. 3). На фрагменте показаны 2 узла сетевого графика с ветвями, узлы показаны кружками, а ветви - стрелками, при этом адреса узлов (125 и 316) показаны в кружках, а номера ветвей проставлены над их изображениями. Пунктиром показаны ветви, которые окончились до рассматриваемого момента, а сплошными линиями (ветви CS , ) показаны ветвк которые окончились одновременно в рассматриваемь й момент. (ВетвиЬ,С,(,Й,)1 еше не начались). Пусть в качестве ДЛЗ используются декадные счетчики импульсов с потенциальным выходом (далее упомянутые элементы будем называть счетчиками). Пусть, далее адреса узлов представлены Б дополнительном коде (тоЭ, в счетчиках записаны числа, дополняющие разряд адреса до полной ewKocTJi счетчика, т.е. до 10). Причем сотни записываются в ДЛЗ первой пары, тогда первоначальное содержимое счетчЕгков ссютветствует таблнде. Пусть в рассматриваемый момент вре мени содержимые счетчиков соответствуют таблице. Как отмечено выше, рассмот рение работы начинается с момента, когда одновремеггао око1г-1йлись ветви, сд, i , которые окончились последними из ветвей, входящих в уэлы 125 н 316 (ветви показанные пунктиром на фиг. 3 окончились раньше), В момент окончания ветвей установились в единицу триггеры 9 моделей ветвей s , i . Выходы триг геров 9 этих моделей ветвей через элемент ИЛИ 2О и инвертор 24 запрещают поступление импульсов серии А на формирователи 8 временных интервалов всех моделей ветвей, эти же выходы обеспечивают разрешающий потенциал на вторых входах элементов И 13 j, И iS. моделей ветвей CS, . Единичный выход вп мента ИЛИ 2О обеспечивает разрешающий потенциал на третьих входах элементов И 19 i, И 19г нка BTqjOM входе элемента И 17, поскольку на выходах элемен..гов ИЛИ единичных сигналов нет, на первые входы элементов И 19, И 19g, через инверторы также подаются разрешаюшие потенциалы, и чер«з влемен ты И 17, ИЛИ 21, И 19j, И 192. « входы счетчиков начинают поступать импульсы серии Б, После поступления одног импульса серии Б появляются сигналы ни выходах счетчиков 7 (модель ветвей Ь, С, d ), 7g (модель ветви О ) 7 j (модель ветвейg,t), 7 (модель ветви i ). Поскольку в каждой модели ветви элементы И 13|, И IS. собраны по приор йтетной схе ме (с приоритетомдпя старшего разряда), то вданичныйсЕГнал появится только на выходе элемента И 13 модели ветви о.. Через элемент ИЛИ 23 и игшертор 25 &тот сигнал запретит поступление имкульсов серии Б на выход .элемента И 19, о значит, к ка входы всех счетчнков старшегЬ разряда (т. а. счетчиков 7 , 7|). Нулевой сигнал на выходе элемента И 13 модели ветви запрещает появление едиккччого сигнала на выходе злемагге И 132 модели ветви i Импульсы серии Б продолжаиу посту- петь на входы счетчиков десятков н еди« ниц. После следующего импульса серии Б появляется сигнал на первом входе элемента И 13 модели ветви d ; единичный сигнал на выходе элемента И той же модели ветви разрещает появление 8ТОГО сигнала па выходе элемента И 13,j , который через элемент ИЛИ 232 инвертор 252 элемент И 192 запрещает поступление импульсов серии Б на входы счетчиков десятков всех моде- /2 лей ветвей (т.е. на все элементы 7, , г i 2 идновременно единичные сигналы -ПОЯВЛЯЮТСЯ на выходах элементов 7 моделей вel0eйЪ, . В дальнейщем m,iпульсы cepini Б поступают только на счетчики 5, 6. Через три импульса се- . рш1 Б появляется сигнал на выходе счет чика 6 модели ветви Ct н счетчнков 5 моделей ветвей Ь,С. Так как ветвь CS оканч1юается последней в узле 125, то на выходе элемента И 18 форМ1 руется единичный сигнал который через ИЛИ 22 поступает на входы элементов 11 всех моделей ветвей, так как на выходах счетчиков 5, 7j, 7 моделей ветвей Ь, С, d присутствуют единичные сигналы, то на всех входах эле- мен-тов 11 этих моделей ветвей присутствуют единичные сигналы, которые через элементы И 11 поступают на формирователи 6 упомянутых моделей ветвей, тем самым эти формирователи подготавливаю-тся к отсчету импульсов серии А . По совпадению единичных сигналов с выходов счетчиков 6, 7 i , 7 модели ветви (3 сбрасывается в нуль триггер 9 упомянутой модели, тем самым запрещая в дальнейшем появление единичных сигналов на выходах элементов И 13., И 132 той же модели. Таким образом, сигналы снимаются с входов (а следовательно, с выходов) элементов ИЛИ 23, 232, поэтому через инверторы 25, 252 тупахуг разрешающие сигналы на первые входы элементов И 19ji, 192,Так выходе элемента ИЛИ 2О по-прежнему присутствует единичный сигнаш (триггер 9 модели ветвй i находится в единнч 7636ном состоянии), то импульсы серии Б поступают на выходы элементов И 17, ИЛИ 21, и 1Q, 11 iOrt и, следовательно, HQ ВХОДЫ всех счетчиков, Череа восемь импульсов серии Б (считая с момента установки в ноль триггера 9 модели ветви а появится единичный сигнал на выходе элемента И 13 модели ветви , который разрешит в дальнейшем появление сигнала на выходе И 13 той же мог дели ветви и через элемент ИЛИ 23 и инвертор 25jзапретит подачу импульсов серии Б на все счетчики старшей декады. Далее процесс продолжается аналогичное а именно производится отсчет десятков, затем единиц адреса узле 316. Когда на г.f- выходах счетчиков о, 2 2 модели ветби i ггоЕвятся единичные сигнапы, такие 1ке сигналы появятся на выходах счетчиков 5, t s 7 д моделей .ветвей 6,Н . TaJt как на остальных входах элементов И 11 укоыянутык моделей также будут единичные сигналы, то послед, ние появятся п на ьыходах элементов И 11 моделей ветвей , tl , подготавлива тем самым формирователи 8 этих моде лей к отсчету импульсов серии А, Поскольку после этого единичные сигналы нп выходах элемента ИЛИ 20 отсутствуют, на третьи входы элементов И 19, 19- , на второй вход И 17 подаются запрещающие потенниалы, а на вход И 16 через инвертор 24 подается разрешающий потенциал, импупьсь) серии Б не поступают на модели ветвей и начинают поступат импульсы серий А на те формирователи 8 на которые было подано разрешение с вы хопа елеглеата И 11s соответствующей мо дели ветви. Технико-экономическая эффективность изобретения заключается в повышении быстродействия устройства по основному изобретению, А именно, для устройства, рассчитанного на моделирование сетевых графиков с максимальным числом узлов 999, скорость формирований топологам возрастает в 33,, 3 раза (так как максимальное Число импульсов серии Б, которое необходимо для моделирования -идраса, в устройстве по основному и дополнительному изобретениям равно соответ ственно 999 и 30). Как уже отмечалось выше, время решеная задачи устройством равно сумме двух временных интервалов, каждый из которых определяется сумма(ным числом импульсов серии А и Б соответственно, поступивших в блок моделей ветвей, начиная с момента пуска, до момента окончания работы. Формула изобретения Устройство для моделирования сетевых графиков по авторскому свидетельству № 422ОО2, отличающеес я тем, что, с целью повышения быстродействия, в каждую модель ветви дополнительно введены (К-1) пары дискретных линий задержки, где К - максимальное исло разрядов в адресе узла и () нтов И, а в блок формирования топологии дополнительно введены (К-1) элементов И, (К-1) инверторов, (К-1) элементов ИЛИ, выход каждого из которых через инвертор подключен к первому входу соответствующего дополнигельного элемента И блока формирования топологии, вторые и третьи входы которых соединены с первым и вторым входами первого элемента И блока формирования топологии соответственно, выходь дополнительных элементов И блока формирования топологии подключены к входам соответствующих пар дополнительных дискретш 1х линий задержки моделей ветвей, выходы первых дополнительных дискретных линий задержки каждой пары соединены с дополнительными входами первого элемента И соответствующей модели ветви, выходы вторых дополнительных дискретных линий задержки каждой пары соединены с дополнительными входами первого триггера соответствующей модели ветви и с первыми входами соответствующих дополнительных элементов И этой модели ветви, вторые входы которых соединены с выходом первого триггера етой модели ветBUf третий вход дополнительного элемента И модели ветви, кроме первого, соединен с выходом преяьщушего дополнительгйого элемента И етой модели ветви, выходы каждого из дополнительных элементов И модели ветви подключены ко входу соответствующего дополнительного елемента ИЛИ блока формирования топологии.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования сетевого графика | 1975 |

|

SU608169A1 |

| Устройство для моделирования сетевых графиков | 1976 |

|

SU636634A2 |

| Устройство для моделирования сетей с отрицательными данными | 1975 |

|

SU534765A1 |

| Устройство для исследования сетей | 1971 |

|

SU486330A1 |

| Устройство для моделирования сетевых графиков | 1983 |

|

SU1128272A2 |

| Устройство для моделированияСЕТЕВОгО гРАфиКА | 1980 |

|

SU849232A2 |

| Устройство для моделирования сетевых графиков | 1983 |

|

SU1119024A1 |

| Устройство для вычисления текущих ресурсов | 1978 |

|

SU746589A1 |

| Вычислительное устройство для решения задач сетевого планирования | 1978 |

|

SU750503A1 |

| Устройство для моделирования сетевых графиков | 1976 |

|

SU556460A2 |

Авторы

Даты

1978-12-05—Публикация

1977-04-25—Подача