элемента И, вход счетчика является вторым входом формирователя управляющих импульсов, а в каждую модель вет.ви введен счетчик, в блок формирования топологии введен второй элемент НЕ, выход которого подключен к второму входу третьего элемента И, третий вход которого соелинен с выходом первого элемента ИЛИ блока формирования топологии, выходы генератора импульсов подключены к входам второго элемента ИЛИ блока формирования топологии, выход которого соединен с входом второго элемента НЕ, выход первого элемента И блока формирования топологии подключен к входу счетчика блока формирования топологи выход первого элемента И модели ветви соединен с входом счетчика модели ветви, выход которого подключен к второму входу третьего элемента И и к первому входу второго элемента И, второй вход которого соединен с выходом элемента НЕ модели ветви, выход третьего элемента И

024

модели ветви подключен к второму входу формирователя временных интервалов, выход второго триггера модели ветви соединен с соответствующим входом записи сдвигового регистра блока формирования топологии, выход третьего элемента И блока формирования топологии подключен к нулевому входу триггера, к входу управления записью сдвигового регистра блока формирования топологии, к второму входу второго триггера модели ветви, выход сдвигового регистра блока формирования топологии соединён с вторым входом элемента И формирователя управляющих импульсов, являющимся первым входом формирователя управляющих импульсов, вход счетчика формирователя управляющих импульсов соединен с выходом первого элемента И блока формирования топологии,, выход второго элемента И блока формирования; топологии подключен к входу .счетчика импульсов .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования сетевых графиков | 1983 |

|

SU1128272A2 |

| Устройство для моделирования сетевых графиков | 1976 |

|

SU556460A2 |

| Устройство для моделирования сетевого графика | 1985 |

|

SU1374252A1 |

| Модель ветви графа | 1981 |

|

SU1012268A2 |

| Устройство для моделирования экстремальных путей на графе | 1983 |

|

SU1129617A1 |

| Устройство для моделирования сетевых графиков | 1985 |

|

SU1300481A2 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1986 |

|

SU1374239A2 |

| Устройство для моделирования сетевых графиков | 1977 |

|

SU708367A1 |

| Устройство для моделирования кратчайших путей на графах | 1982 |

|

SU1051543A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1983 |

|

SU1161951A1 |

УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СЕТЕВЫХ ГРАФИКОВ, содержащее генератор импульсов, формирователь управляющих импульсов, блок моделей ветвей, блок формирования топологии, включающий счетчик, сдвиговый регистр, триггер, элементы И, элементы ИЛИ, первый элемент НЕ, причем выход первого элемента ИЛИ соединен с первым входом первого элемента И и череэ первый элемент НЕ - с первым входом второго элемента И, вторые входы первого и второго элементов И соединены соответственно с первым и вторым выходами генератора импульсов, вход счетчика подключен к сдвиговому входу сдвигового регистра, выход счетчика соединен с единичным входом триггера, единичный и нулевой выходы которого подключены соответственно к первым входам третьего элемента И и первого элемента ИЛИ, каждая модель ветви включает триггеры, формирователь временных интервалов, элементы И, элемент НЕ и задатчики адресов начального и конечного узлов, входы которых объединены и соединены с входом счетчика блока формирования топологии,, в каждой модели ветви выход первого триггера подключен к первому входу первого элемента И, второй и третий входы которого соединены соответственно с выходом задатчика адреса начального узла и с первым входом формирователя управляющих импульсов, выход формирователя временных интервалов модели ветви подключен к первым входам первого и второго триггеров, второй вход первого триггера соединен с выходом второго элемента И модели ветви, выход задатчика адреса конечного узла подключен к входу элемента НЕ и к первому входу третьего элемента И модели ветви, выход второго элемента И блока формирования топологии соединен с первым входом формирователя временных интервалов модели ветви, выход второго триггера модели ветви подключен к соответствующему входу первого элемента ИЖ блока формирования топалогии, отличающееся тем, что, с целью расширения функциональных возможностей за счет моделирования альтерна тивных и мажоритарных сетей, в него введен счетчик импульсов, кроме того, формирователь управляющих импульсов содержит счетчик и элемент И, выход которого является выходом формирователя управляющих импульсов, выход счетчика подключен к первому входу

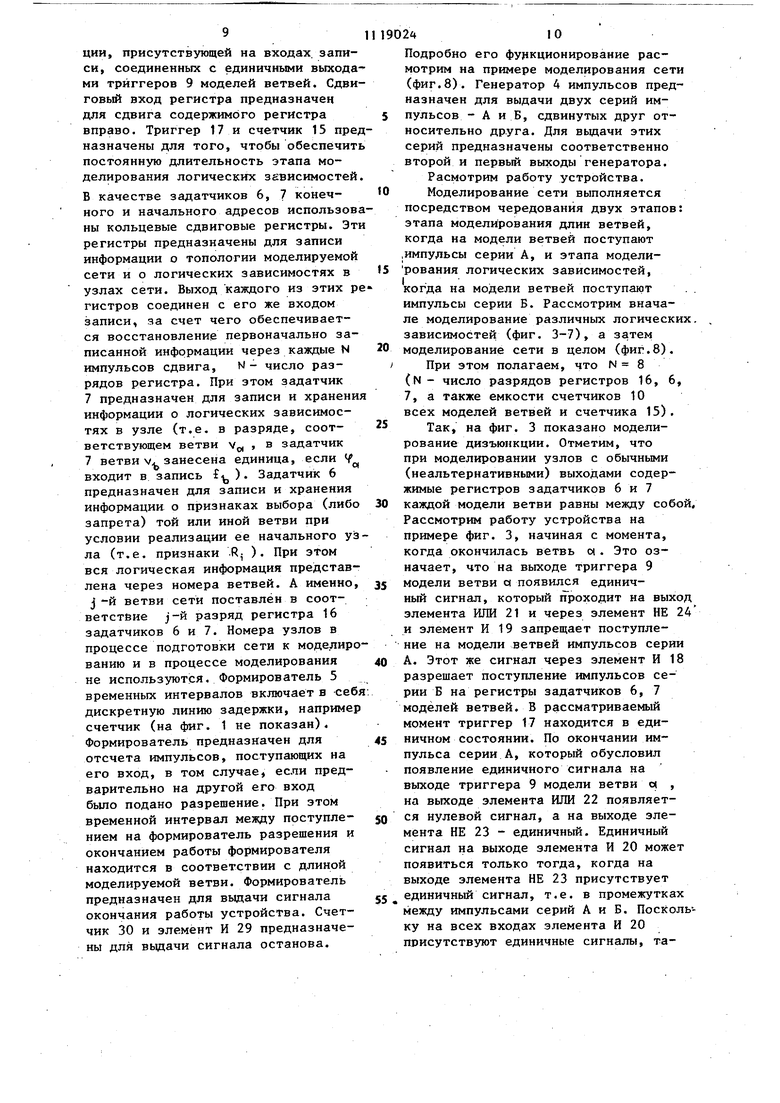

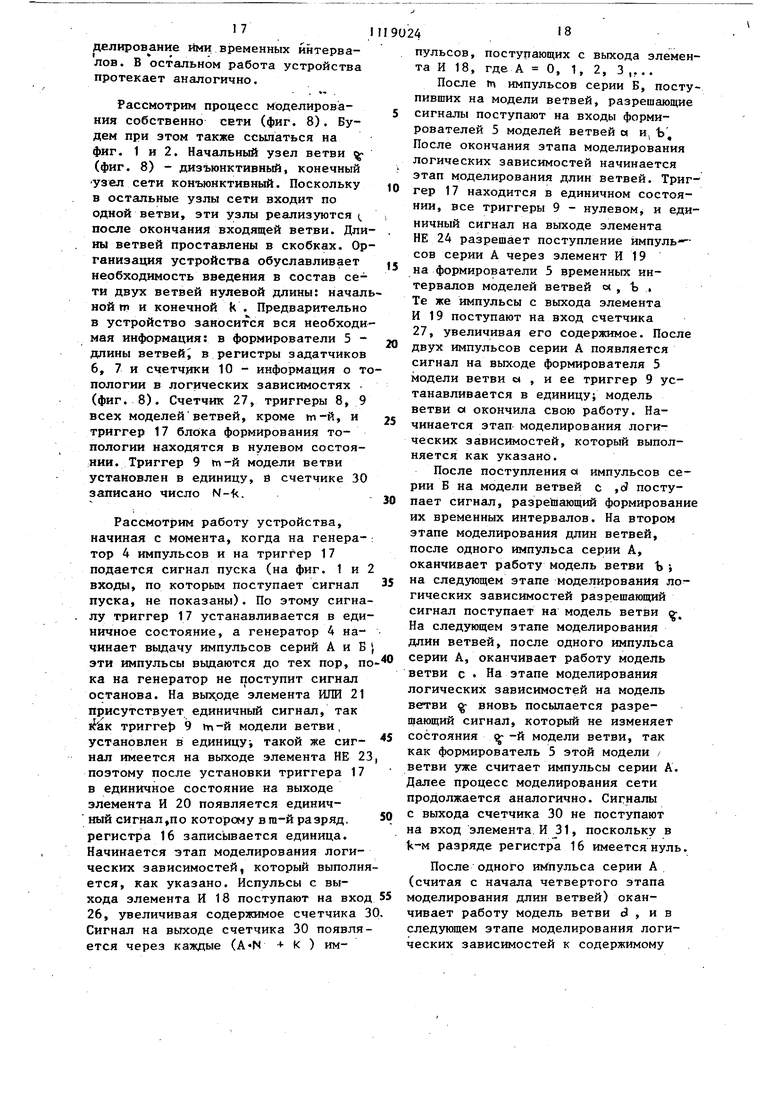

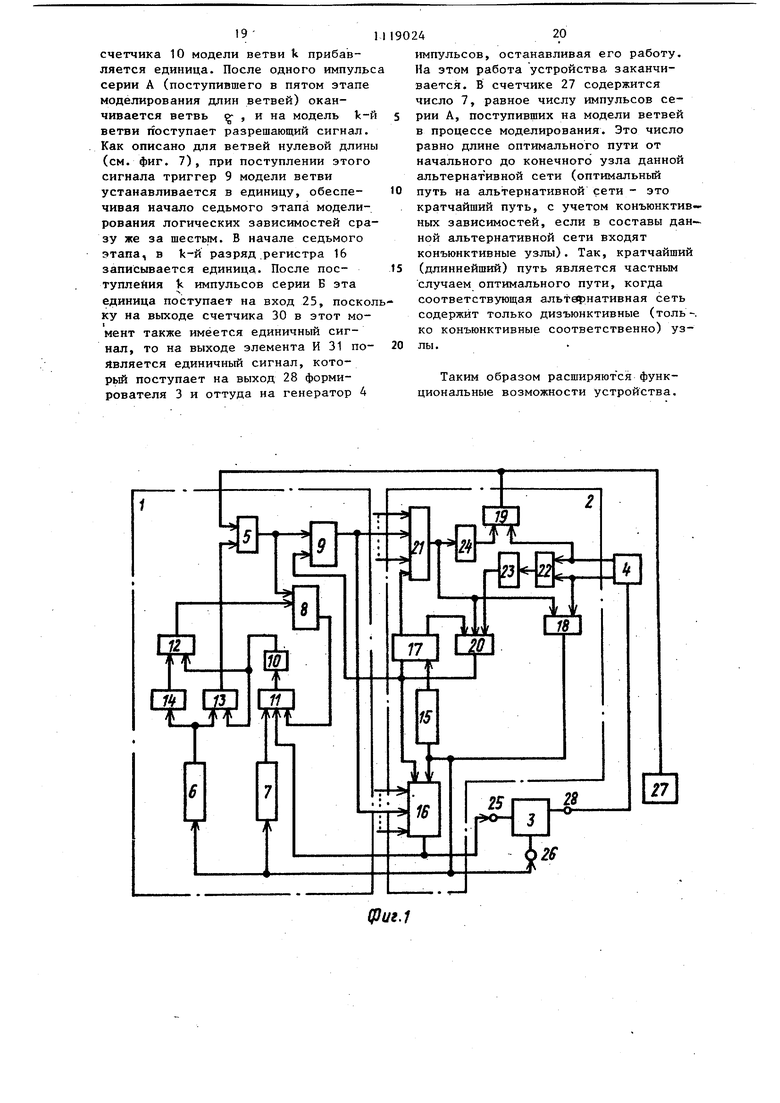

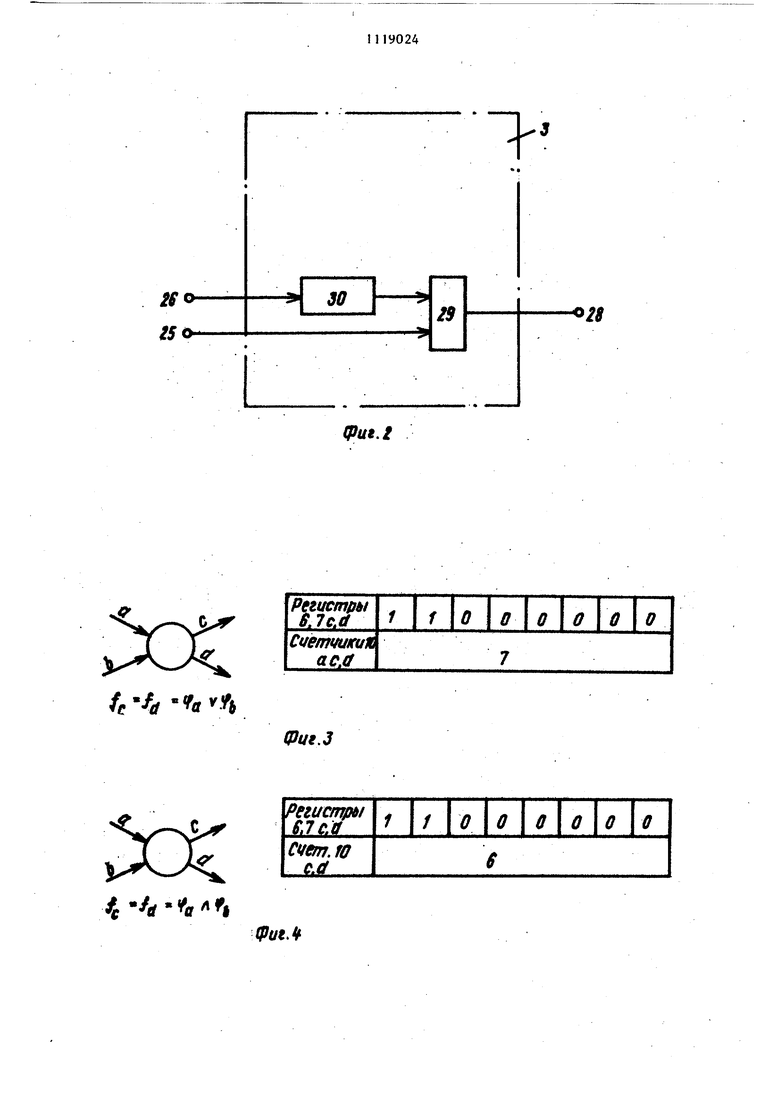

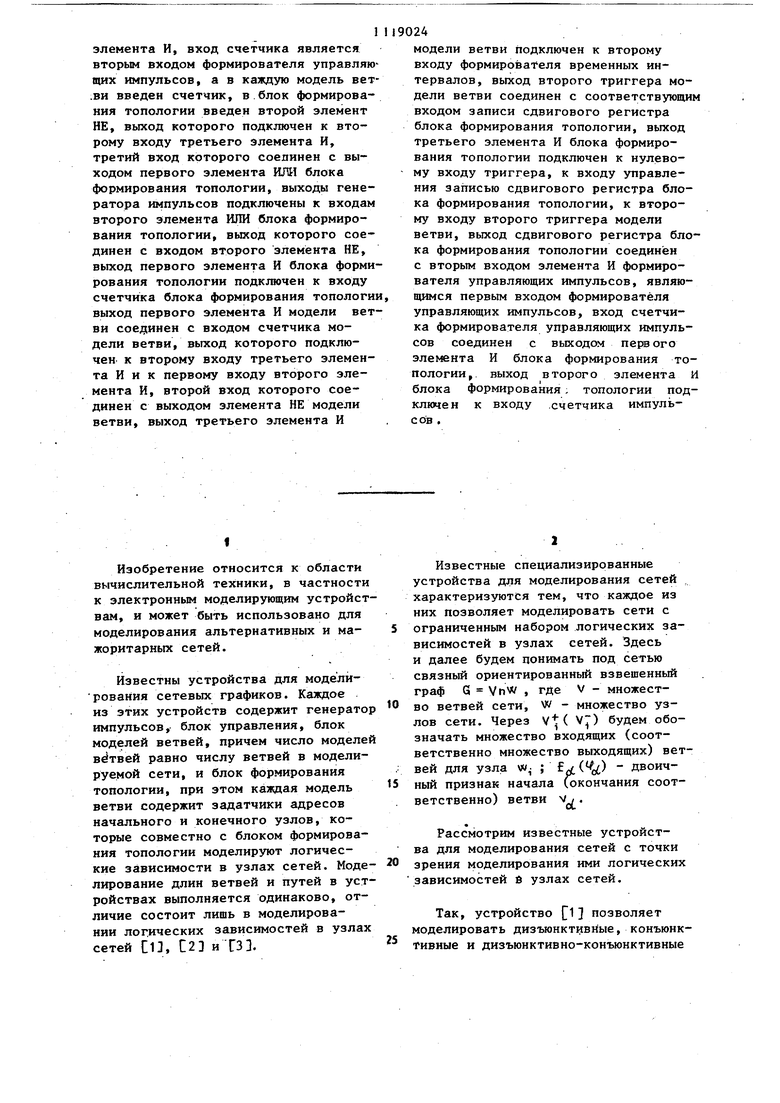

Изобретение относится к области вычислительной техники, в частности к электронным моделирующим устройст вам, и может быть использовано для моделирования альтернативных и мажоритарных сетей. Известны устройства для моделйрования сетевых графиков. Каждое иэ этих устройств содержит генерато импульсов, блок управления, блок моделей ветвей, причем число моделе ветвей равно числу ветвей в моделируемой сети, и блок формирования топологии, при этом каждая модель ветви содержит задатчики адресов начального и конечного узлов, которые совместно с блоком формирования топологии моделирзпот логические зависимости в узлах сетей. Моде лирование длин ветвей и путей в уст ройствах выполняется одинаково, отличие состоит лишь в моделировании логических зависимостей в узлах сетей СП. С2 и ГЗЗ. Известные специализированные устройства для моделирования сетей характеризуются тем, что каждое из них позволяет моделировать сети с ограниченным набором логических зависимостей в узлах сетей. Здесь и далее будем понимать под сетью связный ориентированный взвешенный граф G VnW , где V - множество ветвей сети, W - множество узлов сети. Через Vp будем обозначать множество входящих (соответственно множество выходящих) ветвей для узла w- ; EvCot Двоичный признак начала (окончания соответственно) ветви V;. Рассмотрим известные устройства для моделирования сетей с точки зрения моделирования ими логических зависимостей и узлах сетей. Так, устройство 1 позволяет моделировать дизъюнктивные, конъюнктивные и дизъюнктивно-конъюнктивные зависимости в узлах, которые описываются выражениями: .. (V)(W) vvУстройство для моделирования сетевых графиков 2 позволяет моделировать в узлах сети зависимости вида (1), (2) и выполнять ассоци тивный поиск по совокупности призна ков, т.е. реализовать зависимость вида Л ...,. (4) где П, Пп, , П - значения двоичных признаков, п которым ведется поиск; ., если П 1; П П , если Пр 0. Устройство 3 позволяет моделировать дизъюнктивные узлы с альтернативными и стохастическими выхо дами, т.е. peaлизo вaть зависимость (WV-).Vv,-v,...eVt ..4,-eV;., (5) где Rg - двоичный признак разрешения начала ветви Vg после окончания ее начального узла i при этом существует лишь одна ветвь, для которой этот признак равен в данный момент единице, т.е. из всех выходящих ветвей реализуется лишь одна. Для узла с альтернативными выходами значение признаков а t задается заранее, до начала моделирования сети, для узла со стохастическими выходами значение признака Rg связано с вероятностью реализаци ветви Vg и получается в процессе моделирования сети. Недостатком указанных устройств является узкий набор моделируемых логических зависимостей в узлах. Наиболее близким техническим решением к изобретению является устро ство для моделирования сетевых графиков, со ержащее блок управления, первый выход которого подключен к первому входу первого элемента ИЛИ блока формирования топологии, блок моделей ветвей по числу работ сете,вого -рафика, каждая из которых вып нена в виде задатчиков адресов, выходами соединенных с элементами И, причем выход первого элемента И соединен с входом формирователя временных интервалов, вход второго элемента И соединен через инвертор с первым входом элемента liJTM, к второму входу которого подключен выход второго элемента И, генератор импульсов, первый и второй выходы которого подключены соответственно к, второму входу первого элемента И каждой модели и первому входу первого элемента И блока формирования ТОПОЛОГИИ; второй вход которого соединен с входом инвертора блока формирования тоцологии, кроме того, каждая модель ветви содержит триггеры, входы которых соединены с формирователем временных интервалов, причем второй вход первого триггера подключен к первому входу второго элемента И, к второму входу которого и третьему входу первого элемента И подключены выходы второго триггера входы задатчиков адресов каждой .модели ветви соединены с выходом первого элемента ИЛИ блока формирования топологии содержащего второй элемент ИЛИ, подключенный через инвертор к входу второго элемента И, и последовательно соединенные третий элемент И и третий элемент ИЛИ, выход и вход которого подключены соответственно к входу и второму выходу блока управления, причем первый выход генератора импу;1ьсов соединен с вторым входом второго элемента И блока формирования топологии, выход которого подключен к входу формирователя временных интервалов каждой модели ветви, вход блока управления соединен с четвертым входом первого элемента И каждой модели ветви, выход первого триггера каждой модели ветви подключен к входу второго элемента ИЛИ блока формирования топологии, а выход второго элемента ИЛИ каждой модели ветви соединен с входом третьего элемента И блока формирования топологии, в каждую модель ветви введен дополнительный элемент И, в блок формирования топологии введены триггер, сдвиговый регистр и счетчик, вход которого соединен с входом сдвигового регистра и с выходом первого элемента ИЛИ блока формирования топологии, а выход счетчика соединен с единичным входом триггера бло формирования топологии, единичный выход которого подключен к одному из входов третьего элемента И блока формирования топологии, а нулевой рыход триггера соединен с одним из входов второго элемента 1ШИ блока формирования топологии, а выход сдвигового регистра подключен к пер вому входу дополнительного элемента каждой модели ветви, второй вход которого соединен с выходом задатчика адреса начального узла, а выход подключен к единичному входу второго триггера ветви 4. Устройство для моделирования сетевых графиков позволяет моделировать конъюнктивные сети с исключением ветвей, выходящих из запрещенных узлов W е W , т.е. реализовать зависимость вида « 4 - ot 0 - i.feV,R.0, «.-..ev: ,vv,v,...6V. . (6) Ни одно из известных устройств не может моделировать альтернативные и мажоритарные сети. Альтернативные сети отличаются от обычных сетевых графиков широким набором логических зависимостей в узлах. А именно, в число узлов альтернативной сети входят дизъюнктивные и конъюнк тивные с обычными выходами, а также дизъюнктивные и конъюнктивные с аль тернативными и стохастическими выхо дами. Эти зависимости описываются соответственно вьфажениями (1), (2) (5) и (7) V(c4,). . 3., vv,Vt,..6V- , (7) где смысл всех обозначений тот же что ив (5). Од«им из видов узлов альтернативной сети является также узел типа временной различитель. Для такого узла число выходящих вет вей равно числу входящих, и каждой выходящей ветви соответствует единственная входящая ветвь, так что признак R., принимает единичное значение только тогда, когда окончалас соответствующая , входящая ветвь. Так, если узел типа временной различитель дизъюнктивный, то после око чания первой входящей в него ветви начинается -только соответствующая этой ветви выходящая ветвь,.а остальные ветви исключаются. Таким образом, сетевой график представляет собой альтернативную сеть частного вида. Альтернативные сети охватывают существенно более широкий класс объектов и задач планирования и управления, нежели сетевые графики, в связи с чём моделирование таких сетей имеет большое практическое значение. Мажоритарные сети отличаются тем, что их узлы реализуют-мажори-. тарные функции. Важность моделирования таких сетей обусловлена широкими исследованиями по созданию вычислительных машин на мажоритарных элементах. Функция 1-го мажоритарного узла с тремя входами описывается выражением «а Ч --Ч%С.. . . c..4.-ev;,v.vp,v.v . (al Цель изобретения - расширение функциональных возможностей за счет моделирования альтернативных и мажоритарных сетей. Указанная цель достигается тем, что в устройство для моделирования сетевых графиков, содержащее генератор импульсов, формирователь управляющих импульсов, блок моделей ветвей, блок формирования топологии, включающий счетчик, сдвиговый регистр, триггер, элементы И, элементы ИЛИ, первый элемент НЕ, причем выход первого элемента ИЛИ соединен с первым входом первого элемента И, и через первый элемент НЕ - с первым входом второго элемента И вторые входы первого и второго элементов И соединены соответственно с первым и вторым выходами генератора импульсов, вход счетчика подключен к сдвиговому входу сдвигового регистра, выход счетчика соединен с единич ным входом триггера, единичный и нулевой выходы которого подключены соответственно к первым входам третьего элемента И и первого элемен та ИЛИ, каждая модель ветви включает триггеры, формирователь временных интервалов, элементы И, элемент НЕ и задатчики адресов начального и конемного узлов, входы которых объединены и соединены с входом счетчика блока формирования топологии, в каждой модели ветви выход первого триггера подключен к первому входу, первого элемента И, второй и третий входы которого соединены соответственно с выходом задатчика адреса начального узла и с первым входом формирователя управляющих импульсов выход формирователя временных интервалов модели ветви подключен к первым входам первого и второго триггеров, второй вход первого триггера соединен с выходом второго элемента И модели ветви, выход задатчика адр са конечного узла подключен к входу элемента НЕ и к первому входу треть го элемента И модели ветви, выход второго элемента И блока формирования топологии соединен с первым входом формирователя временных интервалов модели ветви, выход второг триггера модели ветви подключен к соответствующему входу первого элемента ИЛИ блока формирования топологии, введен счетчик импульсов, кроме того, формирователь управляющих импульсов содержит счетчик и эл мент И, выход которого является вых дом формирователя управляющих импульсов, выход счет1ика подключен к первому входу элемента И, вход счетчика является вторым входом фор мирователя управляющих импульсов, а в каждую модель ветви введен счетчик, в блок формирования топологии введен второй элемент. НЕ, выход которого подключен к второму входу третьего элемента И, третий вход которого соединен с выходом первого элемента ИЛИ блока формирования топологии, выходы генератора импуль сов подключены к входам второго элемента ИЛИ блока формирования топологии, выход которого соединен с входом второго элемента НЕ, выход первого элемента И блока формирования топологии, подключен к входу счетчика блока формирования топологии выход первого элемента И модели ветви соединен с входом счетчика мо дели ветви, выход которого подключен к второму входу третьего элег мента И и к первому входу второго элемента И, второй вход которого со динен с выходом элемента НЕ модели ветви, выход третьего элемента И модели ветви подключен к второму входу формирователя временных интервалов, выход второго триггера модели ветви соединен с соответствующим входом записи сдвигового регистра блока формирования топологии, выход третьего элемента И блока формирова ния топологии подключен к нулевому входу триггера, к входу управления записью сдвигового регистра блока формирования топологии, к второму входу второго триггера модели ветви, выход сдвигового регистра блока формирования топологии соединен с вторым входом элемента И формирователя управляющих импульсов, являющим ся первым входом формирователя управляющих импульсов, вход счетчика формирователя управляющих импульсов соединен с выходом первого элемента И блока формирования топологии, выход второго элемента И блока формирования топологии подключен к входу счетчика импульсов. На фиг, 1 изображена функциональная схема устройства для моделирования сетевых графиков; на фиг. 2 формирователь управляющих импульсов; на фиг. 3 - 7 - примеры моделирования логических зависимостей в узлах; на фиг. 8 - пример моделирования сети. Устройство содержит блок 1 моделей ветвей, блок 2 формирования топологий, формирователь 3 управляющих импульсов, генератор 4 импульсов. Каждая модель ветви содержит формирователь 5 временных интервалов, задатчики 6, 7 конечного и начального адресов соответственно, триггеры 8, 9, счетчик 10, элементы И 11 - 13, элемент НЕ 14. Блок формирования топологии содержит счетчик 15, сдвиговый регистр 16, триггер 17, элементы И 18-20, элементы ИЛИ 21-22, второй и первьй элементы НЕ 23 24. На фиг. 1 обозначены входы 25, 26 формирователя 5, счетчик импульсов 27 и выход 28 формирователя 3, на фиг. 2 - элемент И 29, счетчик 30. Регистр 16 блока формирования топологии является сдвиговым регистром с параллельной записью информации. Сдвиговый вход регистра соединен с выходом элемента И 18, а вход управления записью - с выходом элемента И 20. Последний вход регистра предназначен для записи в регистр информа

ции, присутствующей на входах, записи, соединенных с единичными выходами триггеров 9 моделей ветвей. Сдвиговый вход регистра предназначен для сдвига содержимого регистра вправо. Триггер 17 и счетчик 15 предназначены для того, чтобы обеспечить постоянную длительность этапа моделирования логических зависимостей. В качестве задатчиков 6, 7 конечного и начального адресов использованы кольцевые сдвиговые регистры. Эти регистры предназначены для записи информации о топологии моделируемой сети и о логических зависимостях в узлах сети. Выход каждого из этих регистров соединен с его же входом записи, за счет чего обеспечивается восстановление первоначально записанной информации через каждые N импульсов сдвига, N- число разрядов регистра. При зтом задатчик 7 предназначен для записи и хранения информации о логических зависимостях в узле (т.е. в разряде, соответствующем ветви Vj , в задатчик 7 ветви V.C занесена единица, если V входит в запись f ). Задатчик 6 предназначен для записи и хранения информации о признаках выбора (либо запрета) той или иной ветви при условии реализации ее начального узла (т.е. признаки .R, ). При этом вся логическая информация представлена через номера ветвей. А именно, j-и ветви сети поставлен в соответствие j-й разряд регистра 16 задатчиков 6 и 7. Номера узлов в процессе подготовки сети к моде,лированию и в процессе моделирования не используются. Формирователь 5 временных интервалов включает в себя дискретную линию задержки, например счетчик (на фиг. 1 не показан). Формирователь предназначен для отсчета импульсов, поступающих на его вход, в том случае, если предварительно на другой его вход было подано разрешение. При этом временной интервал между поступлением на формирователь разрешения и окончанием работы формирователя находится в соответствии с длиной моделируемой ветви. Формирователь предназначен для вьщачи сигнала окончания работы устройства. Счетчик 30 и элемент И 29 предназначены для вьщачи сигнала останова.

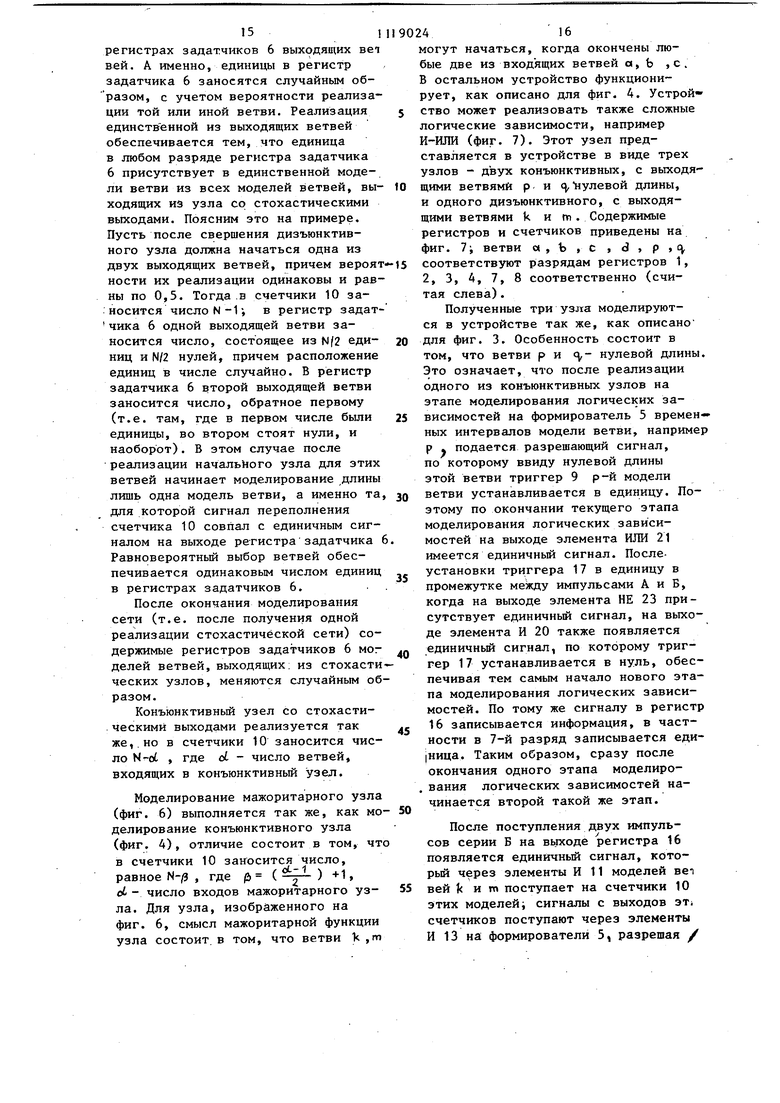

Подробно его функционирование расмотрим на примере моделирования сети (фиг.8). Генератор 4 импульсов предназначен для выдачи двух серий им5 пульсов - А и Б, сдвинутых друг относительно друга. Для вьщачи этих серий предназначены соответственно второй и первый выходы генератора.

Расмотрим работу устройства. 10 Моделирование сети выполняется посредством чередования двух этапов: этапа моделирования длин ветвей, когда на модели ветвей поступают .импульсы серии А, и этапа модели15 рования логических зависимостей,

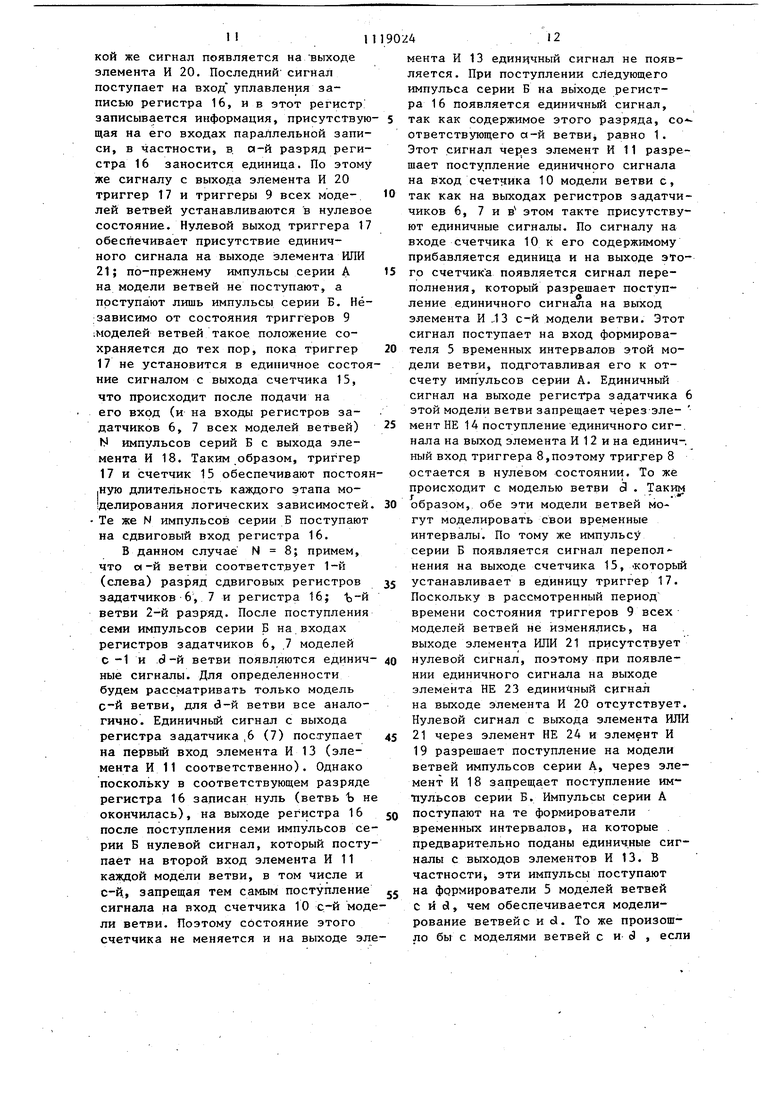

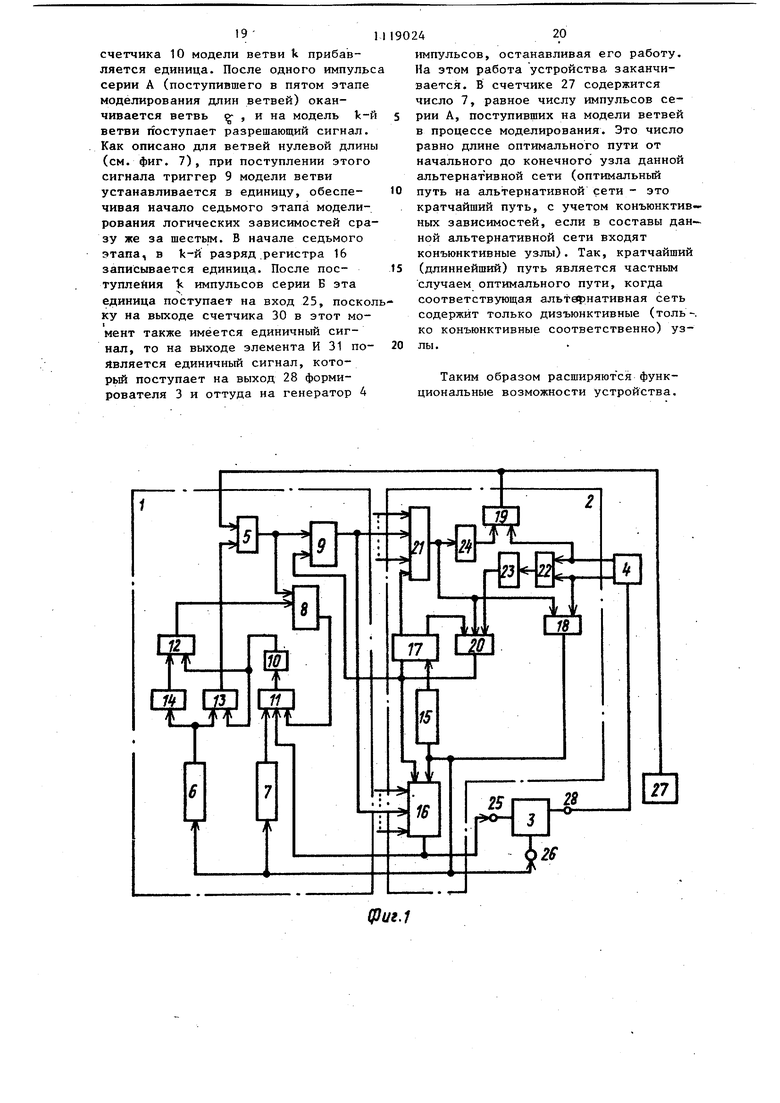

когда на модели ветвей поступают .. импульсы серии Б. Рассмотрим вначале моделирование различных логических, зависимостей (фиг. 3-7), а затем 0 моделирование сети в целом (фиг.8). I При этом полагаем, что (N - число разрядов регистров 16, 6, 7, а также емкости счетчиков 10 всех моделей ветвей и счетчика 15). Так, на фиг. 3 показано моделирование дизъюнкции. Отметим, что при моделировании узлов с обычными (неальтернативными) выходами содержимые регистров задатчиков 6 и 7 0 каждой модели ветви равны между собой. Рассмотрю работу устройства на примере фиг. 3, начиная с момента, когда окончилась ветвь сх . Это означает, что на выходе триггера 9 5 модели ветви а появился единичный сигнал, который проходит на выход элемента ИЛИ 21 и через элемент НЕ 24 и элемент И 19 запрещает поступление на модели ветвей импульсов серии 0 А. Этот же сигнал через элемент И 18 разрешает поступление импульсов серии Б на регистры задатчиков 6, 7 моделей ветвей. В рассматриваемый момент триггер 17 находится в еди5 ничном состоянии. По окончании импульса серии А, который обусловил появление единичного сигнала на выходе триггера 9 модели ветви q , на выходе элемента ИЛИ 22 появляется нулевой сигнал, а на выходе элемента НЕ 23 - единичный. Единичный сигнал на выходе элемента И 20 может появиться только тогда, когда на выходе элемента НЕ 23 присутствует , единичньй сигнал, т.е. в промежутках между импульсами серий А и Б. Посколь-ку на всех входах элемента И 20 присутствуют единичные сигналы, таП1кой же сигнал появляется на выходе элемента И 20. Последний сигнал поступает на вход уплавления записью регистра 16, ив этот регистр записывается информация, присутствую щая на его входах параллельной записи, в частности, в. а-й разряд регистра 16 заносится единица. По этому же сигналу с выхода элемента И 20 триггер 17 и триггеры 9 всех моделей ветвей устанавливаются в нулевое состояние. Нулевой выход триггера 17 обеспечивает присутствие единичного сигнала на выходе :элемента ИЛИ 21; по-прежнему импульсы серии А на модели ветвей не поступают, а поступают лишь импульсы серии Б. Независимо от состояния триггеров 9 ;моделей ветвей такое положение сохраняется до тех пор, пока триггер 17 не установится в единичное состоя ние сигналом с выхода счетчика 15, что происходит после подачи на его вход (и на входы регистров задатчиков 6, 7 всех моделей ветвей) N импульсов серий Б с выхода элемента И 18. Таким образом, триггер 17 и счетчик 15 обеспечивают постоян |Ную длительность каждого этапа моделирования логических зависимостей Те же N импульсов серии Б поступают на сдвиговый вход регистра 16. В данном случае N 8; примем, что «-и ветви соответствует 1-й (слева) разряд сдвиговых регистров задатчиков 6, 7 и регистра 16; й ветви 2-й разряд. После поступления семи импульсов серии Б на входах регистров задатчиков 6, .7 моделей с -1 и .d-и ветви появляются единичные сигналы. Для определенности будем рассматривать только модель С-й ветви, для d-й ветви все аналогично. Единичньм сигнал с выхода регистра задатчика ,6 (7) поступает на первый вход элемента И 13 (элемента И 11 соответственно). Однако поскольку в соответствующем разряде регистра 16 записан нуль (ветвь Ъ н окончилась), на выходе регистра 16 после поступления семи импульсов се рии Б нулевой сигнал, который посту пает на второй вход элемента И 11 каждой модели ветви, в том числе и с-й., запрещая тем самым поступление сигнала на вход счетчика 10 с-й мод ли ветви. Поэтому состояние этого счетчика не меняется и на выходе эл 412 мента И 13 единичный сигнал не появляется. При поступлении следующего импульса серии Б на выходе регистра 16 появляется единичный сигнал, так как содержимое этого разряда, соответствующего а-й ветвиj равно 1. Этот сигнал через элемент И 11 разрешает поступление единичного сигнала на вход счетг1ика 10 модели ветви с, так как на выходах регистров задатчичиков 6, 7 и в этом такте присутствуют единичные сигналы. По сигналу на входе счетчика 10 к его содержимому прибавляется единица и на выходе этого счетчика появляется сигнал переполнения, который разрешает поступление единичного сигнала на выход элемента И ЛЗ с-й модели ветви. Этот сигнал поступает на вход формирователя 5 временных интервалов ЭТой модели ветви, подготавливая его к отсчету импульсов серии А. Единичный сигнал на выходе регистра задатчика 6 этой модели ветви запрещает через элемент НЕ 14 поступление единичного сиг-, нала на выход элемента И 12 и на единич-. ный вход триггера 8,поэтому триггер 8 остается в нулевом состоянии. То же происходит с моделью ветви д . Таким образом, обе эти модели ветвей могут моделировать свои временные интервалы. По тому же импульс серии Б появляется сигнал перепол нения на выходе счетчика 15, жоторьй устанавливает в единицу триггер 17. Поскольку в рассмотренный период времени состояния триггеров 9 всех моделей ветвей не изменялись, на выходе элемента ИЛИ 21 присутствует нулевой сигнал, поэтому при появлении единичного сигнала на выходе элемента НЕ 23 единичный сигнал на выходе элемента И 20 отсутствует. Нулевой сигнал с выхода элемента ИЛИ 21 через элемент НЕ 24 и элемент И 19 разрещает поступление на модели ветвей импульсов серии А, через элемент И 18 запрещает поступление импульсов серии Б. Импульсы серии А поступают на те формирователи временных интервалов, на которые . предварительно поданы единичные сигналы с вьпсодов элементов И 13. В частностиj эти импульсы поступают на Формирователи 5 моделей ветвей с и (3, чем обеспечивается моделирование ветвей с и d. То же произошло бы с моделями ветвей с и d , если

бы первой окончилась ветвь Ъ либо ветви а и-Ъ окончились одновременно.

Моделирование конъюнкции (фиг. 4) отличается тем, что в счетчики 10 с-и и d-й моделей ветвей заносится число, равное в общем случае неМ-1, а N-ot , где od - число ветвей, входящих в узел, начальный для с и . Конкретно для фиг. 4 ,T.e. в счетчиках 10 моделей с-и и d-й ветвей Занесено число 6. Таким образом, сигнал переполнения на выходе счетчика 10 появляется после того, как к его содержимому прибавлены две единицы, т.е. после того, как окончились обе ветви ot и Ь . Этапы моделирования логических зависимостей после окончания ветвей а и Ъ, если они окончились в разное время, выполняются так же,как указано. В течение первого этапа к содержимым счетчиков 10 моделей с-и и -й ветве прибавляется по единице, после чего их содерзкимые становятся равными 7. Сигнал переполнения появляется на их выходах только после второго этапа, когда окончилась вторая ветвь (а либо b). Если же ветви а и Ъ окончились одновременно, то в начале этапа моделирования логических зависимостей присутствуют единичные ;сигнальг иа выходах- триггеров 9 ot-й и Ь-й моделей ветвей и по сигналу с выхода элемента И 20 записываются единицы как в сл-й, так и в Ь-й разряды регистра 16. В этом случае прибавление двух единиц к содержимым счетчиков 10 моделей ветвей сив выполняется в течение одного этапа. В остальном устройство работает, как указано.

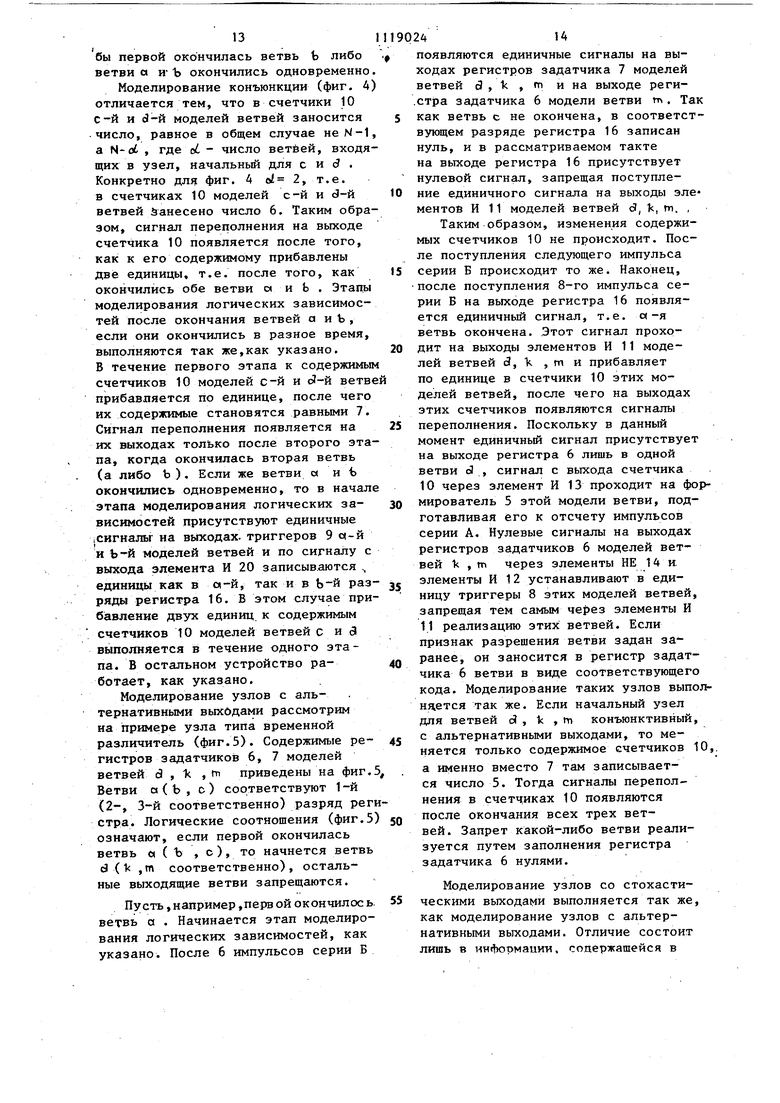

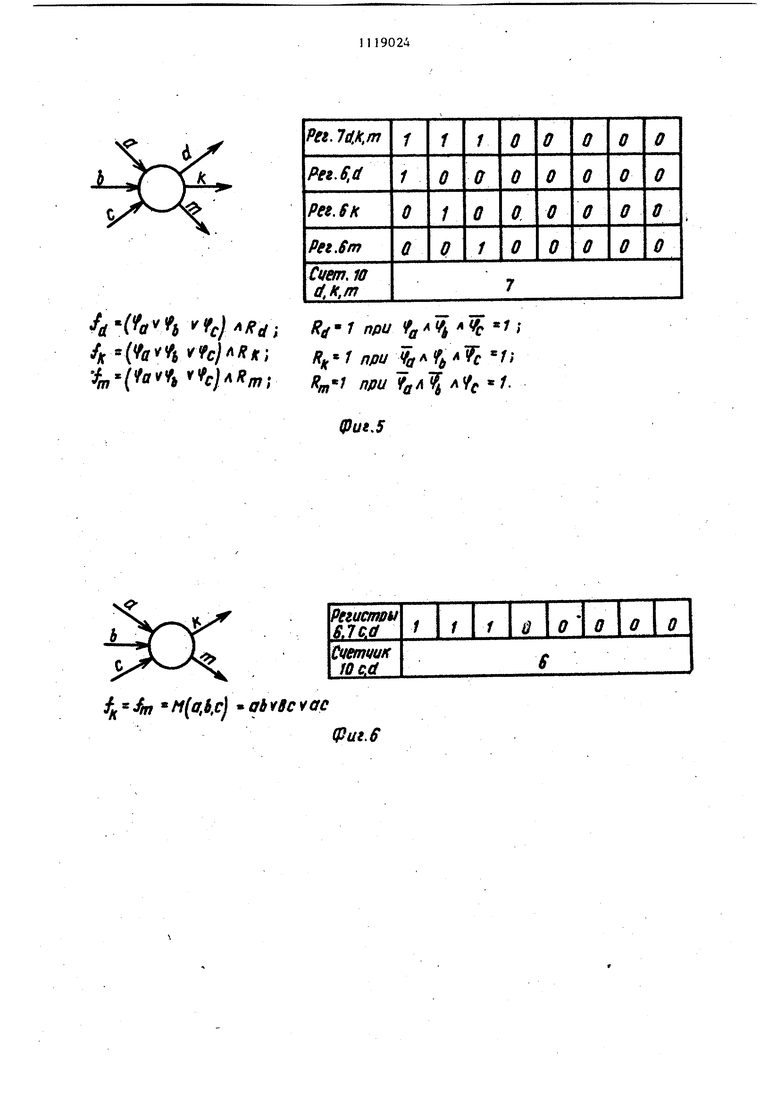

Моделирование узлов с альтернативными выходами рассмотрим на примере узла типа временной различитель (фиг.5). Содержимые регистров задатчиков 6, 7 моделей ветвей d , К , гп приведены на фиг.5 Ветви а(Ь, с) соответствуют 1-й (2-, 3-й соответственно) разряд регистра. Логические соотношения (фиг.5) означают, если первой окончилась ветвь ск ( Ъ , с), то начнется ветвь d (1 ,т соответственно), остальные выходящие ветви запрещаются.

Пусть, например,первой окончилось ветвь а . Начинается этап моделирования логических зависимостей, как указано. После 6 импульсов серии Б

появляются единичные сигналы на выходах регистров задатчика 7 моделей ветвей (3 , 1 , fn и на выходе реги.стра задатчика 6 модели ветви m. Та как ветвь с не окончена, в соответствующем разряде регистра 16 записан нуль, и в рассматриваемом такте на выходе регистра 16 присутствует нулевой сигнал, запрещая поступление единичного сигнала на выходы элементов И 11 моделей ветвей d, 1с, m. ,

Таким образом, изменения содержимых счетчиков 10 не происходит. После поступления следующего импульса серии Б происходит то же. Наконец, после поступления 8-го импульса серии Б на выходе регистра 16 появляется единичный сигнал, т.е. а-я ветвь окончена. Этот сигнал проходит на выходы элементов И 11 моделей ветвей (3, V. , m и прибавляет по единице в счетчики 10 этих моделей ветвей, после чего на выходах этих счетчиков появляются сигналы переполнения. Поскольку в данный момент единичный сигнал присутствует на выходе регистра 6 лишь в одной ветви d , сигнал с выхода счетчика

10через элемент И 13 проходит на фомирователь 5 этой модели ветви, подготавливая его к отсчету импульсов серии А. Нулевые сигналы на выходах регистров задатчиков 6 моделей ветвей V , m через элементы НЕ 14 и элементы И 12 устанавливают в единицу триггеры 8 этих моделей ветвей, запрещая тем самым через элементы И

11реализацию этих ветвей. Если признак разрешения ветви задан заранее, он заносится в регистр задатчика 6 ветви в виде соответствующего кода. Моделирование таких узлов выпоняется так же. Если начальный узел для ветвей d , 1 , m конъюнктивный,

с альтернативными выходами, то меняется только содержимое счетчиков 1

а именно вместо 7 там записывается число 5. Тогда сигналы переполнения в счетчиках 10 появляются после окончания всех трех ветвей. Запрет какой-либо ветви реализуется путем заполнения регистра задатчика 6 нулями.

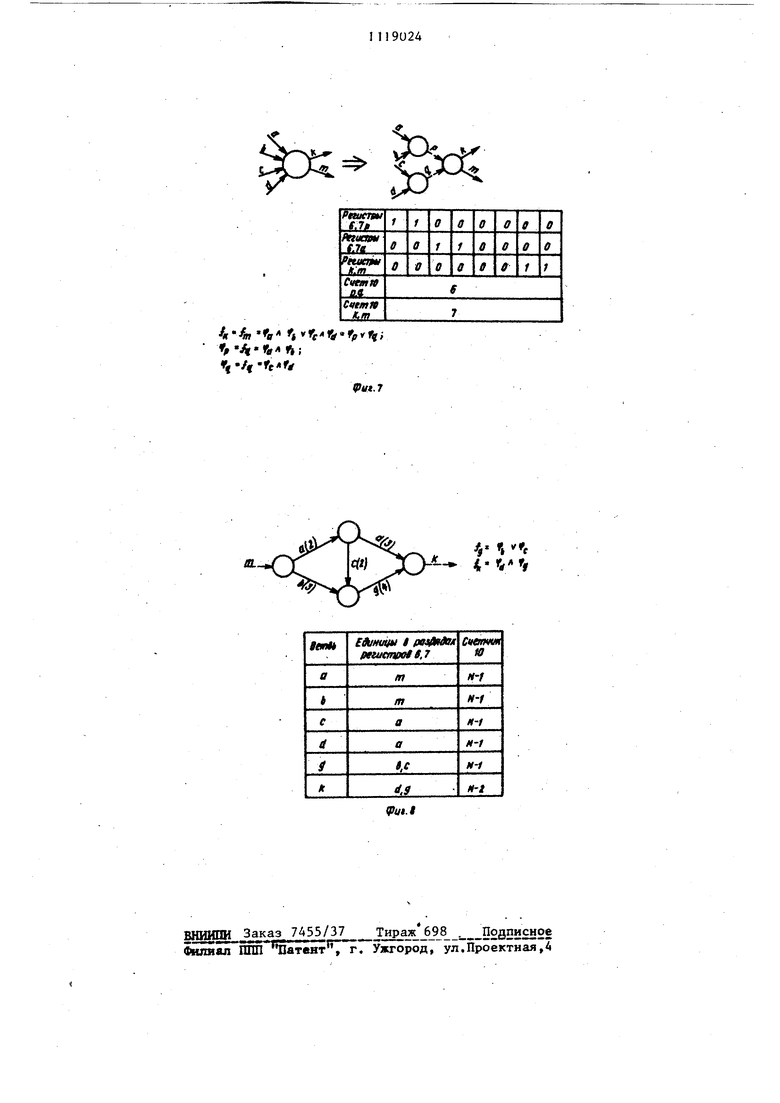

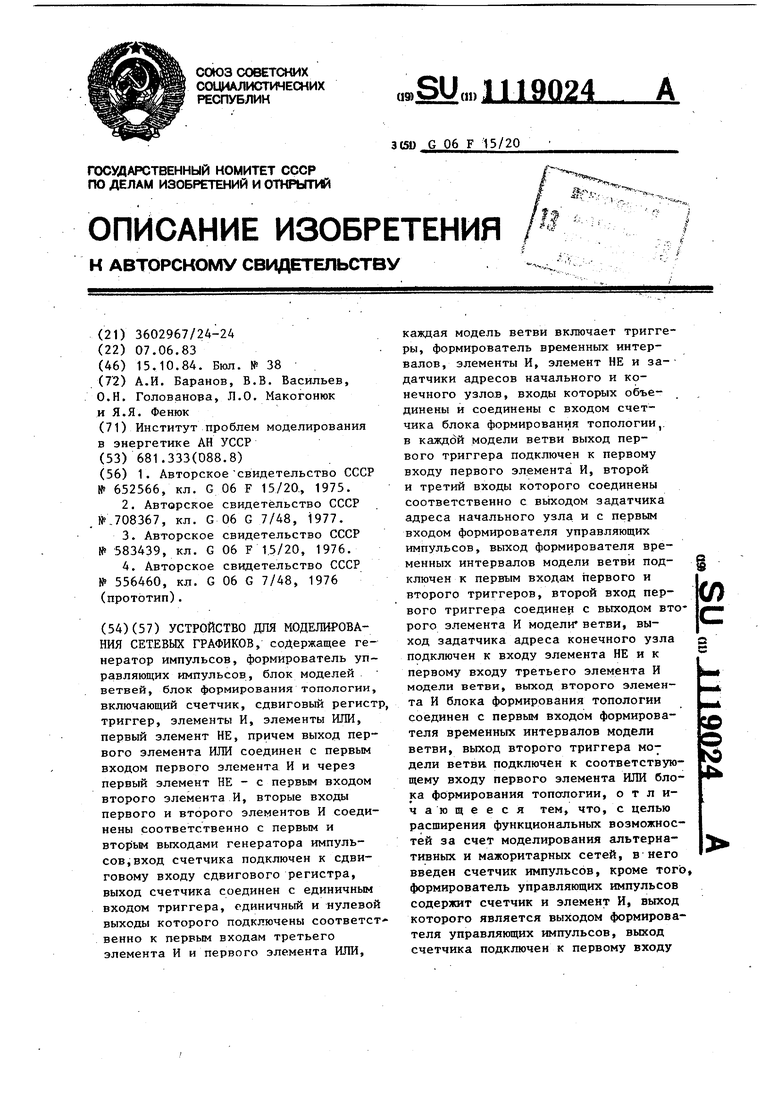

Моделирование узлов со стохастическими выходами выполняется так же, как моделирование узлов с альтернативными выходами. Отличие состоит лишь в информации, содержащейся в 15 регистрах задатчиков 6 выходящих ве вей. А именно, единицы в регистр задатчика 6 заносятся случайным образом, с учетом вероятности реализа ции той или иной ветви. Реализация единственной из выходящих ветвей обеспечивается тем, что единица в любом разряде регистра задатчика 6 присутствует в единственной модели ветви из всех моделей ветвей, вы ходящих из узла со стохастическими выходами. Поясним это на примере. Пусть после свершения дизъюнктивного узла должна начаться одна из двух выходящих ветвей, причем вероя ности их реализации одинаковы и рав ны по 0,5. Тогда .в счетчики 10 заносится число N-1 , в регистр задат чика 6 одной выходящей ветви заносится число, состоящее из Nf2 единиц и N/2 нулей, причем расположение единиц в числе случайно. В регистр задатчика 6 второй выходящей ветви заносится число, обратное первому (т.е. там, где в первом числе были единицы, во втором стоят нули, и наоборот). В этом случае после реализации начального узла для этих ветвей начинает моделирование длины лишь одна модель ветви, а именно та для которой сигнал переполнения счетчика 10 совпал с единичным сигналом на выходе регистразадатчика Равновероятный выбор ветвей обеспечивается одинаковым числом единиц в регистрах задатчиков 6. . После окончания моделирования сети (т.е. после получения одной реализации стохастической сети) содержимые регистров задатчиков 6 мог делей ветвей, выходящих: из стохасти ческих узлов, меняются случайным об разом. Конъюнктивный узел со стохасти.ческимй выходами реализуется так же,.но в счетчики 10 заносится число , где cL - число ветвей, входящих в конъюнктивный узел. Моделирование мажоритарного узла (фиг. 6) выполняется так же, как мо делирование конъюнктивного узла (фиг. 4), отличие состоит в том, чт в счетчики 10 заносится число, равное N- , где |й ( ) +1, d- - число входов мажоритарного узла. Для узла, изображенного на фиг. 6, смысл мажоритарной функции узла состоит в том, что ветви X ,т 416 могут начаться, когда окончены любые две из входящих ветвей а, Ь ,с. В остальном устройство функционирует, как описано для фиг. 4. Устройство может реализовать также сложные логические зависимости, например И-ИЛИ (фиг. 7). Этот узел представляется в устройстве в виде трех узлов - двух конъюнктивных, с выходящими ветвями р и (нулевой длины, и одного дизъюнктивного, с выходящими ветвями k и m. Содержимые регистров и счетчиков приведены на фиг. 7i ветви а , Ъ , с , d , р , CJ, соответствуют разрядам регистров 1, 2, 3, 4, 7, 8 соответственно (считая слева). Полученные три узла моделируются в устройстве так же, как описано для фиг. 3. Особенность состоит в том, что ветви р и - нулевой длины. Это означает, что после реализации одного из конъюнктивных узлов на этапе моделирования логических зависимостей на формирователь 5 временных интервалов модели ветви, например р J подается разрешающий сигнал, по которому ввиду нулевой длины этой ветви триггер 9 р-й модели ветви устанавливается в единицу. Поэтому по окончании текущего этапа моделирования логических зависимостей на выходе элемента ИЖ 21 имеется единичньй сигнал. Послеустановки триггера 17 в единицу в промежутке между импульсами А и В, когда на выходе элемента НЕ 23 присутствует единичный сигнал, на выходе элемента И 20 также появляется единичньй сигнал, по которому триггер 17 устанавливается в нуль, обеспечивая тем самым начало нового этапа моделирования логических зависимостей. По тому же сигналу в регистр 16 записывается информация, в частности в 7-й разряд записывается еди|ница. Таким образом, сразу после окончания одного этапа моделирования логических зависимостей начинается второй такой же этап. После поступления двух импульсов серии В на вьпсоде регистра 16 появляется единичный сигнал, который через элементы И 11 моделей веч вей } и го поступает на счетчики 10 этих моделей; сигналы с выходов эт; счетчиков поступают через элементы И 13 на формирователи 5, разрешая / 7 делирование ими временных интервалов. В остальном работа устройства протекает аналогично. Рассмотрим процесс моделирования собственно СЕТИ (фиг. 8). Будем при этом также ссылаться на фиг. 1 и 2. Начальный узел ветви (фиг. 8) - дизъюнктивный, конечный узел сети конъюнктивный. Поскольку в остальные узлы сети входит по одной ветви, эти узлы реализуются (. после окончания входящей ветви. Дли ны ветвей проставлены в скобках. Ор ганизация устройства обуславливает необходимость введения в состав сети двух ветвей нулевой длины; начал ной m и конечной k . Предварительно в устройство заносится вся необходи мая информация: в формирователи 5 длины ветвей в регистры задатчиков 6, 7 и счетчики 10 - информация о т пологии в логических зависимостях . (фиг. 8). Счетчик 27, триггеры 8, 9 всех моделейветвей, кроме гп-й, и триггер 17 блока формирования топологии находятся в нулевом состоянии. Триггер 9 w-й модели ветви установлен в единицу, и счетчике 30 записано число N-f. Рассмотрим работу устройства, начиная с момента, когда на генератор 4 импульсов и на триггер 17 подается сигнал пуска (на фиг. 1 и входы, по которым поступает сигнал пуска, не показаны). По этому сигна лу триггер 17 устанавливается в еди ничное состояние, а генератор 4 начинает вьщачу импульсов серий А и Б эти импульсы вьщаются до тех пор, п ка на генератор не поступит сигнал останова. На вых.оде элемента ИЛИ 21 присутствует единичный сигнал, так if&K триггер 9 т-й модели ветви, установлен в единицуi такой же сигнал имеется на выходе элемента НЕ 2 поэтому после установки триггера 17 в единичное состояние на выходе элемента И 20 появляется единичный сигнал,по которому вга-й разряд, регистра 16 записывается единица. Начинается этап моделирования логических зависимостей, который выполн ется, как указано. Испульсы с выхода элемента И 18 поступают на вхо 26, увеличивая содержимое счетчика Сигнал на выходе счетчика 30 появля ется через каждые (A«N К ) им4пульсов, поступающих с выхода элемента И 18, где А О, 1, 2, 3 ,,.. После п импульсов серии Б, поступивших на модели ветвей, разрешающие сигналы поступают на входы формирователей 5 моделей ветвей а и, Ъ После окончания этапа моделирования логических зависимостей начинается этап моделирования длин ветвей. Триггер 17 находится в единичном состоянии, все триггеры 9 - нулевом, и единичный сигнал на выходе элемента НЕ 24 разрешает поступление ймпулЬ сов серии А через элемент И 19 на формирователи 5 временных интервалов моделей ветвей «,13. Те же импульсы с выхода элемента И 19 поступают на вход счетчика 27, увеличивая его содержимое. После двух импульсов серии А появляется сигнал на выходе формирователя 5 ;модели ветви « , и ее триггер 9 устанавливается в единицу; модель ветви а окончила свою работу. Начинается этап моделирования логических зависимостей, который выполняется как указанб. После поступления а импульсов серии Б на модели ветвей с ,d поступает сигнал, разрешающий формирование их временных интервалов. На втором этапе моделирования длин ветвей, после одного импульса серии А, оканчивает работу модель ветви Ъ i на следующем этапе моделирования логических зависимостей разрешающий сигнал поступает на модель ветви g-. На следующем этапе моделирования длин ветвей, после одного импульса серии А, оканчивает работу модель ветви с . На этапе моделирования логических зависимостей на модель ветви вновь посьшается разрещающий сигнал, который не изменяет состояния -и модели ветви, так как формирователь 5 этой модели / ветви уже считает импульсы серии А. Далее процесс моделирорания сети продолжается аналогично. Сигналы с выхода счетчика 30 не поступают на вход элемента И 31, поскольку в Я-м разряде регистра 16 имеется нуль. После одного импульса серии А (считая с начала четвертого этапа моделирования длин ветвей) оканчивает работу модель ветви d , и в следующем этапе моделирования логических зависимостей к содержимому 19счетчика 10 модели ветви k прибавляется единица. После одного импульс серии А (поступившего в пятом этапе моделирования длин ветвей) оканчивается ветвь , и на модель k-f ветви поступает разрешающий сигнал. Как описано для ветвей нулевой длины (см. фиг. 7), при поступлении этого сигнала триггер 9 модели ветви устанавливается в единицу, обеспечивая начало седьмого этапа моделирования логических зависимостей сра зу же за шестьм. В начале седьмого этапа, в k-й разряд регистра 16 записывается единица. После поступлейия Я импульсов серии Б эта единица поступает на вход 25, поскол ку на выходе счетчика 30 в этот момент также имеется единичный сигнал, то на выходе элемента И 31 поЯвляется единичный сигнал, который поступает на выход 28 формирователя 3 и оттуда на генератор 4 4 импульсов, останавливая его работу. На этом работа устройства заканчивается. В счетчике 27 содержится число 7, равное числу импульсов серии А, поступивших на модели ветвей в процессе моделирования. Это число равно длине оптимального пути от начального до конечного узла данной альтернативной сети (оптимальный путь на альтернативной сети - это кратчайший путь, с учетом конъюнктивных зависимостей, если в составы данной альтернативной сети входят конъюнктивные узлы). Так, кратчайший (длиннейший) путь является частным случаем оптимального пути, когда соответствующая альтернативная сеть содержит только дизъюнктивные (толь-, ко конъюнктивные соответственно) узлы. Таким образом расширяются функциональные возможности устройства.

(риг.1

30

ffOi5

(put. I

V-f

v-0

fe fa 4a /

(Pi/f.J

4-yrf-vi/tf|

(/«.4

Т

23

IS

при ;

при /; при «/.

Фик.5

: j «/Yffl;Arj fl Bc yffc

(pui.ff

-YС- V Jk

r4 fa

(

Фш. 7

/,. n

j|;- frf V

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Модель ветви графа | 1975 |

|

SU652566A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-15—Публикация

1983-06-07—Подача