Изобретение относится к радиотехнике н может быть испо.пьзовано в системах передачи дискретных сигналов.

Одним из известных стартстопных регенераторов, используемых для регенерации по форме и длительности посылок стартстопной телеграфной комбинации, является регенератор, содержащий входной, исправляющий и выходной узлы, а также упразляемый делитель частоты н счетную схему со спусковым реле для управления упомянутым деЛн.телем 1j.

Однако известный регенераюр нельзя использовать в приемниках стартстопно-сннхронных систем для коррекции длительности стоповых посылок.

Наиболее близкнм техническим решением к предлагаемому устройству является регенератор приемника стартстопных телеграфных сигналов, содержащий формирователь входных снгналов, на управляющий вход которого поданы управляющне нмнульсы, н последовательно соеднненные делнтель частоты, на управляющнй вход которого поданы тактовые нмпульсы, счётчнк н спусковое реле, к другому входу которого подключен выход

блока коррекции, причем выход спускового реле подключен к другому входу счетчика, а выход делителя частоты подключен к тактовому входу блока коррекции (2).

Однако и этот регенератор невозможно применять в приемниках стартстопно-сннхронных систем для коррекции длительности стоповых посылок из-за низкой помехоустойчивости.

Цель изобретения - повышение помехоустойчивости путем регенерации стоповой посылки телеграфных сигналов.

Для этого в регенератор прнемника стартстопных телеграфных сигналов, содержащнй формирователь входных снгналов, на управляющнй вход которого поданы управляющне нмпульсы, н последовательно соеднненные делнтель частоты, на управляющий вход которого поданы тактовые нмпульсы, счётчнк н спусковое реле, к другому входу которого подключен выход блока коррекции, причем выход спускового реле подключен к другому входу счётчика, а выход делителя частоты подключен к тактовому входу блока коррекцин, введены фазовый днскримннатор, блок

вычитания, реверсивный счетчик, блок совпадения и блок эластичгюй памяти.

Между выходом формирователя входных сигналов и информационным входом блока коррекции, включен блок эластичной памяти, выход которого через блок вычитания подключен ко входу фазового дискриминатора и к вычитающему входу реверсивного счетчика. К суммирующему входу счетчика подключен выход фазового дискриминатора, выход реверсивного счетчика подключен к другому входу блока вычитания и к соответствующему входу блока эластичной памяти, а выходы счетчика и блока коррекции подключены соответственно ко входам блока совпадения, выход которого подключен к соответствующему входу блока вычитания и к дополнительному входу делителя частоты. Выход делителя частоты подключен к соответствующему входу фазового дискриминатора, причем на управляющие входы фазового дискриминатора и блока эластичной памяти поданы управляющие импульсы, а на тактовый вход блока вычитания соответственно тактовые импульсы.

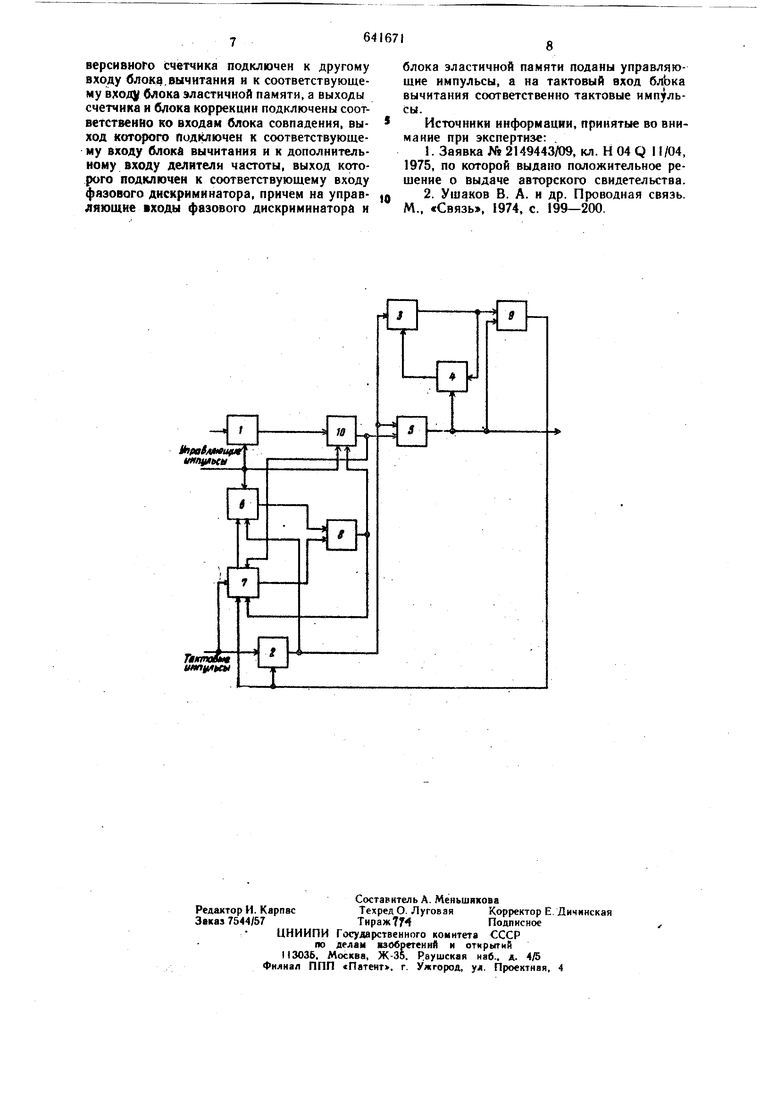

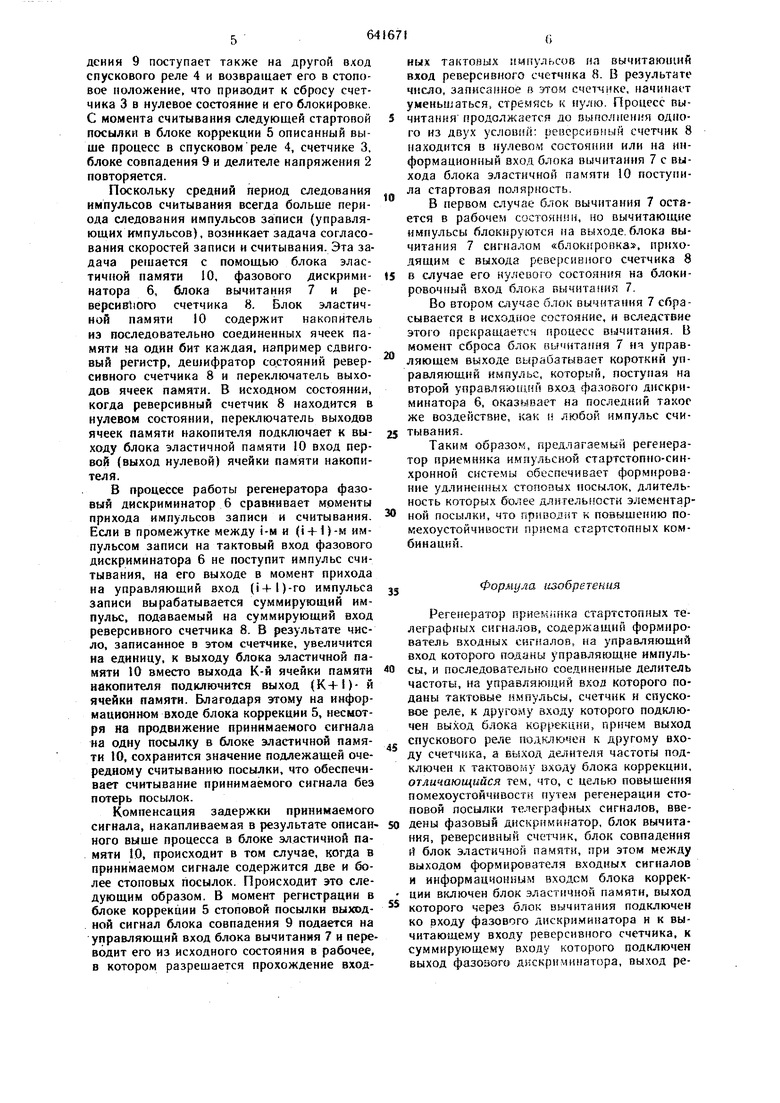

На чертеже приведена структурная электрическая: схема предложенного регенератора.

Регенератор приемника стартстопных телеграфных сигналов содержит формирователь входных сигналов 1, на управляющий вход которого поданы управляющие импульсы, и последовательно соединенные делитель частоты 2, на управляющий вход которого поданы тактовые импульсы, счетчик 3 и спусковое реле 4, к другому входу которого подключен выход блока коррекции 5. Выход спускового реле 4 подключен к другому входу счетчика 3, а йыход делителя частоты 2 подключен к тактовому входу блока коррекции 5,

Регенератор также содержит фазовый дискриминатор 6, блок вычитания 7, реверсивный счетчик 8, блок совпадения 9 и блок эластичной памяти Ю. Между выходом, формирователя входных сигналов 1 и информационным входом блока коррекции 5 включен блок эластичной памяти 10, выход которого через блок вычитания 7 подключен ко входу фазового дискриминатора 6 и к вычитающему входу реверсивного счетчика 8.

К суммирующему входу счетчика 8 подключен выход фазового дискриминатора 6, выход реверсивного счетчика 8 подключен к другому входу блока вычитания 7 и к соответствующему входу блока эластичной памяти 10. Выходы счетчика 3 и блока коррекции 5 подключены соответственно ко входам блока совпадения 9, выход которого подключен к соответствующему входу блока вычитания 7 и к дополнительному входу делителя частоты 2. Выход последнего подключен к соответствующему входу фазового дискриминатора 6, причем на управляющие входы фазового дискриминатора 6 и блока эластичной памяти 10 поданы управляющие импульсы, а на тактовый вход блока вычитания 7 соответственно тактовые импульсы.

Регенератор работает следующим образом.

В стоповом положении регенератора счетчик 3 заблокирован в нулевом состоянии управляющим сигналом с выхода спускового

реле 4, которое находится в стоповом положении. Кроме того, реверсивный счетчик 8 находится в нулевом состоянии, а управляемый делитель частоты 2 делит частоту входных тактовых импульсов в К раз так, чтобы период следования выходных тактовых импульсов был равен длительности элементарной посылки Го.

В формирователе входных сигналов 1 с помощью управляющих импульсов из группового многоканального сигнала импульсной стартстопно-синхронной системы выделяется сигнал данного канала и с помощью этих же управляющих импульсов, период следования которых г го, записывается в блок эластичной памяти 10. С выхода блока 10 сигнал с помощью блока коррекции 5

5 считывается в моменты прихода тактовых импульсов на вход этого блока благодаря . чему осуществляется коррекция длительности посылок принимаемого сигнала.

Коррекция длительности стоповой посылки осуществляется при помощи счетчика 3, спускового реле 4, блока совпадения 9 и управляемого делителя частоты 2. В момент считывания в блоке коррекции 5 стартовой посылки срабатывает спусковое реле 4 и разрещает работу счетчика 3, подсчитывающего

5 количество считывающих (выход1гых тактовых) импульсов, начиная с первой (стартовой) посылки в стартстопной комбинации. После подсчета числа импульсов, равного минимальному числу посылок в стартстопной комбинации, на выходе счетчика 3 ноявляется сигнал, подаваемый на вход блока совпадения 9. Если на другой вход блока совпадения 9 а этот момент с выхода блока коррекции 5 поступает стоповая полярность, то с выхода блока совпадения 9 подается сиг5 пал на управляющий вход управляемого делителя частоты 2 и увеличивает его коэффициент деления частоты до величины Tak, чтобы следующий считывающий ( выходной тактовый), импульс был выработан через интервал Тс to. Затем коэффици-.

o ент деления частоты управляемого делителя частоты 2 возвращается к прежнему значению К, что обеспечивает удлинение стоповой посылки на Дт . Величина L выбирается таким образом, чтобы длительность стартстопного цикла на выходе регенератора не превыщала минимально допустимую длительность стартстопного цикла на входе стартстопно-синхронной системы.

Выходной сигнал счетчика 3 одновременно с поступлением на вход блока совпадения 9 поступает также на другой вход спускового реле 4 и возвращает его в стоповое положение, что приводит к сбросу счетчика 3 в нулевое состояние и его блокировке. С момента считывания следующей стартовой посылки в блоке коррекции 5 описанный выше процесс в спусковом реле 4, счетчике 3. блоке совпадения 9 и делителе напряжения 2 повторяется.

Поскольку средний период следования импульсов считывания всегда больше периода следования импульсов записи (управляющих импульсов), возникает задача согласования скоростей записи и считывания. Эта задача решается с помощью блока эластичной памяти 10, фазового дискриминатора 6, блока вычитания 7 и реверсив1тго счетчика 8. Блок эластичной памяти 10 содержит накоийтель из последовательно соединенных ячеек памяти на один бит каждая, например сдвиговый регистр, дешифратор состояний реверсивного счетчика 8 и переключатель выходов ячеек памяти. В исходном состоянии, когда реверсивный счетчик 8 находится в нулевом состоянии, переключатель выходов ячеек памяти накопителя подключает к выходу блока эластичной памяти 10 вход первой (выход нулевой) ячейки памяти накопителя.

В процессе работы регенератора фазовый дискриминатор 6 сравнивает моменты прихода импульсов записи и считывания. Если в промежутке между i-м и (i-f 1)-м импульсом записи на тактовый вход фазового дискриминатора 6 не поступит импульс считывания, на его выходе в момент прихода на управляющий вход (i4-l)-ro импульса записи вырабатывается суммирующий импульс, подаваемый на суммирующий вход реверсивного счетчика 8. В результате число, записанное в этом счетчике, увеличится на единицу, к выходу блока эластичной памяти 10 вместо выхода К-й ячейки памяти накопителя подключится выход (К-Ь1)- и ячейки памяти. Благодаря этому на информационном входе блока коррекции 5, несмотря на продвижение принимаемого сигнала на одну посылку в блоке эластичной памяти 10, сохранится значение подлежащей очередному считыванию посылки, что обеспечивает считывание принимаемого сигнала без потерь посылок.

Компенсация задержки принимаемого сигнала, накапливаемая в результате описанного выше процесса в блоке эластичной памяти 10, происходит в том случае, когда в принимаемом сигнале содержится две и более стоповых посылок. Происходит это следующим образом. В момент регистрация в блоке коррекции 5 стоповой посылки выж дной сигнал блока совпадения 9 подается на управляющий вход блока вычитания 7 и переводит его из исходного состояния в рабочее, в котором разрешается прохождение входных тактовых импульсов на вычитающий вход реверсивного счетчика 8. В результате число, записанное в этой счепиже, начинает уменьшаться, стремясь к нулю. Процесс вычитания продолжается до выполнения одного из двух условий: реисрсиоиый счетчик 8 находится в нулевом состоянии или на информационный вход блока вычитания 7 с выхода блока эластичной 10 поступила стартовая полярность.

В первом случае блок вычитания 7 остается в рабочем состоянии, но вычитающие импульсы блокируются на выходе, блока вычитания 7 Сигналом «блоифонка, приходящим с выхода реверсивного счетчика 8 в случае его нулевого состояния на блокировочный вход блока вычита ня 7.

Во втором случае блок вычнтання 7 сбрасывается в исходное состояние, и вследствие этого прекращается процесс вычитания. В момент сброса блок ныинтання 7 нч управляющем выходе вьфабатывает короткий управляющий импульс, который, поступая на второй упраатяющнй вход фазового дискриминатора 6, оказывает на последний такое же воздействие, как любой импульс считывания.

Таким образом, предлагаел5ын регенератор приемника импульсной стартстопно-синхронной системы обеспечивает формирование удлиненных стоповых 1 осылок, длительность которых более длительности элементарной посылки, что приводит к повышению помехоустойчивостн приема стартстопных комбинаций.

Формула изобретения

Регенератор прие.-;ника стартстопиых телеграфных сигналов, содержащий формирователь входных сигналов, на управляющий вход которого поданы управляющие импульсы, и последовательно соединенные делитель частоты, на управляю ций вход которого поданы тактовые импульсы, счетчик и спусковое реле, к другому входу которого подключен БЫход блока коррекцни, причем выход спускового реле подьу ючен к другому входу счетчика, а выход делителя частоты подключен к тактовоглу зходу блока коррекции, отличающийся тем, что, с целью повышения помехоустойчивости: нуте.м регенерации стоповой посылки телеграфных сигналов, введены фазовый дискримннатор, блок вычитания, реверсивныН счетчик, блок совпадения и блок эластичной памяти, при этом между выходом формирователя входны.х сигналов и информационным входсм блока коррекции включен блок эластичной памяти, выход которого через блок вычитания подключен ко входу фазового днскриминатора и к вычитающему входу реверсивного счетчика, к суммирующему входу которого подключен выход фазового дискриминатора, выход реверсивиого счетчика подключен к другому входу блока,вычитания и к соответствующему 19холу блока эластичной памяти, а выходы счетчика и блока коррекции подключены соответственйо ко входам блока совпадения, выход которого Подключен к соответствующему входу блока вычитания и к дополнительному входу делителя частоты, выход которого подключен к соответствующему входу фазового дискриминатора, причем на управляющие моды фазового дискриминатора и

блока эластичной памяти поданы управляющие импульсы, а на тактовый вход блЬка вычитания соответственно тактовые импульсы.

Источники информации, принятые во внимание при экспертизе: ,

1.Заявка № 2149443/09. кл. Н 04 Q 11/04, 1975. по которой выдано положительное рещение о выдаче авторского свидетельства.

2.Ушаков В. А. и др. Проводная связь. М.. «Связь. 1974. с. 199-200.

| название | год | авторы | номер документа |

|---|---|---|---|

| Регенератор стартстопных телеграфныхСигНАлОВ | 1979 |

|

SU815956A1 |

| Устройство для формированияиСпыТАТЕльНОгО TEKCTA | 1979 |

|

SU803118A1 |

| Устройство для фазирования электронного стартстопного регенератора | 1982 |

|

SU1073896A1 |

| Регенератор двоичных сигналов | 1978 |

|

SU703914A1 |

| Дискретный синхронизатор | 1973 |

|

SU516172A1 |

| Стартстопное приемное устройство | 1979 |

|

SU788423A1 |

| Электронное синхронное телеграфное устройство | 1978 |

|

SU860331A2 |

| Электронный распределитель | 1984 |

|

SU1170625A2 |

| Устройство выделения тактовых импульсов | 1982 |

|

SU1062880A1 |

| Устройство для сопряжения передатчика стартстопного телеграфного аппарата с синхронным распределителем | 1955 |

|

SU105482A1 |

IhpaS/vMufJt

HtUUfbtU

ПтаШ

UHnff tttl

Авторы

Даты

1979-01-05—Публикация

1976-10-14—Подача