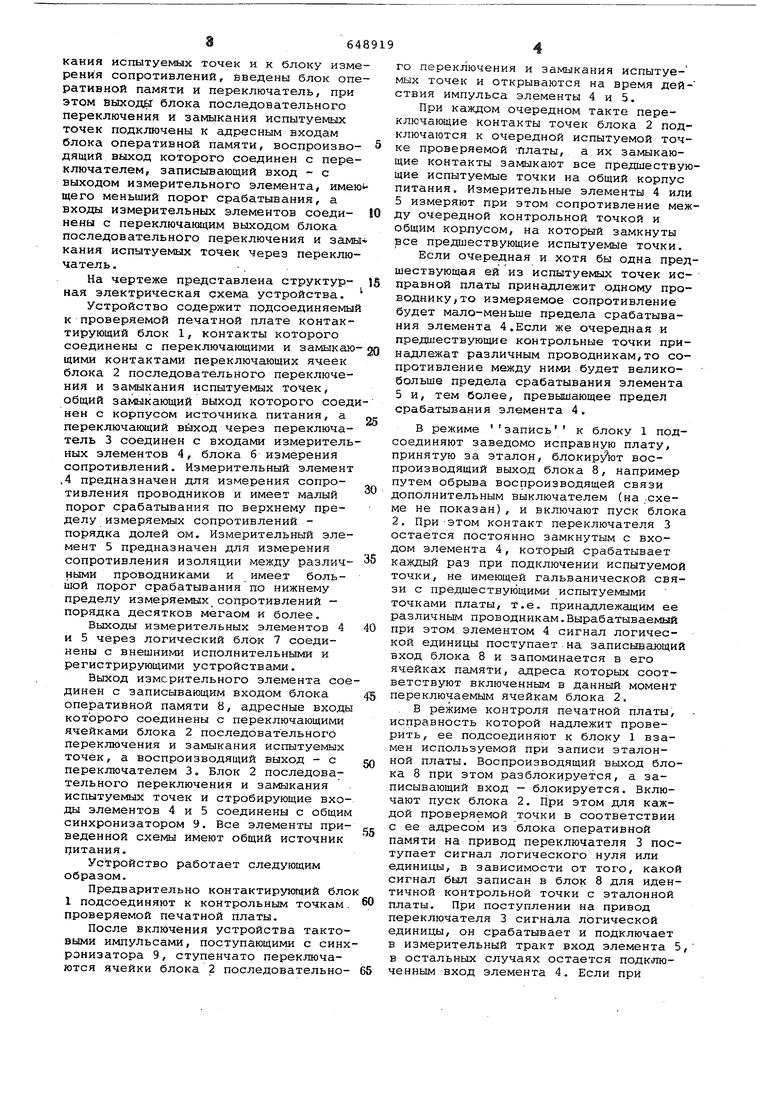

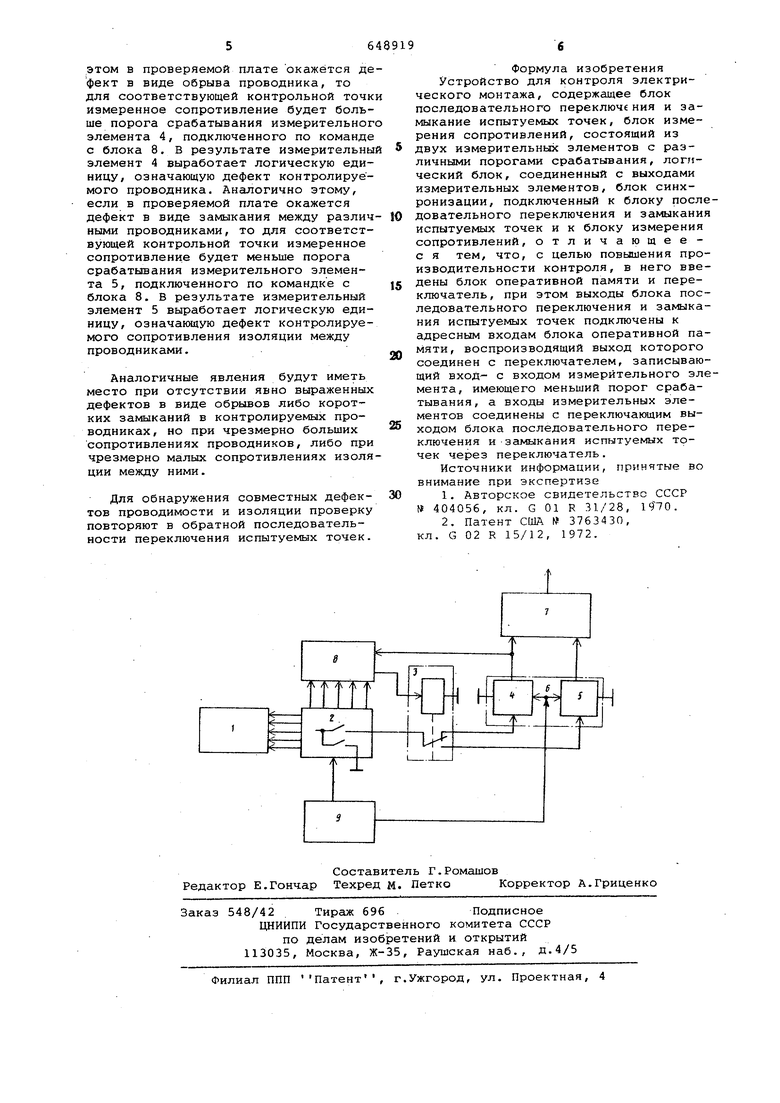

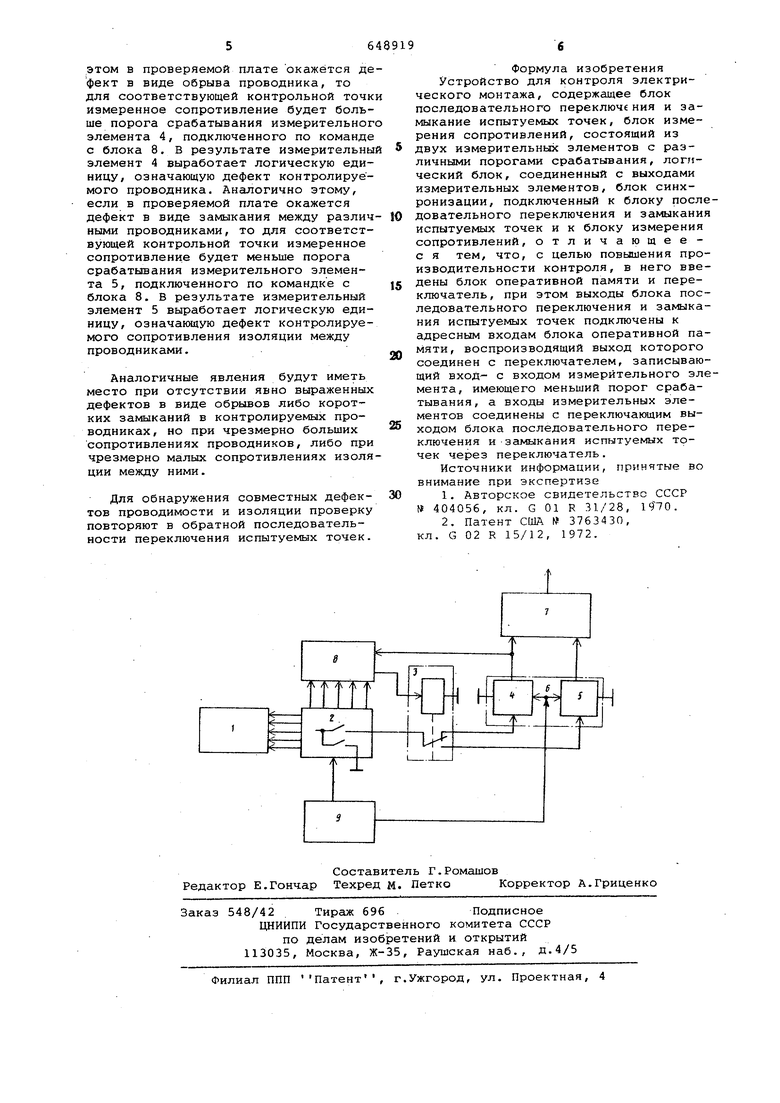

а6 камня испытуемых точек и к блоку изм рения сопротивлений, введены блок оп ративной памяти и переключатель, при этом выхода блока последовательного переключения и замыкания испытуемых точек подключены к адресным входам блока оперативной памяти, воспроизво дящий выход которого соединен с пере ключателем, записывающий вход - с выходом измерительного элемента, име щего меньш:ий порог срабатывания, а входы измерительных элементов соедийены с переключающим выходом блока последовательного переключения и зам кания испытуемых точек через переклю чатель. На чертеже представлена структурная электрическая схема устройства. Устройство содержит подсоединяемы к проверяемой печатной плате контактирующий блок 1, контакты которого соединены с переключающими и замыкаю щими контактами переключающих ячеек блока 2 последовательного переключения и замыкания испытуемых точек, общий замыкающий выход которого соед нен с корпусом источника питания, а переключающий выход через переключатель 3 соединен с входами измеритель ных элементов 4, блока б измерения сопротивлений. Измерительный элемент ,4 предназначен для измерения сопротивления проводников и имеет малый порог срабатывания по верхнему пределу измеряемых сопротивлений порядка долей ом. Измерительный элемент 5 предназначен для измерения сопротивления изоляции между различными проводниками и имеет большой порог срабатывания по нижнему пределу измеряемых сопротивлений - порядка десятков мегаом и более. Выходы измерительных элементов 4 и 5 через Логический блок 7 соединены с внешними исполнительныгли и регистрирующими устройствами. Выход измерительного элемента сое динен с записывающим входом блока оперативной памяти 8, адресные входы которого соединены с переключающими ячейками блока 2 последовательного переключения и замыкания испытуемых точек, а воспроизводящий выход - с переключателем 3, Блок 2 последовательного переключения и замыкания испытуемых точек и стробирующие входы элементов 4 и 5 соединены с общим синхронизатором 9. Все элементы приведенной схемы имеют общий источник цитания. Устройство работает следующим образом. Предварительно контактируютий бло 1 подсоединяют к контрольным точкам проверяемой печатной платы. После включения устройства такто выми импульсами, поступающими с синх ронизатора 9, ступенчато переключаются ячейки блока 2 последовательного переключения и замыкания испытуемых точек и открываются на время действия импульса элементы 4 и 5, При каждом очередном такте переключа шцие контакты точек блока 2 подключаются к очередной испытуемой точке проверяемой Платы, а их замыкающие контакты замыкают все предшествующие испытуемые точки на общий корпус питания. Измерительные элементы 4 или 5 измеряют при этом сопротивление между очередной контрольной точкой и общим корлусом, на который замкнуты все предшествующие испытуемые точки. Если очередная и хотя бы одна предшествующая ей из испытуемых точек исправной платы принадлежит одному проводнику, то измеряемое сопротивление будет мало-меньше предела срабатывания элемента 4.Если же очередная и предшествующие контрольные точки принадлежат различным проводникам,то сопротивление между ними-будет великобольше предела срабатывания элемента 5 и, тем более, превышающее предел срабатывания элемента 4. В режиме запись к блоку 1 подсоединяют заведомо исправную плату, принятую за эталон, блокир ют воспроизводящий выход блока 8, например путем обрыва воспроизводящей связи дополнительным выключателем (на ,-схеме не показан), и включают пуск блока 2, При-этом контакт переключателя 3 остается постоянно замкнутым с входом элемента 4, который срабатывает каждый раз при подключении испытуемой точки, не имеющей гальванической связи с предшествунзщими испытуемыми точками платы, т.е. принадлежащим ее различным проводникам.Вырабатываемый при этом, элементом 4 сигнал логической единицы поступает.на записывающий вход блока 8 и запоминается в его ячейках памяти, адреса которых соответствуют включенным в данный момент переключаемым ячейкам блока 2. . В режиме контроля печатной платы, исправность которой надлежит проверить, ее подсоединяют к блоку 1 взамен используемой при записи эталонной платы. Воспроизводящий выход блока 8 при этом разблокируешься, а записывающий вход - блокируется, включают пуск блока 2. При этом для каждой проверяемой точки в соответствии с ее адресом из блока оперативной памяти на привод переключателя 3 поступает сигнал логического нуля или единицы, в зависимости от того, какой сигнал был записан в блок 8 для идентичной контрольной точки с эталонной платы. При поступлении на привод переключателя 3 сигнала логической единицы, он срабатывает и подключает в измерительный тракт вход элемента 5, в остальных случаях остается подключенным вход элемента 4. Если при

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электрического монтажа печатных плат | 1977 |

|

SU783722A2 |

| Устройство для контроля электрического монтажа | 1981 |

|

SU968772A2 |

| Устройство для контроля электрического монтажа | 1988 |

|

SU1626224A2 |

| Способ контроля сопротивления изоляции | 1978 |

|

SU1045166A1 |

| Устройство для контроля монтажных схем | 1980 |

|

SU920747A1 |

| Устройство для автоматической проверки правильности электромонтажа | 1985 |

|

SU1296966A1 |

| Устройство для контроля монтажных схем | 1981 |

|

SU1018062A1 |

| Устройство для контроля печатных плат | 1975 |

|

SU549757A1 |

| Устройство для контроля электрических цепей | 1985 |

|

SU1357883A1 |

| Устройство для контроля печатных плат | 1973 |

|

SU470944A1 |

Авторы

Даты

1979-02-25—Публикация

1975-12-29—Подача