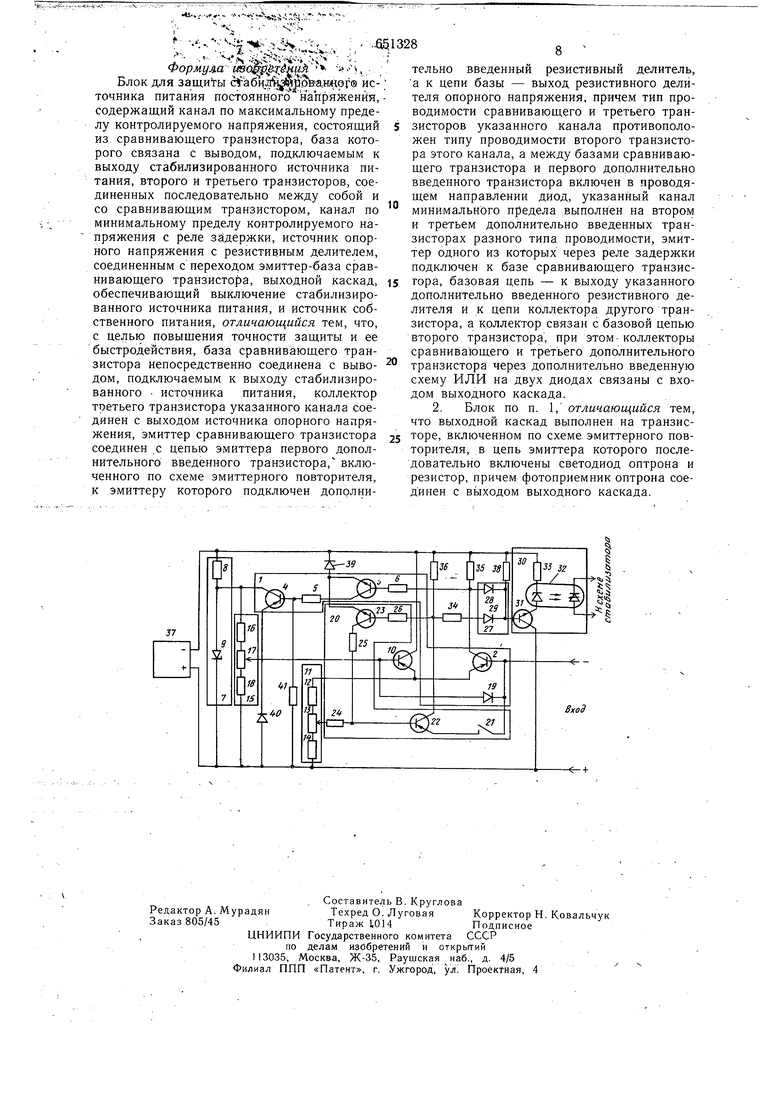

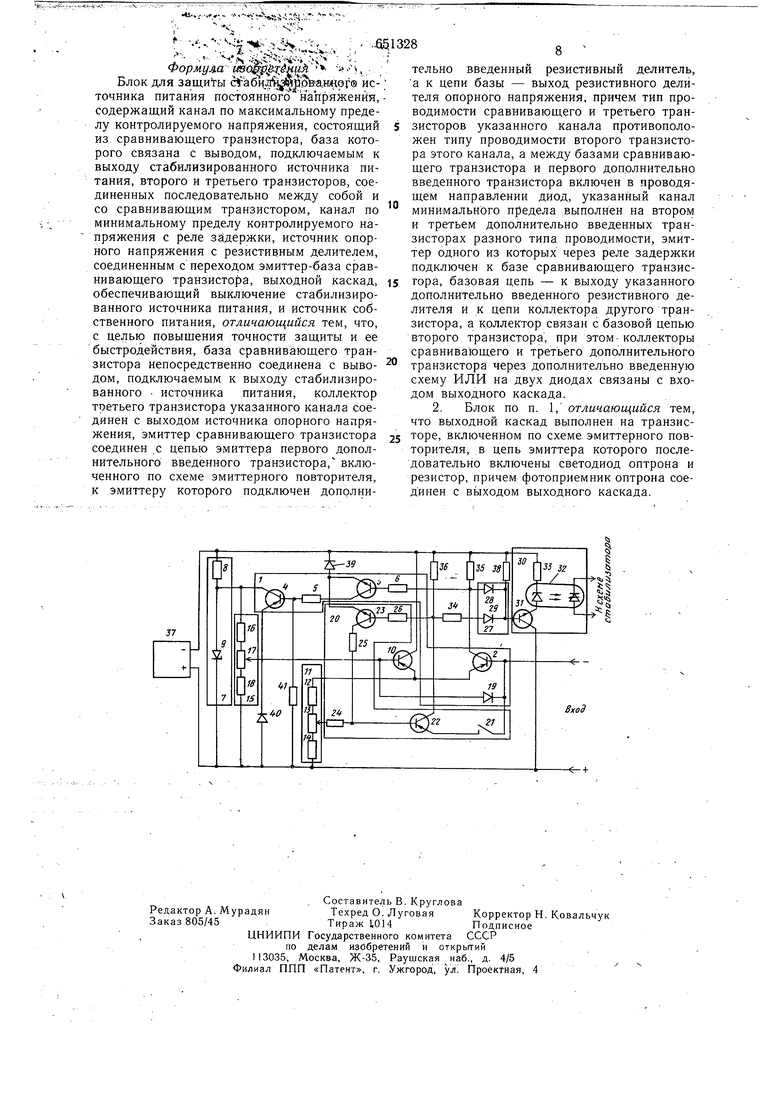

в линейном режиме. И хотя введенная в STOT усилитель постоянного тЬка отрицательная обратная связь повышает стабильность коэффициента усиления, ее нельзя сделать достаточно большой, так как при этом соответственно понижается чувствительность защиты. Недостаточное быстродействие рассмотренного устройства обусловлено тем, что регенеративный процесс происходит только в схеме с двумя устойчивыми состояниями и не распространяется на усилитель постоянного тока. Целью изобретения является повышение точности защиты и ее быстродействия. Цель достигается тем, что в блоке для защиты стабилизированного источника питания, содержащем канал по максимальному пределу контролируемого напряжения, состоящий из сравнивающего транзистора, база которого связана с выводом, подключаемым к выходу стабилизированного источника питания, второго и третьего транзисторов, соединенных последовательно между собой и со сравнивающим транзистором, канал по минимальному пределу контролируемого напряжения с реле задержки, источник опорного напряжения с резистивным делителем, соединённым с переходом эмиттер-база сравнивающего транзистора, выходной каскад, обеспечивающий выключение стабилизированного источника питания, и источник собственного питания, база сравнивающего транзистора непосрё/(ствённо соединена с выводом, подключаемым к выходу стабилизированного источника питания, коллектор третьего транзистора указанного канала связан с выходом источника Опорного напряжения, эмиттер сравнивающего транзистора соединен с цепью эмиттера первого дополнительного введенного транзистора, включенного по схеме эмиттерного повторителя, к эмиттеру которого подключен дополнительно введенный резистивный делитель, а к цепи базы - выход рёзистивного делителя опорного напряжения, причем тип проводимости сравнивающего и третьего транзисторов указанного канала противоположен типу проводимости второго транзистора этого канала, а между базами сравнивающего транзистора и первого дополнительно введенного транзистора включен в проводящем направлении диод, указанный канал минимального предела выполнен на втором и третьем дополнительно введенных транзисторах разного типа проводимости, эмиттер одного из которых через реле задержки подключен к базе сравнивающего транзистора, базовая цепь - к выходу указанного допрлнительно BBeAeHHOifo резйстйвн ОТО делиГтёля и цепи коллектора другого транзистора, а коллектор связан с базовой цепью второго транзистора, при этом коллекторы сравнивающего и третьего дополнительного транзистора через дополнительно введенную схему ИЛИ на двух диодах соединены с вхо-, дом выходного каскада. При этом выходной каскад может быть выполнен на транзисторе, включенном по Схеме эмиттерного повторителя, в цепь эмиттера которого последовательйо включены светодиод оптрона и резистор, причем фотоприемник оптрона соединен с выходом выходного каскада. На чертеже представлена электрическая схема блока для защиты стабилизированного источника питания. Блок содержит канал 1 по максимальному пределу контролируемого напряжения, состоящий из сравнивающего транзистора 2, база которого непосредственно соединена с выводом, подключаемым к выходу стабилизированного источника питания, второго и третьего л-ранзисторов 3 и 4, соединенных последовательно через резистор 5 между собой и через резистор 6 с коллектором транзистора 2, причем коллектор транзистора 4 соединен с выходом источника 7 опорного напряжения, образованного последовательно соединенными резистором 8 и стабилитроном 9, эмиттер сравнивающего транзистора 2 сое динен с эмиттером первого дополнительно введенного транзистора 10, включенного по схеме эмиттерного повторителя, к эмиттеру которого подсоединен дополнительно введенный резистивный делитель 11, составленный из резисторов 12-14, а к цепи базы - выход рёзистивного делителя 15 опорного напряжения, образованного резисторами 16- 18 и подключенного к выходу источника 7 опорного напряжения, диод 19, включенный между базами сравнивающего транзистора 2 и первого дополнительно введенного транзистора 10 и канала. 20 по минимальному пределу контролируемого напряжения. Канал 20 по минимальному пределу контролируемого напряжения содержит реле 21 задержки, второй и третий дополнительно введенные транзисторы 22 и 23, эмиттер транзистора 22 через реле 21 задержки подключен к базе сравнивающего транзистора 2, а база транзистора 22 через резисторы 24 и 25 соединены соответственно с выходом рёзистивного делителя 11 и коллектором транзистора 23. Коллектор транзистора 22 через резистор 26 соединен с базой транзистора 23. Коллекторы транзисторов 2 и 22 через схему ИЛИ 27, собранную на диодах 28 и 9, подключены к входу выходного каскада 30, выполненного на транзисторе 31, включенном по схеме эмиттерного повторителя, в цепь эмиттера которого последовательно включены светодиод оптронного тиристора 32 и резистор 33, причем фототирйстор ОПтрШа; соединен с выходом выходного каскада 30. Диод 29 схемы ИЛИ 27 подключен к транзистору 22 канала минимального предела через резистор 34. Коллекторы транзисторов 2 и 22 через резисторы 35 и 36 нагрузки подключены к источнику 37 собственного питания. Резистором нагрузки схемы ИЛИ 27 является резистор 38. Оба эмиттера транзисторов 3 и 23 и эмиттер транзистора 4 соединены с выходными цепями источника 37 соответств.енно через диоды 39 и 40. Между базой транзистора 4 и выводом диода 40, нротивоположным тому, который соединен с эмиттером транзистора 4, включен резистор 41. В спокойном состоянии транзисторы 2 . и 22 закрыты за счет разности величины напряжения контролируемого стабилизированного источника питания и пороговых напряжений соответственно по максимальному и минимальному пределам, из которых первое снимается со всей нагрузки (резисторы 12-14 делителя 11) эмиттерного повторителя на транзисторе 10, а другое с движка переменного резистора 13. Закрыты также и остальные транзисторы каналов максимального и минимального пределов: транзисторы 3 и 23 закрыты из-за того, что нет падения напряжения на резисторах 35 и 36 нагрузки, и в их эмиттерных цеПях включен диод 39 создающий нелинейную обратную связь по току за счет нелинейности внутреннего сопротивления диода, которое велико при малых токах и сравнительно мало на рабочем токе транзистора 3 или 23, а транзистор 4 закрыт из-за отсутствия тока через транзистор 3 и наличия в цепи его эмиттера и базы диода 40 и резистора 41. Уровни пороговых напряжений определяются величиной напряжения стабилитрона 9, коэффициентом деления делителя 15, коэффициентом передачи эмиттерного повторителя, собранного на транзисторе 10 и величиной участка отсутствия базового токана входной характеристике транзистора 2, а уровень порогового напряжения по минимальному пределу определяется коэффициентами деления делителей 11 и 15, коэффициентом передачи транзистора 10 и величиной участка отсутствия базового тока на входной характеристике транзистора 22. Если вследствие неисправности в контролируемом источнике напряжение на базе сравниваюшего транзистора 2 превысит напряжение по максимальному пределу, транзистор 2 открывается. Появляется падение напряжения на резисторе 35, которое прикладывается через резистор 6 и диод 39 к переходу база-эмиттер транзистора 3. Когда падение напряжения на резисторе 35 превысит сумму падения напряжения на ди-. оде 39 и величины напряжения перехода база-эмиттер транзистора 3 соответствующего участку отсутствия базового тока на его входной характеристике, транзистор 3 также отпирается и через диод 39, открытый транзистор 3 и резистор 5 на базу транзистора 4 начинает поступать ток, приводящий его в состояние проводимости. Теперь этот транзистор начинает подшунтировывать стабилитрон 9. Ток балластного резистора 8 идет уже не только через стабилитрон, но и через цепочку: транзистор 4, диод 40. И когда ток стабилитрона 9 становится меньше тока стабилизации, выходное напряжение делителя 15 будет уменьшаться, а следовательно, начнет уменьшаться и пороговое напряжение. Вследствие этого ток транзистора 2, а значит, и транзисторов 3 и 4 увеличится, что приведет к еш,е большему понижению порогового напряжения. Этот процесс носит, таким образом, лавинообразный регенеративный характер, охватываюший весь канал максимального предела. В ходе этого процесса схема практически мгновенно переходит во второе устойчивое COQтояние, при котором транзисторы 2-4 находятся в состоянии максимальной проводимости, а опорное напряжение отсутствует из-за закорачивания выхода источника 7 опорного напряжения транзистором 4 и диодом 40. Чтобы избежать излишнего превышения базового тока транзистора 2 при увеличении напряжения стабилизированного источника питания, которое может превысить номинальную величину в 1,5-2 раза, в канале максимального предела используется диод 19, который способствует выравниванию напряжений баз транзисторов 2 и 10 и, таким образом, ограничению базового тока транзистора 2. Напряжение с резистора 35 через диод 28 схемы ИЛИ 27, выделяясь на резисторе 38, прикладывается к базе транзистора 31 выходного каскада 30, в результате чего срабатывает тиристор 32 оптрона. Последний, будучи подключен к схеме стабилизированного источника Питания в тех точках, подключение к которым позволяет прекратить работу стабилизатора, обеспечивает отключение источника. В случае понижения напряжения контролируемого стабилизированного источника питания ниже порога по минимальному пределу, как и в канале максимального предела, появляется коллекторный ток транзистора 23, который, протекая через резистор 25 на базу транзистора 22, также вызывает лавинообразный регенеративный процесс канала минимального предела. Напряжение с резистора 36 через резистор 34 поступает на схему ИЛИ 27, что обеспечивает защиту по нижнему пределу. Наличие резистора 34 позволяет сохранить равенство величин тока светодиода оптрона как при работе канала максимального предела, так и минимального предела. Из рассмотренного принципа работы блока для защиты стабилизированного источника питания видно, что точность порогов его срабатывания повышена за счет уменьшения области линейного режима усиления транзисторов обоих каналов, а быстродействие - за счет полного охвата каналов регенеративным процессом. :- м ;;-;; :;-.:- .- N; Si . - ,v «iv - - Ж Формула «si Блок для защиты cf 6krf |i0fea,Keof® источника питания постоянного напряжения, содержащий канал по максимальному пределу контролируемого напряжения, состоящий из сравнивающего транзистора, база которого связана с выводом, подключаемым к выходу стабилизированного источника питания, второго и третьего транзисторов, соединенных последовательно между собой и со сравнивающим транзистором, канал по минимальному пределу контролируемого напряжения с реле задержки, источник опорного напряжения с резистивным делителем, соединенным с переходом эмиттер-база сравнивающего транзисто()а, выходной каскад, обеспечивающий выключение стабилизированного источника питания, и источник собственного питания, отличающийся тем, что, с целью повыщения точности защиты и ее быстродействия, база сравнивающего транзистора непосредственно соединена с выводом, подключаемым к выходу стабилизированного источника питания, коллектор третьего транзистора указанного канала соединен с выходом источника опорного напряжения, эмиттер сравнивающего транзистора соединен ,с цепью эмиттера первого дополнительного введенного транзистора, включенного по схеме эмиттерного повторителя, к эмиттеру которого подключен допрлни.55 8 тельно введенньгй резистивный делитель, а к цепи базы - выход резистивного делителя опорного напряжения, причем тип проводимости сравнивающего и третьего транзисторов указанного канала противоположен типу проводимости второго транзистора этого канала, а между базами сравнивающего транзистора и первого дополнительно введенного транзистора включен в проводящем направлении диод, указанный канал минимального предела выполнен на втором и третьем дополнительно введенных транзисторах разного типа проводимости, эмиттер одного из которых через реле задержки подключен к базе сравнивающего транзисгора, базовая цепь - к выходу указанного дополнительно введенного резистивного делителя и к цепи коллектора другого транзистора, а коллектор связан с базовой цепью второго транзистора, при этом- коллекторы сравнивающего и третьего дополнительного транзистора через дополнительно введенную схему ИЛИ на двух диодах связаны с входом выходного каскада. 2. Блок по п. 1, отличающийся тем, что выходной каскад выполнен на транзисторе, включенном по схеме эмиттерного повторителя, в цепь эмиттера которого последовательно включены светодиод оптрона и резистор, причем фотоприемник оптрона соединен с выходом выходного каскада.

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок для защиты стабилизированного источника питания постоянного напряжения | 1979 |

|

SU855843A2 |

| Селектор уровня постоянного напряжения | 1980 |

|

SU943683A1 |

| Устройство электропитания с самоконтролирующейся защитой | 1981 |

|

SU1026129A1 |

| Стабилизированный источник постоянногоНАпРяжЕНия или TOKA | 1979 |

|

SU845149A1 |

| Стабилизированный источник электропитания постоянного напряжения | 1979 |

|

SU769514A1 |

| Импульсный стабилизированный источникпОСТОяННОгО НАпРяжЕНия C зАщиТОй | 1979 |

|

SU845148A1 |

| Источник питания с защитой | 1977 |

|

SU693355A1 |

| Устройство электронной защиты | 1982 |

|

SU1136133A1 |

| Источник питания постоянного напряжения с защитой и фиксированной перестройкой | 1980 |

|

SU866554A1 |

| Самоконтролирующаяся система электропитания постоянного напряжения | 1981 |

|

SU1001298A1 |

Авторы

Даты

1979-03-05—Публикация

1974-12-25—Подача