(54) БЛОК ДЛЯ ЗАЩИТЫ СТАБИЛИЗИРОВАННОГО ИСТОЧНИКА ПИТАНИЯ ПОСТОЯННОГО НАПРЯЖЕНИЯ

1

Изобретение относится к технике электропитания радиоэлектронной аппаратуры, в частности к устройствам защиты стабилизаторов постоянного напряжения.

По основному авт. св. № 651328 известен блок для защиты стабилизированного источника питания постоянного напряжения, содержащий канал по максимальному пределу контролируемого напряжения, состоящий из сравнивающего транзистора, база которого связана с выводом, подключаемым к выходу стабилизированного источника питания, второго и третьего транзисторов, соединенных последовательно между собой и со сравниваю1дим транзистором, канал по минимальному пределу контролируемого напряжения с реле задержки, источник опорного напряжения с резистивным делителем, соединенным с переходом эмиттер база сравнивающего транзистора, выходной каскад, обеспечивающий выключение стабилизированного источника питания, и источник собственного питания, база сравнивающего транзистора непосредственно соединена с выводом, подключаемым к выходу стабилизированного источника питания, коллектор третьего транзистора указанного канала соединен с вьаходом источника опорного напряжения, эмиттер сравнивающего транзистора соединен с цепью эмиттера первого дополнительно введенного транзистора, включенного по схеме эмиттерного повторителя, к эмиттеру которого подключен дополнительно введенный резистивный

10 делитель, а к цепи базы - выход реэистивного делителя опорного напряжения, причем тип проводимости сравнивающего и третьего транзисторов указанного канала противоположен

15 типу проводимости второго транзистора этого канала, а между базами сравнивающего транзистора и первого «дополнительно введенного транзистора включен в проводящем направлении

20 диод, указанный канал минимального предела выполнен на втором и третьем дополнительно введенных транзисторах разного типа проводимости, эмиттер одного из которых через реле задерж25ки подключен к базе сравнивающего тралзистора, базовая цепь - к выходу указанного дополнительно введенного резистивного делителя и к цепи коллектора другого транзистора, а кол30лектор связан с базовой цепью второХО транзистора, при этом коллекторы сравнивающего и третьего дополнительного транзистора через дополнительно введенную схему ИЛИ на двух диодах связаны с входами выходного каскада, выполненного на транзисторе включенном по схеме эмиттерного повторителя, в цепь эмиттера которого последовательно включены светодиод Ьптрона и резистоо. поичем фотоприемник оптрона соединен с выходом вы,ходного каскада 1.

Недостатком известного устройства является отсутствие быстродействующего демпфирования контролируемого сточника питания постоянного напрях ения при возникновении в нем неисправности, приводящей к превышению его выходного напряжения.

Цель изобретения - расширение функциональных возможностей путем обеспечения быстродействующето дех шфирования контролируемого источнике питания постоянного напряжения при зозникновении в нем неисправности, приводящей к превышению его выходного напряжения.

Поставленная цель достигается тем, что в блок для защиты стабилизированного источника питания постоянного напряжения введен узел демпфирования, состоящий из цепочки последовательно включенных резистора и фОтоприемника оптрона, противоположные выводы которой подключены параллельно выводам, подключаемым к выход стабилизированного источигжа питания а светодиод оптрона включен последовательно между коллектором третьего транзистора канала максимального предела и выходом источника опорного напряжения, кроме того в узехг демпфирования введены два резистора и транзистор, причем резистор упомянутой цепочки узла демпфирования подключен к одному из выводов для Подключения к стабилизированному источнику питания через переход база эмиттер транзистора, коллектор которого через первый резистор подключен к другому выводу для подключения к стабилизированному источнику питания а параллельно переходу база - эмиттер транзистора включен второй резистор ,

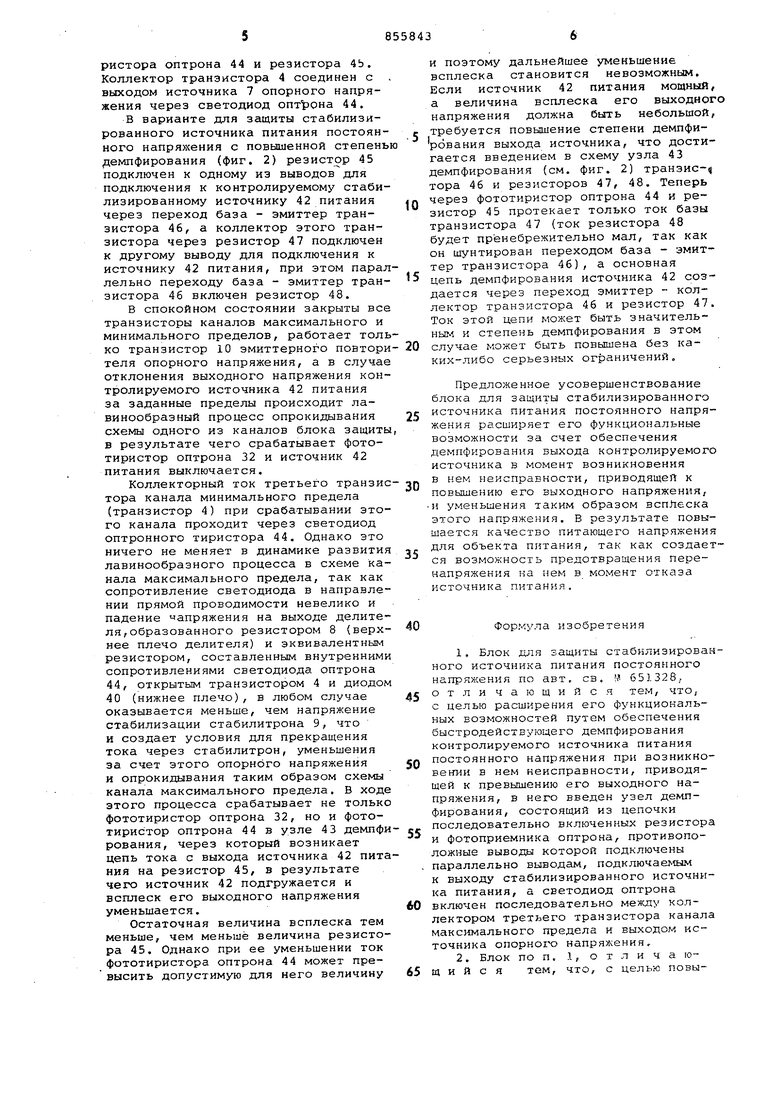

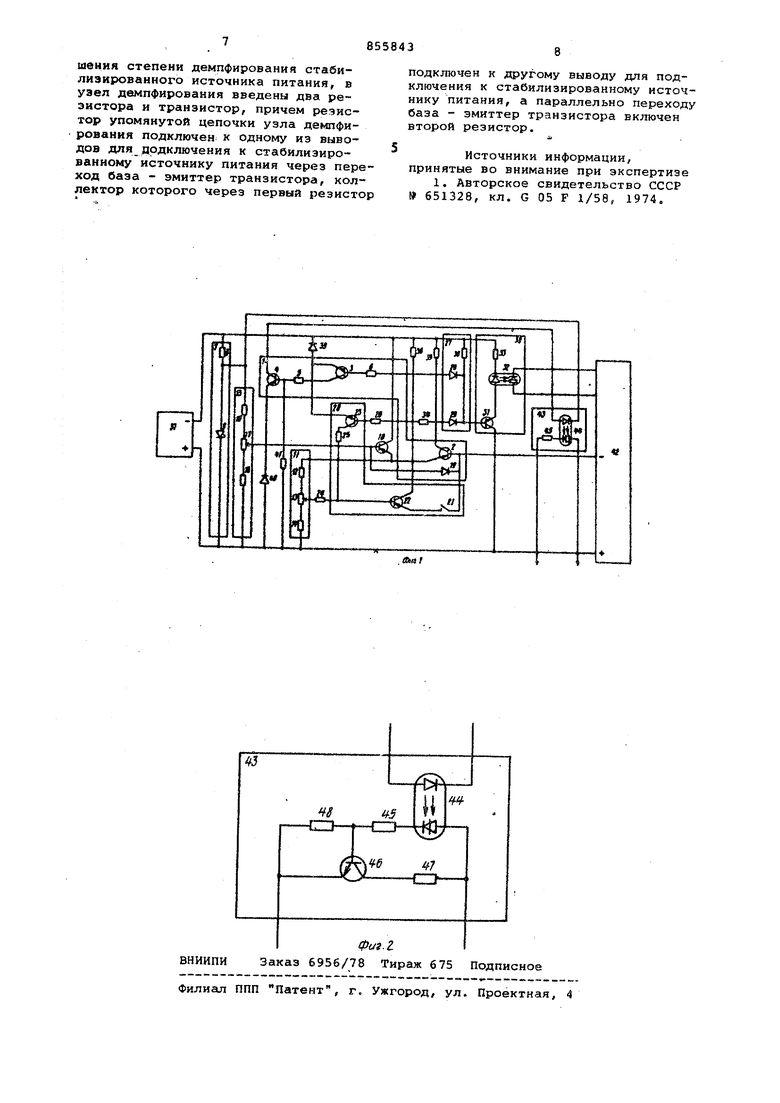

На фиг о 1 представлена схема блока для за111иты стабилизированного источника питания постоянного напряжения на фиг. 2 - развитие демпфирующего устройства этого блока для повышения степени демпфирования.

Блок содержит канал 1 по максимальному пределу, состоявдий из сравнивающего транзистора 2, база которого непосредственно соединена с выводом, подключаемая. к выходу стабилизированного источника питания, второго и третьего транзисторов 3 и 4, соединенных последовательно через резистор 5 между собой и через резистор 6 с коллектором транзистора 2. Источник 7 опорного напряжения образован последовательно соединенными резистором 8 и стабилитроном 9, Эмиттер сравнивающего транзистора 2 соединен с эмиттером транзистора 10, Ьключенного по схеме змиттерного повторителя, к эмиттеру которого подключен резистивный делитель 11, , составленный иэ резисторов 12-14, а к цепи базы - выход резистивного делителя 15 опорного напряжения,образованного резисторами 16 - 18, подключен выход источника 7 опорного напряжения. Между базами сравнивающего транзистора 2 и транзистора 10 включен диод 19,, Канал 20 по минимальному пределу содержит реле 21 задерш и и транзисторы 22 и 23. Эмиттер транзистора 22 через реле 21

0 задержки подключен к базе -сравнивающего транзистора 2, а база транзистора 22 через резисторы 24 и 25 соединена соответственно о выходом резистивного делителя 11 и коллекg тором транзистора 23. Коллектор транзистора 22 через резистор 26 соединен с базой транзистора 23. Коллекторы транзисторов 2 и 22 через схему 27 ИЛИ, собранную на диадах 28 и 29, подключены ко входу выходного каскада 30, выполненного на транзисторе 31, включенном по схеме эмиттерного повторителя, в цепь эмиттера которого последовательно включены светодиод оптрона 32 и резистор 33, причем фотоприемник (фототиристор) оптрона соединен с выходом выходного каскада 30. Диод 29 схемы 27 ИЛИ подключен к транзистору 22 канала минимального предела через резистор 34,- Коллекторы транзисторов 2 и 22 , через резисторы нагрузки 35 и 3.6 подключены к источнику 37 собственного питания. Резистором нагрузки схемы 27 ИЛИ является резистор 38.

j Оба эмиттера транзисторов 3 и 23 и эмиттер транзистора 4 соединены с выходны1у1и цепями источника 37 соответственно через диоды 39 и 40, Между базой транзистора 4 и выводом диода 40, противоположньзм тому, который соединен с эмиттером транзистора 4, включен резистор 41.

Фототиристор оптрона 32 выходного каскада 30 соедашен с точками контролируемого стабилизированного источника 42 питания постоянного напряже- ния, подключение к которым позволяет прекратить его работу при срабатывании фототиристора. Выход источника 42 питания подключен к объекту питания, к канал;ам максимального 1 и минимал1 ного 20 пределов блока эащяты и к узлу 43 деКтфирования, в котором он подключен параллельно цепочке, состоящей из последователь-, но соединенных между собой фототиристора оптрона 44 и резистора 4Ь. Коллектор транзистора 4 соединен с выходом источника 7 опорного напряжения через светодиод оптрона 44. В варианте для защиты стабилизированного источника питания постоян ного напряжения с повышенной степен демпфирования (фиг. 2) резистор 45 подключен к одному из выводов для подключения к контролируемому стаби лизированному источнику 42 питания через переход база - эмиттер транзистора 46, а коллектор этого транзистора через резистор 47 подключен к другому выводу для подключения к источнику 42 питания, при этом пара лельно переходу база - эмиттер тран зистора 46 включен резистор 48. В спокойном состоянии закрыты вс транзисторы каналов максимального и минимального пределов, работает тол ко транзистор 10 эмиттерного повтор теля опорного напряжении, а в случа отклонения выходного напряжения кон тролируемого источника 42 питания за заданные пределы происходит лавинообразный процесс опрокидывания схемы одного из каналов блока защиты в результате чего срабатывает фототиристор оптрона 32 и источник 42 питания выключается. Коллекторный ток третьего транзис тора канала минимального предела (транзистор 4) при срабатывании этого канала проходит через светодиод оптронного тиристора 44. Однако это ничего не меняет в динамике развития лавинообразного процесса в схеме канала максимального предела, так как сопротивление светодиода в направлении прямой проводимости невелико и падение напряжения на выходе делителя,образованного резистором 8 (верхнее плечо делителя) и эквивалентныь1 резистором, составленным внутренними сопротивлениями светодиода оптрона 44, открытым транзистором 4 и диодом 40 (нижнее плечо), в любом случае оказывается меньше, чем напряжение стабилизации стабилитрона 9, что и создает условия для прекращения тока через стабилитрон, уменьшения за счет этого опорного напряжения и опрокидывания таким образом схемы канала максимального предела. В ходе этого процесса срабатывает не только фототиристор оптрона 32, но и фототиристор оптрона 44 в узле 43 демпфи рования, через который возникает цепь тока с выхода источника 42 пита ния на резистор 45, в результате чего источник 42 подгружается и всплеск его выходного напряжения уменьшается. Остаточная величина всплеска тем меньше, чем меньше величина резистора 45. Однако при ее уменьшении ток фототиристора оптрона 44 может превысить допустимую для него величину и поэтому дальнейшее уменьшение всплеска становится невозможным. Если источник 42 питания мощный, а величина всплеска его выходного напряжения должна быть небольшой, требуется повышение степени демпфирования выхода источника, что достигается введением в схему узла 43 демпфирования (см. фиг. 2) транзистора 46 и резисторов 47, 48. Теперь через фототиристор оптрона 44 и резистор 45 протекает только ток базы транзистора 47 (ток резистора 48 будет пренебрежительно мал, так как он шунтирован переходом база - эмиттер транзистора 46), а основная цепь демпфирования источника 42 создается через переход эмиттер - коллектор транзистора 46 и резистор 47. Ток этой цепи может быть значительным и степень демпфирования в этом случае может быть повышена без каких-либо серьезных ог эаничений, Предложе иное усовершенствование блока для защиты стабилизированного источника питания постоянного напряжения расширяет его функциональные возможности за счет обеспечения демпфирования выхода контролируемого источника в момент возникновения в нем неисправности, приводящей к повьпдению его выходного напряжения, и уменьшения таким образом вспЛеска этого напряжения. В результате повышается качество питающего напряжения для объекта питания, так как создается возможность предотвращения перенапряжения ка нем в момент отказа источника питания. Формула изобретения 1.Блок xuiH защиты стабилизированного источника питания постоянного напряжения по авт. ев, f 651328, отличающийся тем, что, с целью расширения его функциональных возможностей путем обеспечения быстродействующего демпфирования контролируемого источника питания постоянного напряжения при возникновении в нем неисправности, приводящей к превышению его выходного напряжения, в него введен узел демпфирования, состоящий из цепочки последовательно включенных резистора и фотоприемника оптрона, противоположные выводы которой подключены параллельно выводам, пoдключae ым к выходу стабилизированного источника питания, а светодиод оптрона включен последовательно межлу коллектором третьего транзистора канала максимального предела и выходом источника опорного напряжения, 2.Блок по п. 1, о X л и ч а ющ и и с я тем, что, с целью повышения степени демпфирования стабилизированного источника питания, в узел демпфирования введены два резистора и транзистор, причем резистор упомянутой цепочки узла демпфирования подключен к одному из выводов для ярдключения к стабилизированному источнику питания через переход база - эмиттер транзистора, коллектор которого через первый резистор

подключен к другому выводу для подключения к стабилизированному источнику питания, а параллельно переходу база - эмиттер транзистора включен

второй резистор.

л

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР 651328, кл. G 05 F 1/58, 1974,

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок для защиты стабилизированного источника питания постоянного напряжения | 1974 |

|

SU651328A1 |

| Селектор уровня постоянного напряжения | 1980 |

|

SU943683A1 |

| Двухполярный стабилизированный источник питания | 1985 |

|

SU1334123A1 |

| Устройство для контроля уровня напряжения источника постоянного тока | 1986 |

|

SU1332296A1 |

| Импульсный стабилизированный источникпОСТОяННОгО НАпРяжЕНия C зАщиТОй | 1979 |

|

SU845148A1 |

| Источник питания постоянного напряжения с защитой и фиксированной перестройкой | 1980 |

|

SU866554A1 |

| Стабилизированный источник электропитания постоянного напряжения | 1979 |

|

SU769514A1 |

| Устройство электропитания с самоконтролирующейся защитой | 1981 |

|

SU1026129A1 |

| Двухполярный стабилизатор постоянного напряжения | 1990 |

|

SU1756873A1 |

| Стабилизированный источник постоянногоНАпРяжЕНия или TOKA | 1979 |

|

SU845149A1 |

Авторы

Даты

1981-08-15—Публикация

1979-05-03—Подача