I

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных системах, системах управления и передачи информации. Построение данного устройства, которое реализует алгоритм постановки сигналов в очередь, возможно в виде конечного автомата с памятыо.

Известен многоканальный блок приоритета, который содержит триггеры, логические схемы И, ИЛИ, НЕ, соединенные между собой определенным образом 1.

Недостатком известного устройства является использование не всей мощности множества входных сигналов.

Наиболее близким техническим решением предложенному является известный блок приоритета, содержащий первую группу элементов И, группу элементов НЕ, причем каждый вход элемента И первой группы соединен соответственно с одноименными входами группы входов устройства, вторые входы элементов И первой группы соединены соответственно с группой входов устройства, вторые входы элементов И первой группы соединены соответственно с выходами элементов НЕ первой группы 2.

Однако в многоканальном блоке приоритета можно указывать следуюпгие недостатки:

1) используется не вся мощность множества входных сигналов. Если на вход прищел сигнал xj и в очереди уже находились сигналы XK, то в дальнейшем будет производиться обслуживание только х, сигналов, если ,

2) после прихода сигнала по j-му каналу, дальнейший приоритет устанавливается в порядке возрастания номера канала (к j), а не в порядке времени прихода сигнала.

Целью настоящего изобретения является устранение указанных недостатков, а именно, расширение функциональных возможностей за счет установления приоритета по времени прихода сигнала.

Указанная цель достигается тем, что в блок приоритета введены вторая, третья, четвертая группы элементов И, вторая и третья группы элементов НЕ, причем входы элементов НЕ первой группы соединены соответственно с выходами элементов И второй группы, первые входы которых соединены соответственно с выходами элементов НЕ второй группы, выход элемента И первой группы соединен с первым входом одноименного элемента И третьей группы, входом одноименного элемента НЕ второй группы, с первыми и вторыми входами элементов И, кроме одноименного, четвертой группы элементов И, каждый выход элемента И третьей группы подключен ко входу одноименного элемента НЕ третьей группы и к одноименному выходу группы выходов устройства, выход каждого элемента НЕ третьей группы подключен к первым и вторым входам элементов И, кроме одноименного, третьей группы элементов И, выходы элементов И четвертой группы соединены соответственно со вторыми входами элементов И второй группы.

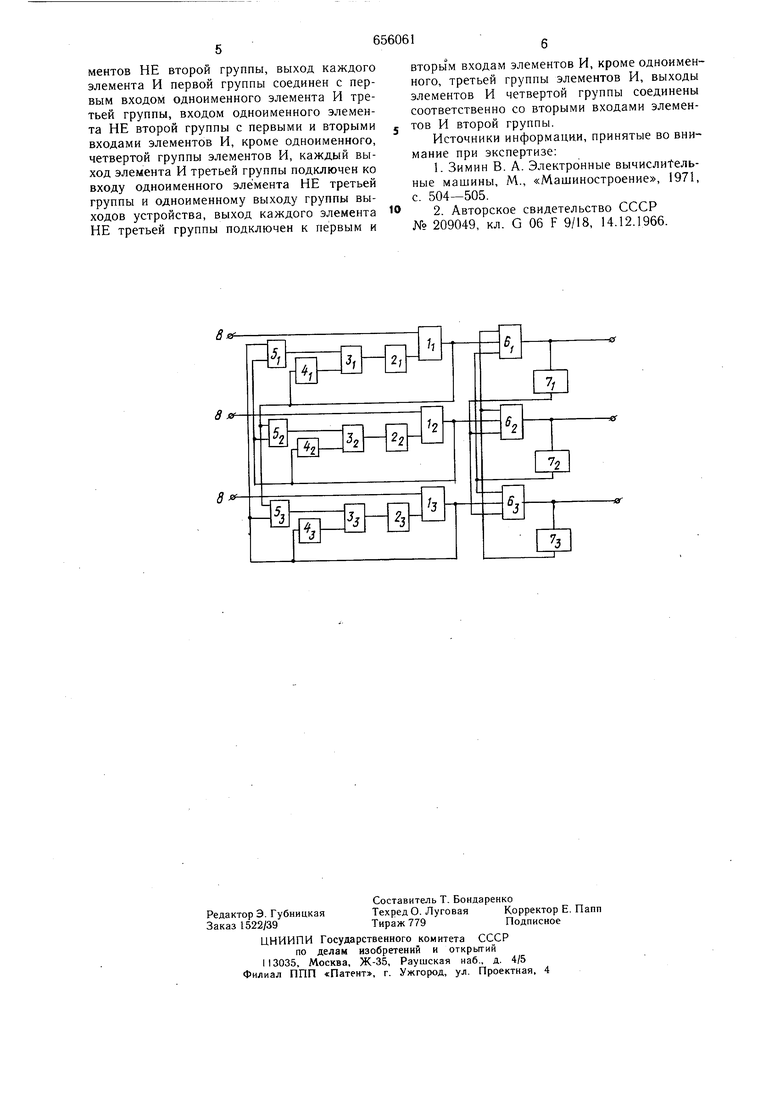

Схема блока динамического приоритета приведена на чертеже.

Элементы И первой группы 1, элементы НЕ первой группы 2, элементы И второй группы 3, элементы НЕ второй группы 4, элементы И четвертой группы 5, элементы И третье й группы 6, элементы НЕ третьей группы 7, группа входов устройства 8. Блок динамического приоритета функционирует следующим образом.

Заявки (xi , Хг, хз) поступают на соответствующие входы группы входов устройства, факт прихода заявки отождествляется с появлением потенциала на соответствующем входе. Рассмотрим работу блока на примере входной последовательности заявок вида: Xi,X2, Хз. Поток этих заявок полагается ординарным.

Работу блока удобно подразделить на 2 режима.

1. Режим постановки сигналов на очередь. Будем полагать, что к началу работы очередь была свободна.

X, проходит через элементы И, 1 и 6 к соответствующему выходу группы выходов устройства, так как в данный момент времени на выходах всех групп элементов НЕ (2;,, 4t, Tli-2,3 ) - единица. Пройдя к шине обслуживания х запрещает прохождение поступающих в дальнейщем сигналов через ба и , поскольку на выходе 7 -- 0. В то же время через обратную связь сигнал Xi запрещает появления «О на втором входе элемента И Ц , а также проходит на входы элементов И и .

Сигнал Лз проходит через элемент И 1з, так как на выходе - единица и занимает второе место Очереди, соответствующее входу элемента И . Через обратную связь Хз запрещает появление «О на втором входе элемента И 1з. Проходя на элемент И 5| и 5fe, сигнал Хз запрещает прохождение следующего сигнала через элемент И 1з так как на выходах элементов 4 - «1, следовательно на выходе 2 - «О. Для поступающего сигнала хг остается третье место очереди, соответствующее входу элемента Ig.

2. Режим сдвига. Этот режим начинается по окончанию обслуживания сигнала, стоящего на первом месте очереди. При этом обслуженный сигнал снимается (снимается также потенциал с соответствующей щины 1, 2, 3).

Пусть при состоянии очереди х, хi, Хз обслужен и снят сигнал х . В результате этого происходит освобождение первого места очереди. Сигнал хз выходит на первое

место очереди и запрещает прохождение последующих сигналов через элементы И 6| и 6i, поскольку на выходе, 7) - «О. В то же время, т. к. сигнал х i снят, на выходе 5i - «О. Следовательно, на выходе

За - «О и на выходе 2 - «1. Вследствие этого сигнал ха занимает второе место очереди, появляясь на выходе схемы U. Произощел сдвиг. Состояние очереди: хз- Х2,в Затем обрабатывается и снимается сигнал X 3 В результате этого освобождается

1-е место очереди, которое и занимает последний сигнал у.а,.

Предлагаемый блок динамического приоритета позволяет улучщить качество обработки информации в вычислительных системах в тех случаях, когда очередность обслуживания поступающих сообщений нельзя определить заранее. Например, при однотипных сообщениях рационально порядок их обслуживания соотносить с порядком прихода (с временем поступления). При

этом используется вся мощность множества входных сигналов и по сравнению с жесткой детерминированной системой приоритетов такой порядок обслуживания уменьшает время ожидания. Это определяет уменьщение общего времени пребывания сообщения в системе (применительно к цифровым вычислительным машинам (.ЦВМ), работающим в контурах управления), при этом уменьфается запаздывание.

Формула изобретения

Блок динамического приоритета, содержащий первую группу элементов И, группу

элементов НЕ, причем каждый вход элементов И первой группы соединен соответственно с одноименными входами группы входов устройства, вторые входы элементов И первой группы соединены соответственно с выходами элементов НЕ первой группы, оглычающийся, тем, что, с целью расширения функциональных возможностей за счет установления приоритета по времени прихода сигнала, в блок приоритета введены вторая, третья, четвертая группы элементов И.

вторая и третья группы элементов НЕ, причем входы элементов НЕ первой группы соединены соответственно с выходами элементов И второй группы, первые входы которых соединены соответственно с выходами элементов НЕ второй группы, выход каждого элемента И первой группы соединен с первым входом одноименного элемента И третьей группы, входом одноименного элемента НЕ второй группы с первыми и вторыми входами элементов И, кроме одноименного, четвертой группы элементов И, каждый выход элемента И третьей группы подключен ко входу одноименного элемента НЕ третьей группы и одноименному выходу группы выходов устройства, выход каждого элемента НЕ третьей группы подключен к первым и

вторь1м входам элементов И, кроме одноименного, третьей группы элементов И, выходы элементов И четвертой группы соединены соответственно со вторыми входами элементов И второй группы.

Источники информации, принятые во внимание при экспертизе:

1.Зимин В. А. Электронные вычиcлиteльные машины, М., «Машиностроение, 1971, с. 504-505.

2.Авторское свидетельство СССР № 209049, кл. G 06 F 9/18, 14.12.1966.

| название | год | авторы | номер документа |

|---|---|---|---|

| Поточно-параллельный процессор Хаара | 1989 |

|

SU1756901A1 |

| Устройство динамического приоритета | 1980 |

|

SU934475A1 |

| Многорежимное устройство динамического приоритета | 1984 |

|

SU1246095A1 |

| Многоканальное устройство приоритета | 1988 |

|

SU1580364A1 |

| Параллельный процессор Хаара | 1989 |

|

SU1667103A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Устройство для обслуживания запросов | 1987 |

|

SU1444768A1 |

| Многоканальное устройство для выбора задач на обслуживание | 1987 |

|

SU1444773A1 |

| Устройство для моделирования систем массового обслуживания | 1982 |

|

SU1067508A1 |

| Устройство для обслуживания запросов | 1987 |

|

SU1437864A1 |

Авторы

Даты

1979-04-05—Публикация

1977-03-14—Подача