Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств контроля и управления технологическими процессами цифровых систем с микропрограммным управлением.

Цель изобретения - расширение области применения и повышение быстродействия устройства.

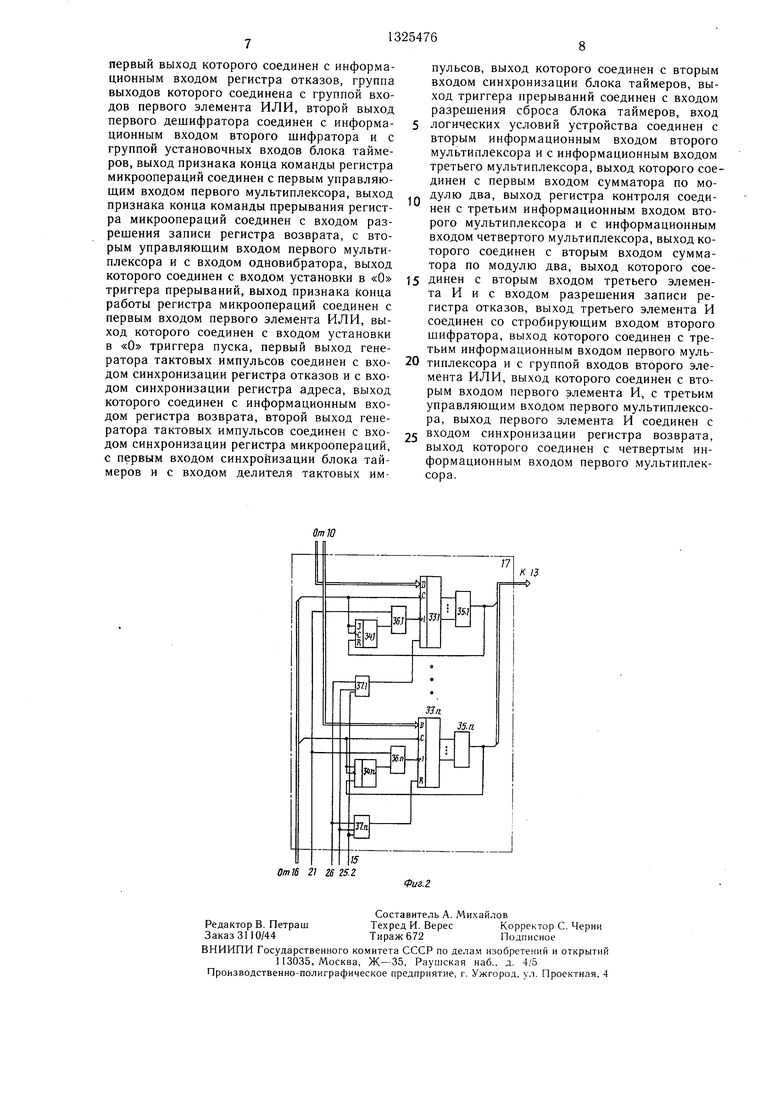

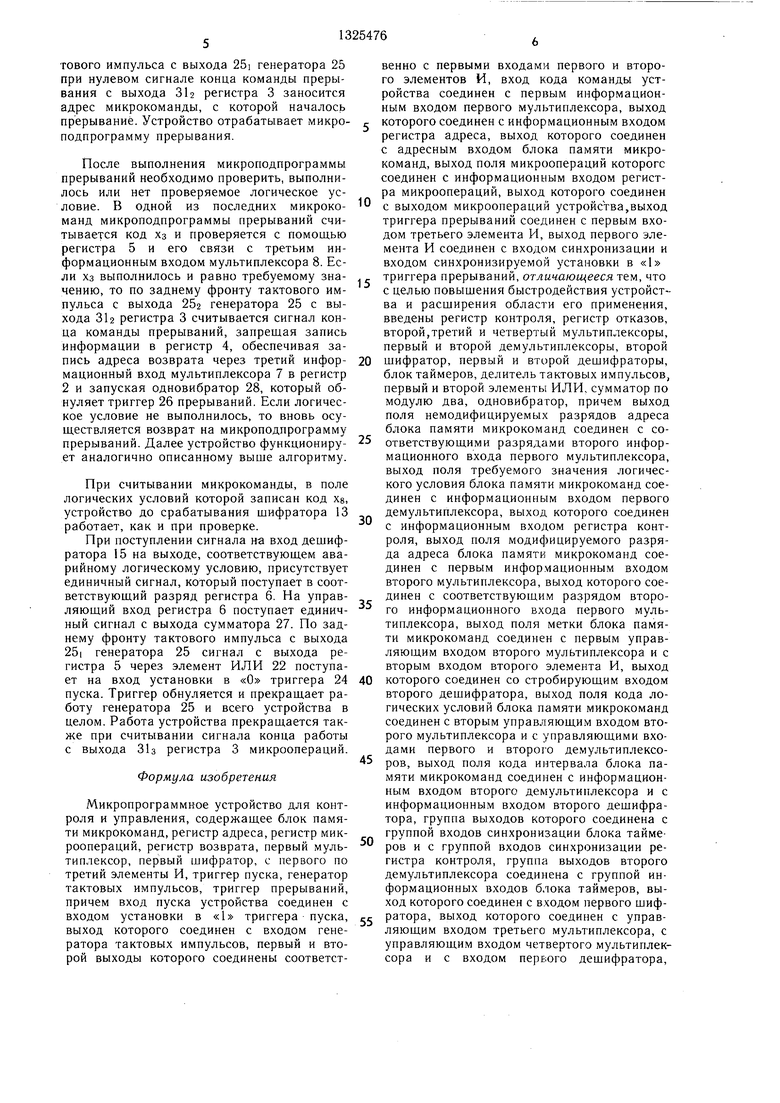

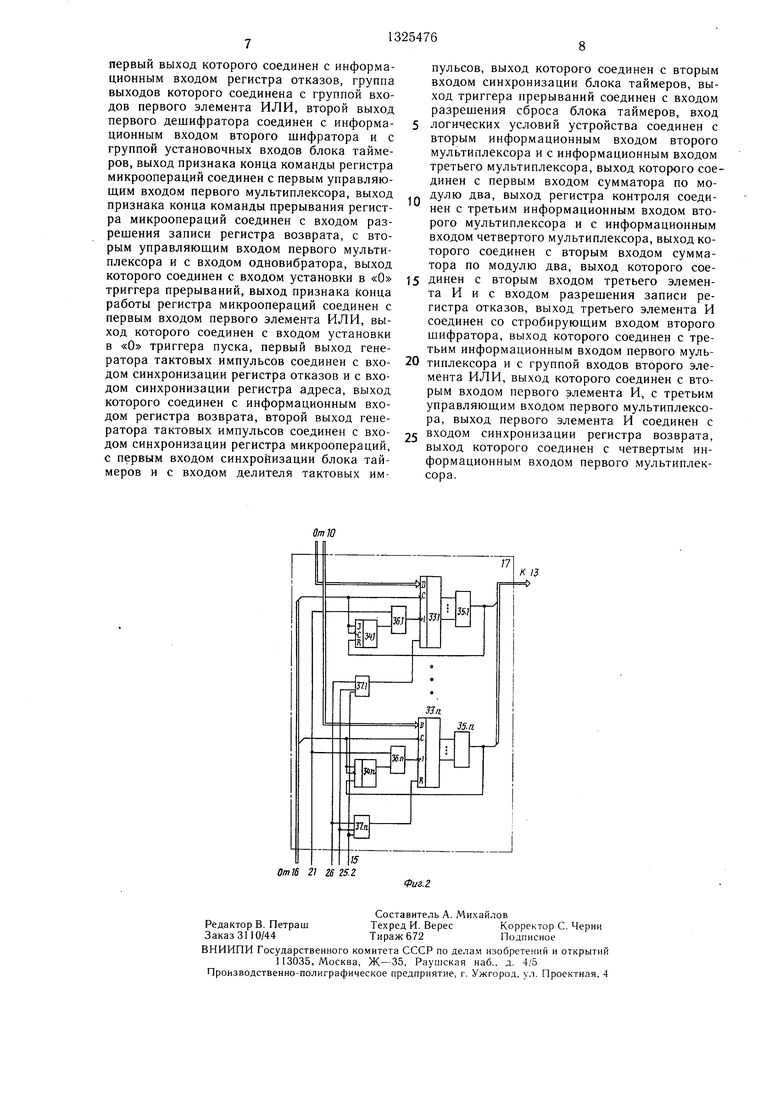

На фиг. 1 приведена функциональная схема микропрограммного устройства для контроля и управления; на фиг. 2 - функциональная схема блока таймеров.

Микропрограммное устройство для контроля и управления содержит блок 1 памяти микрокоманд с выходами поля старших (немодифицируемых) разрядов адреса очередной микрокоманды h, поля кода микроопераций 12, поля требуемого значения проверяемого логического условия Ь, поля младшего (модифицируемого) разряда адреса очередной микрокоманды Ь, поля значения метки Ь, поля кода проверяемого логического условия 1б, регистр 2 адреса, регистр 3 микроопераций, регистр 4 возврата, регистр 5 контроля, регистр 6 отказа, первый 7 и второй 8 мультиплексоры, первый 9 и второй 10 демультиплексоры, третий 11 и четвертый 12 мультиплексоры, первый 13 и второй 14 шифраторы, первый 15 и второй 16 дешифраторы, блок 17 таймеров, первый 18, второй 19 и третий 20 элементы И, делитель 21 тактовых импульсов, первый 22 и второй 23 элементы ИЛИ, триггер 24 пуска, генератор 25 тактовых импульсов с первым 25i и вторым 252 выходами, триггер 26 прерываний, сумматор 27 по модулю два, одновибра- тор 28, входы пуска 29 и кода операции 30 устройства, выход 31 микроопераций устройства (31i признака конца команды, ЗЬ признака конца команды прерываний, 31з - признака конца работы), вход 32 логических условий устройства.

Блок 17 таймеров содержит группу счетчиков 33i-ЗЗп, группу триггеров 34i - 34„, первую группу 35i - 35„ элементов И, вторую группу 36i - 37л элементов И.

Устройство работает следуюш,им образом.

Микропрограммное устройство для контроля и управления работает в режимах выполнения рабочей микропрограммы и отработки прерываний по непрерывно контролируемым логическим условиям (НКЛУ).

В режиме выполнения рабочей микропрограммы возможны реализация линейных микрокоманд, микрокоманд ветвления, постановка и снятие с контроля непрерывно контролируемых логических условий. При выполнении неаварийных НКЛУ устройство переходит к второму режиму работы, предназначенному для отработки микроподпрограммы прерываний до принятия контролируемым параметром нормального значения. При выполнении микроподпрограмм прерываний также возможны случаи реализации линейных микрокоманд и микрокоманд ветвления постановка и снятие с контроля НКЛУ. Но отработка микропрограммы прерываний в данном случае возможна лишь только после получения микрооперации конца прерываний микроподпрограммы отработки прерывания по предыдущему НКЛУ.

При отработке микроподпрограмм прерывания устройства осуществляется выход из второго режима. При выполнении аварийных НКЛУ устройство прекращает работу.

В исходном состоянии все элементы схемы приведены в «О. Только в разряде мик- рооперации, соответствующем выходу 311 регистра 3, записана «1 (цепи приведения в исходное состояние не показаны).

По сигналу «Пуск, поступающему на вход 29 устройства, триггер 24 пуска устанавливается в единичное состояние и гене- 0 ратор 25 начинает выработку тактовых сигналов. По первому тактовому импульсу с выхода 25i генератора 25 в регистр 2 заносится код команды с входа 30. Этот код записывается через мультиплексор 7 (через 5 его первый информационный вход) в регистр 2 при разрешающем сигнале с выхода 31: регистра 3. По коду, считанному из регистра 2, с блока 1 памяти выбирается микрокоманда.

Реализуемая микрокоманда - линейная. 0 Операционная часть кода линейной микрокоманды по заднему фронту второго тактового импульса с выхода 252 генератора 25 заносится в регистр 3 и на выход 31 устройства. Старшие (немодифицируемые) разряды адреса очередной микрокоманды с вы- 5 хода 11 блока 1 памяти поступают на соответствующие входы второго информационного входа мультиплексора 7, а младщий разряд адреса с выхода Ц блока 1 памяти поступает на адресный вход мульти плексора 8, с выхода которого (без изме0

нения I - на соответствующий вход второго

информационного входа мультиплексора 7. По заднему фронту очередного первого тактового импульса с выхода 25i генерато ра 25 с регистра 2 считывается код адс реса очередной микрокоманды, которая выбирается из блока 1 памяти микрокоманд. При реализации всех линейных микрокоманд устройство функционирует аналогично описанному выше алгоритму.

Реализуемая микрокоманда является мик0 рокомандой условного перехода.

Старшие разряды адреса очередной микрокоманды поступают на соответствующие входы мультиплексора 7. Операционная часть микрокоманды поступает в регистр 3 и на выход 31 микроопераций устройства.

5 Младщий разряд адреса очередной микрокоманды поступает на адресный вход мультиплексора 8. По коду логических условий, записанному в поле Ь блока 1 памяти, с входа 32 логических условий устройства мультиплексор 8 выбирает значение проверяемого логического условия. Младший разряд адреса очередной микрокоманды модифицируется значением этого логического условия и поступает на соответствующий вход второго информационного входа мультиплексора 7. При проверке микрокоманд ветвления устройство функционирует аналогично описанному выше алгоритму.

Работу устройства при реализации микрокоманд с непрерывно контролируемыми логическими условиями рассмотрим на сле- дуюшем примере.

Пусть в процессе выполнения микропрограммы вс его проверяется десять логических условий X {xi, Х2,..., Х|о}, среди которых xi, хз, Х8 и Хэ являются непрерывно контролируемыми, из них X| и хз являются неаварийными, а xg и хд - аварийными непрерывно контролируемыми логическими условиями. Таким образом, разрядность поля 1б блока 1 памяти микрокоманд равна четырем, количество таймеров в блоке 17 таймеров равно четырем, регистр 5 контроля является четырехразрядным, а регистр 6 отказа - двухразрядным. Из блока 1 памяти микрокоманд выбирается микрокоманда ветвления с непрерывно контролируемым логическим условием. В поле 1з блока памяти микрокоманд присутствует требуемое значение данного логического условия, в поле 1-., - единичное значение метки, в поле U - код этого условия, в поле Ь - дополнительный код определяющий максимальный интервал времени проверки At, в течение которого это условие должно выполняться. Пусть интервал времени равен 100 синхроимпульсам с выхода делителя 21 тактовых импульсов. Разрядность соответствующего таймера равна семи, он может принять 127 синхроимпульсов с выхода делителя 21, тогда At 27. Старшие разряды адреса очередной микрокоманды с выхода поступают на соответствующий вход мультиплексора 7. Код микроопераций с выхода Ь поступает в регистр 3 и на выход 31 устройства.

Требуемое значение логического условия поступает на информационный вход первого демультиплексора 9. Младщий разряд адреса очередной микрокоманды поступает на первый информационный вход мультиплексора 8, единичное значение метки - на его управляющий вход и на второй элемент И 19. Код непрерывно контролируемого логического условия хз с выхода le поступает на адресный вход мультиплексора 8 и на управляющие входы первого 9 и второго 10 демультиплексоров. Дополнительный код At с выхода Ь блока 1 памяти поступает на второй демультиплексор 10 и дещифратор 16 синхросигналов.

По коду логического условия хз с выхода 1б блока 1 памяти с входа 32 логических условий устройства выбирается его значение и поступает на вход мультиплексора 11 истинного значения логических условий. Требуемое значение логического условия с выхода 1з блока 1 памяти через первый демультиплексор 9, при управляющем воздействии кода логического условия Хз на его управляющий вход, заносится во второй разряд регистра 5 контроля. С выхода регистра 5 это значение поступает на соответствующий вход информационного входа мультиплексора 12. Код интервала времени 0011011, соответ5 ствующий «27, с выхода Ь блока памяти микрокоманд поступает на информационные входы второго демультиплексора 10 и дешифратора 16 синхросигналов. По коду интервала при разрешающем сигнале с выхода второго элемента И 10 дешифратор выби0 рает второй таймер (фиг. 2) и по заднему фронту синхроимпульса заносит в него код «27. Разрядность таймера (счетчика ЗЗз) равна 127, поэтому по приходу с выхода делителя 21 сотого синхроимпульса (т.е. пос5 те окончания времени проверки логического условия) с выхода блока таймеров считывается сигнал переполнения и поступает на шифратор 13. Этим же сигналом триггер 342 обнуляется и запрещает прохождение синхроимпульсов от делителя 21 на сумми0 рующий вход таймера.

По сигналу переполнения щифратор формирует код проверяемого непрерывно контролируемого логического условия, который поступает на соответствующие входы мультиплексоров 11 и 12 и на вход дешиф5 ратора 15 прерываний. Если истинное и требуемое значения проверяемого логического условия равны, то на выходе сумматора 27 присутствует нулевой сигнал, закрывающий третий элемент И 20. Если логическое условие не выполнилось за дан ный промежуток времени, то на выходе сумматора 27 присутствует единичный сигнал, открывающий элемент И 20 (триггер 26 прерываний в нулевом состоянии). По коду проверяемого Хз дешифратор 15 на своем выс ходе, соответствующем коду хз,формирует сигнал прерывания, который при разрешающем сигнале с выхода И 20 поступает на соответствующий вход шифратора 14. Шифратор 14 формирует адрес микроподпрограммы прерываний, предназначен0 ный для выполнения проверяемого логического условия. По заднему фронту очередного тактового импульса с выхода 25i генератора 25 и единичному сигналу с выхода элемента ИЛИ 23 адрес микроподпрограммы прерываний заносится в регистр 2 адре5 са, а триггер 26 устанавливается в единичное состояние, тем самым запрещая сброс таймеров и закрывая элемент И 20. В регистр 4 возврата по заднему фронту тактового импульса с выхода 25i генератора 25 при нулевом сигнале конца команды прерывания с выхода ЗЬ регистра 3 заносится адрес микрокоманды, с которой началось прерывание. Устройство отрабатывает микроподпрограмму прерывания.

После выполнения микроподпрограммы прерываний необходимо проверить, выполнилось или нет проверяемое логическое условие. В одной из последних микрокоманд микроподпрограммы прерываний считывается код хз и проверяется с помощью регистра 5 и его связи с третьим информационным входом мультиплексора 8. Если Хз выполнилось и равно требуемому значению, то по заднему фронту тактового импульса с выхода 252 генератора 25 с выхода 312 регистра 3 считывается сигнал конца команды прерываний, запрещая запись информации в регистр 4, обеспечивая запись адреса возврата через третий информационный вход мультиплексора 7 в регистр 2 и запуская одновибратор 28, который обнуляет триггер 26 прерываний. Если логическое условие не выполнилось, то вновь осуществляется возврат на микроподпрограмму прерываний. Далее устройство функционирует аналогично описанному выше алгоритму.

При считывании микрокоманды, в поле логических условий которой записан код хв, устройство до срабатывания щифратора 13 работает, как и при проверке.

При поступлении сигнала на вход дешифратора 15 на выходе, соответствующем аварийному логическому условию, присутствует единичный сигнал, который поступает в соответствующий разряд регистра 6. На управляющий вход регистра 6 поступает единичный сигнал с выхода сумматора 27. По заднему фронту тактового импульса с выхода 25| генератора 25 сигнал с выхода регистра 5 через элемент ИЛИ 22 поступает на вход установки в «О триггера 24 пуска. Триггер обнуляется и прекращает работу генератора 25 и всего устройства в целом. Работа устройства прекращается также при считывании сигнала конца работы с выхода 31з регистра 3 микроопераций.

Формула изобретения

Микропрограммное устройство для контроля и управления, содержащее блок памяти микрокоманд, регистр адреса, регистр микроопераций, регистр возврата, первый мультиплексор, первый шифратор, с первого по третий элементы И, триггер пуска, генератор тактовых импульсов, триггер прерываний, причем вход пуска устройства соединен с входом установки в «1 триггера пуска, выход которого соединен с входом генератора тактовых импульсов, первый и второй выходы которого соединены соответст0

5

0

5

0

5

0

5

0

5

венно с первыми входами первого и второго элементов И, вход кода команды устройства соединен с первым информационным входом первого мультиплексора, выход которого соединен с информационным входом регистра адреса, выход которого соединен с адресным входом блока памяти микрокоманд, выход поля микроопераций которогс соединен с информационным входом регистра микроопераций, выход которого соединен с выходом микроопераций устройства,выход триггера прерываний соединен с первым входом третьего элемента И, выход первого элемента И соединен с входом синхронизации и входом синхронизируемой установки в «1 триггера прерываний, отличающееся тем, что с целью повыщения быстродействия устройства и расширения области его применения, введены регистр контроля, регистр отказов, второй,третий и четвертый мультиплексоры, первый и второй демультиплексоры, второй шифратор, первый и второй дешифраторы, блок таймеров, делитель тактовых импульсов, первый и второй элементы ИЛИ, сумматор по модулю два, одновибратор, причем выход поля немодифицируемых разрядов адреса блока памяти микрокоманд соединен с соответствующими разрядами второго информационного входа первого мультиплексора, выход поля требуемого значения логического условия блока памяти микрокоманд соединен с информационным входом первого демультиплексора, выход которого соединен с информационным входом регистра контроля, выход поля модифицируемого разряда адреса блока памяти микрокоманд соединен с первым информационным входом второго мультиплексора, выход которого соединен с соответствующим разрядом второго информационного входа первого мультиплексора, выход поля метки блока памяти микрокоманд соединен с первым управляющим входом второго мультиплексора и с вторым входом второго элемента И, выход которого соединен со стробирующим входом второго дешифратора, выход поля кода логических условий блока памяти микрокоманд соединен с вторым управляющим входом второго мультиплексора и с управляющими входами первого и второго демультиплексо- ров, выход поля кода интервала блока памяти микрокоманд соединен с информационным входом второго демультиплексора и с информационным входом второго дешифратора, группа выходов которого соединена с группой входов синхронизации блока таймеров и с группой входов синхронизации регистра контроля, группа выходов второго демультиплексора соединена с группой информационных входов блока таймеров, выход которого соединен с входом первого шифратора, выход которого соединен с управляющим входом третьего мультиплексора, с управляющим входом четвертого мультиплексора и с входом первого дешифратора.

первый выход которого соединен с информационным входом регистра отказов, группа выходов которого соединена с группой входов первого элемента ИЛИ, второй выход первого дешифратора соединен с информационным входом второго шифратора и с группой установочных входов блока таймеров, выход признака конца команды регистра микроопераций соединен с первым управляющим входом первого мультиплексора, выход признака конца команды прерывания регистра микроопераций соединен с входом разрешения записи регистра возврата, с вторым управляющим входом первого мультиплексора и с входом одновибратора, выход которого соединен с входом установки в «О триггера прерываний, выход признака конца работы регистра микроопераций соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом установки в «О триггера пуска, первый выход генератора тактовых импульсов соединен с входом синхронизации регистра отказов и с входом синхронизации регистра адреса, выход которого соединен с информационным входом регистра возврата, второй выход генератора тактовых импульсов соединен с входом синхронизации регистра микроопераций, с первым входом синхронизации блока таймеров и с входом делителя тактовых им0

пульсов, выход которого соединен с вторым входом синхронизации блока таймеров, выход триггера прерываний соединен с входом разрешения сброса блока таймеров, вход логических условий устройства соединен с вторым информационным входом второго мультиплексора и с информационным входом третьего мультиплексора, выход которого соединен с первым входом сумматора по модулю два, выход регистра контроля соединен с третьим информационным входом второго мультиплексора и с информационным входом четвертого мультиплексора, выход которого соединен с вторым входом сумматора по модулю два, выход которого сое5 динен с вторым входом третьего элемента И и с входом разрешения записи регистра отказов, выход третьего элемента И соединен со стробируюшим входом второго шифратора, выход которого соединен с третьим информационным входом первого муль0 типлексора и с группой входов второго элемента ИЛИ, выход которого соединен с вторым входом первого элемента И, с третьим управляюшим входом первого мультиплексора, выход первого элемента И соединен с

5 входом синхронизации регистра возврата, выход которого соединен с четвертым информационным входом первого мультиплексора.

1 Г

13

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления и контроля | 1985 |

|

SU1280574A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1310817A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Микропрограммный модуль | 1986 |

|

SU1427366A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств контроля и управления технологическими процессами цифровых систем с микропрограммным управлением. Цель изобретения - расширение области применения и повышение быстродействия устройства. Микропрограммное устройство для контроля и управления содержит блок памяти 1 микрокоманд, регистр 2 адреса, регистры микроопераций 3, возврата 4, контроля 5 и отказа 6, первый 7 и второй 8 мультиплексоры, первый 9 и второй 10 демультиплексоры, третий И и четвертый 12 мультиплексоры, первый 13 и второй 14 шифраторы, первый 15 и второй 16 дешифраторы, блок 17 таймеров, первый 18, второй 19 и третий 20 элементы И, делитель 21 тактовых импульсов, первый 22 и второй 23 элементы ИЛИ, триггер 24 пуска, генератор 25 тактовых импульсов, триггер 26 прерываний, сумматор 27 по модулю два и одновибратор 28. Изобретение позволяет расширить область применения и повысить быстродействие устройства путем параллельного выполнения основных микропрограмм и контроля непрерывно контролируемых временных параметров технологических процессов. 2 ил. (Л со ю ел а

OmIB 21 2S 25.2

Составитель А. Михайлов

Редактор В. ПетрашТехред И. ВересКорректор С. Черни

Заказ 3110/44Тираж 672Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг.г

| Микропрограммное устройство управления | 1981 |

|

SU962943A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1980 |

|

SU955057A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-23—Публикация

1985-10-22—Подача