(54) УСТРОЙСТВО ДЛЯ ФАЗОВОГО УПРАВЛЕНИЯ СТАТИЧЕСКИМИ ПРЕОБРАЗОВАТЕЛЯМИ

необходимо применение дорогостоящих и сложных устройств преобразования частоты импульсов в напряжение, что снижает функциональную и элементарную надежность.

Наиболее близким по технической сущности к предлагаемому устройству является цифровое устройство импульсно-фазового управления, состоящее из счетчика импульсов, схемы ввода цифрового кода в счетчик импульсов от ЭВМ, нуль-органа, связанного с питающей сетью, причем вход счетчика соединен с генератором постоянной частоты, а выход счетчика через логические схемы совпадений и ИЛИ - с оконечными каскадами 3. Принцип работы заключается в том, что интервал времени заполнения счетчика импульсами постоянной частоты изменяется в зависимости от вводимого кода числа. Следует заметить, что, хотя управление происходит цифровым кодом, управляющим воздействием является импульс переполнения счетчика.

Недостатком известного цифрового устройства импульсно-фазового управления является сложность введения сигналов коррекции и обратных связей. Для введения данных сигналов через вычислительную мащину необходимо разработать специальные алгоритмы и применить сложные устройства преобразования аналоговых величин в цифровые.

Цель настоящего изобретения - упрощение и расщирение функциональных возможностей устройства.

Поставленная цель достигается тем, что устройство для фазового управления статистическими преобразователями, содержащее счетчик импульсов, установочный вход которого подключен к выходу нуль-органа, соединенного с питающей сетью, а выход счетчика к первым входам схем совпадений, выходы которых подключены к оконечным каскадам, причем вторые входы схем совпадений попарно соединены с соответствующими выходами нуль-органа, а третьи входы также попарно подключены к программным источникам реверсивного управления и источники сигналов управления, положительных и отрицательных коррекций и обратных связей, снабжено сумматором частотно-импульсных сигналов, состоящим из логического элемента ИЛИ и «п формирователей с разрещающими и запрещающими выходами, последовательно-пареллельно соединенными между собой, причем каждый формирователь состоит из двух PS-триггеров и четырех схем совпадений, при этом источники сигналов управления и положительных коррекций подключены ко входам формирователей с разрешающим выходом, а источники сигналов обратных связей и отрицательных коррекций подключены ко входам формирователей с запрещающим выходом.

при этом выходы последовательно соединенных формирователей и выходы параллельно включеных формирователей с разрещающим выходом ко входу логического элемента ИЛИ, а его выход соединен со счетным входом счетчика.

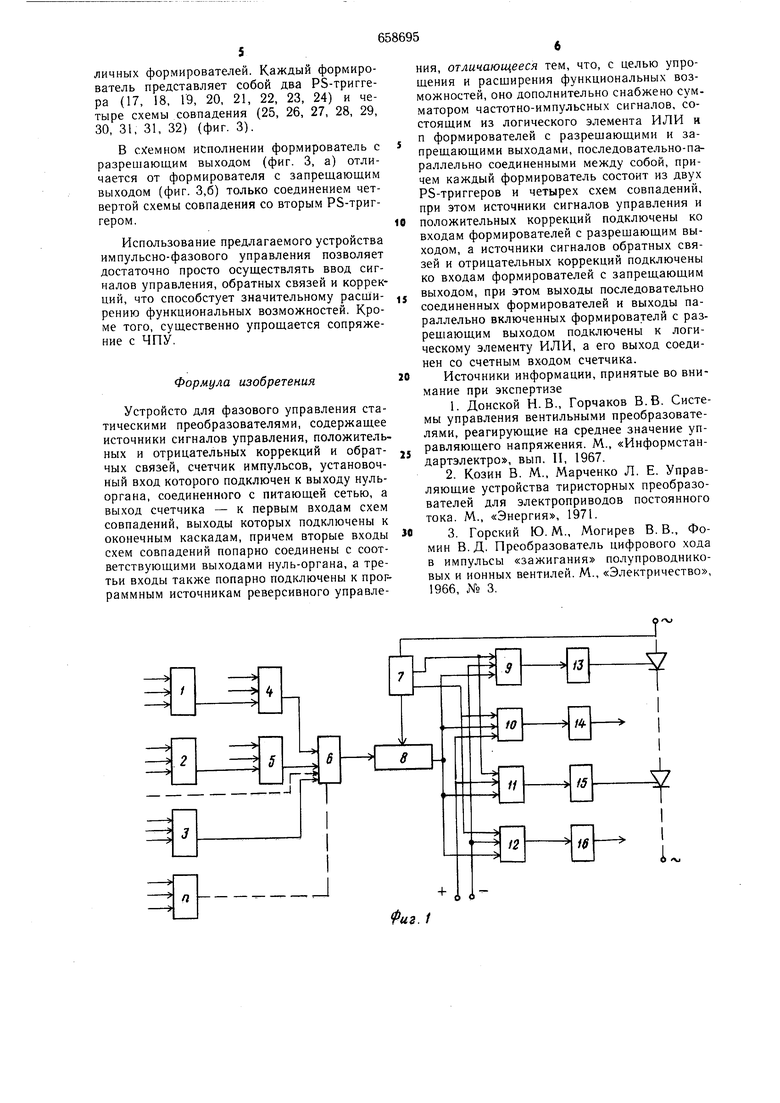

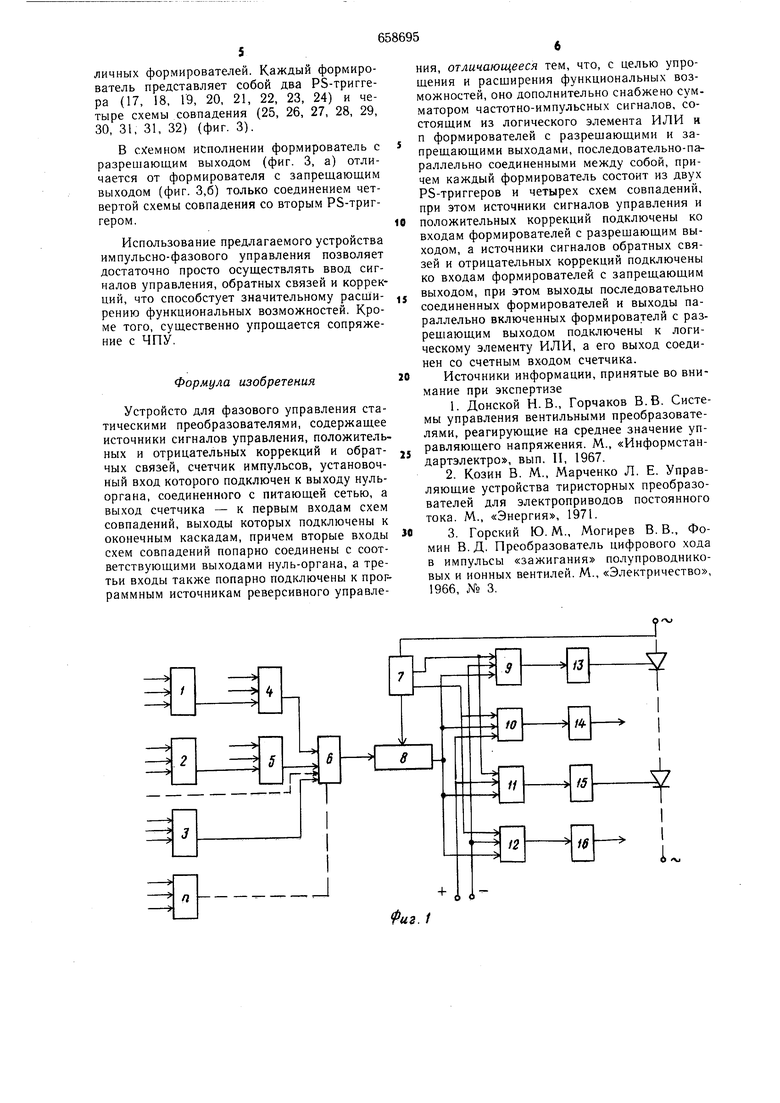

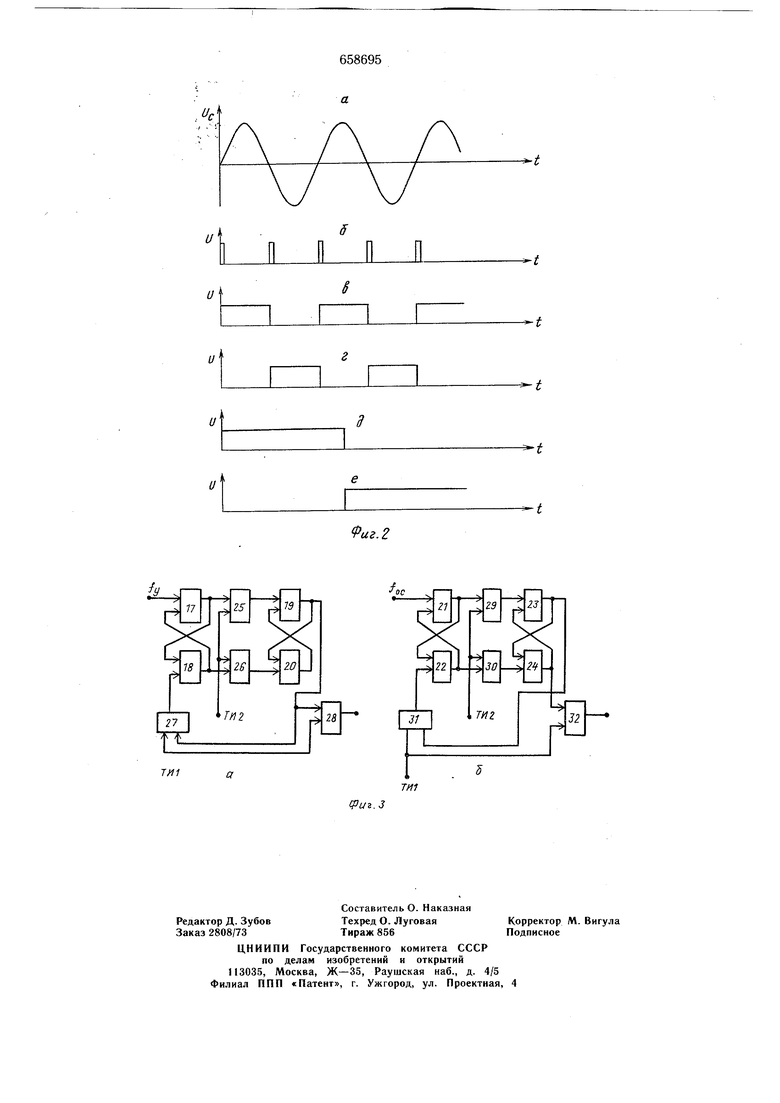

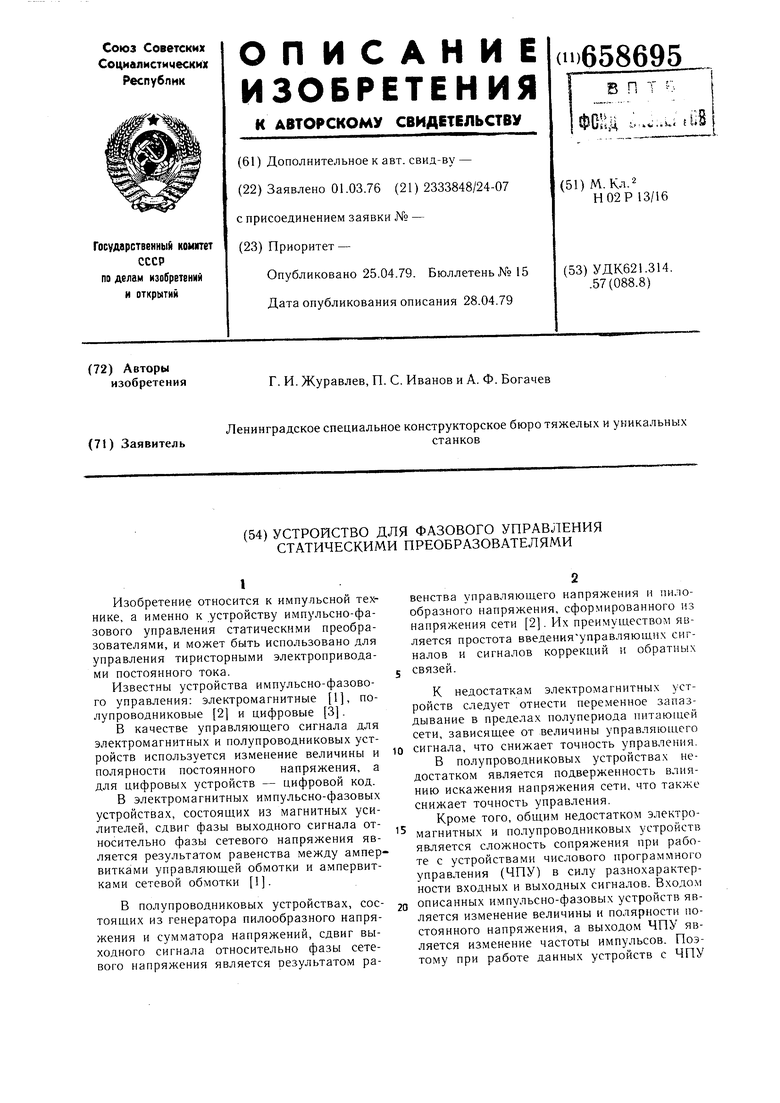

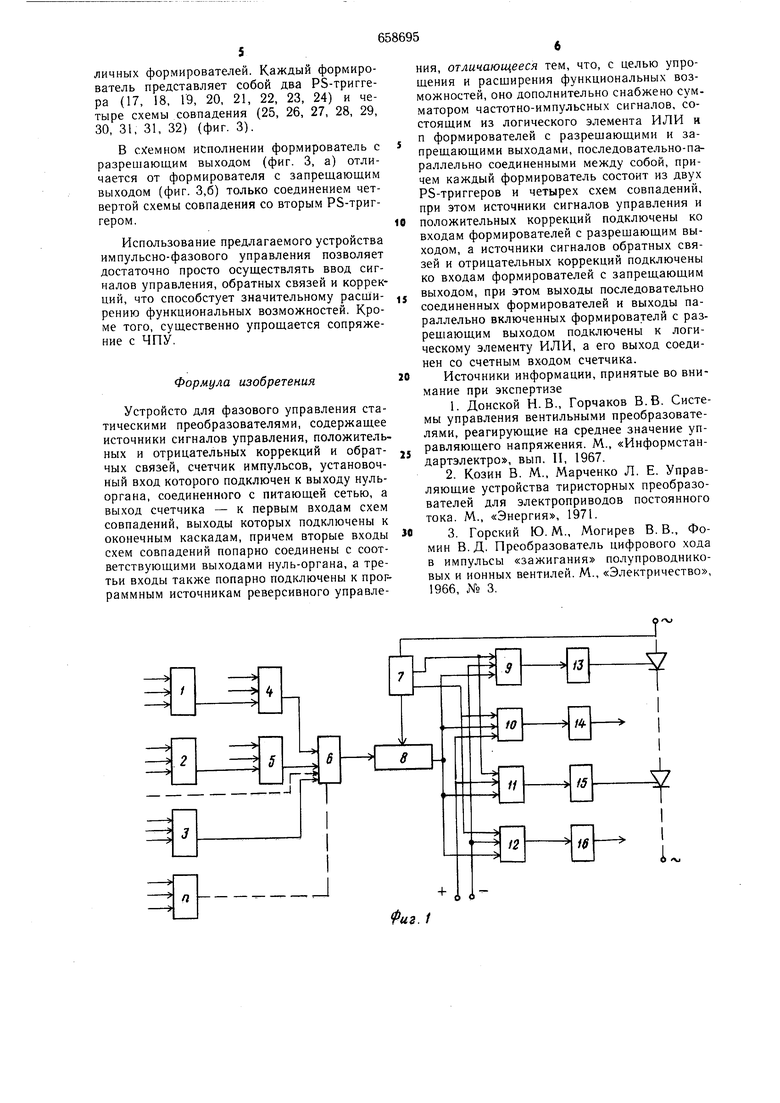

На фиг. I представлена блок-схема устройства импульсно-фазового управления; на фиг. 2 - диаграммы напряжений; на фиг. 3 - принципиальные схемы формирователей

с разрещающими выходами (фиг. 3, а) и запрещающими выходами (фиг. 3 б).

Устройство состоит из формирователей импульсов 1, 2, 3, 4, 5...П, логического элемента ИЛИ 6, нуль-органа 7, счетчика импульсов 8, схем совпадений 9, 10, 11, 12

и оконечных каскадов 13, 14, 15, 16. Выходом устройства являются выходы оконечных каскадов.

Устройство работает следующим образом.

Нуль-орган 7 вырабатывает импульс (фиг. 2, б), устанавливающий счетчик в нулевое состояние при прохождении сетевого напряжения через нуль (фиг. 2, а). После исчезновения установочного импульса счетчик 8 начинает счет импульсов. Импульс переполнения счетчика 8 поступает на схемы совпадений 9, 10, 11, 12, куда также поступают программные сигналы реверсивного управления (фиг. 2, д, е) и сигналы,

0 соответствующие времени прохождения положительной и отрицательной полуволн напряжения сети, вырабатываемого нуль-органом 7 (фиг. 2, в. г).

В случае прохождения положительной полуволны сигналы поступают на схемы совJ падений 9, 12, а при отрицательной - на схемы 10, 11. При положительном выходе сигнал переполнения счетчика 8 пройдет через схемы совпадений 10, 12 и поступит на оконечные каскады 13, 14, при этом положительной полуволне будет соответствовать оконечный каскад 13, а отрицательной - 14. При отрицательном выходе положительной полуволне будет соответствовать каскад 15, а отрицательной - каскад 16. Программные сигналы реверсивного уп равления формируются в ЧПУ.

С целью разнесения сигналов управления, обратных связей и коррекций применены формирователи импульсов 1, 2, 3, 4, 5...п. Разнесение во времени осуществляется с помощью тактовых импульсов ТИ1, ТИ2, ТИЗ, ТИ4...ТИп, сдвинутых относительно друг друга на 36(3°.

Формирователи 1, 2, З...п с разрещающими выходами только формируют импульсы, а формирователи 4, 5 с запрещающими выходами осуществляют вычитание импульсов при последовательном соединении двух различных формирователей. Каждый формирователь представляет собой два PS-триггера (17, 18, 19, 20, 21, 22, 23, 24) и четыре схемы совпадения (25, 26, 27, 28, 29, 30, 31, 31, 32) (фиг. 3). В схемном исполнении формирователь с разрешающим выходом (фиг. 3, а) отличается от формирователя с запрещающим выходом (фиг. 3,6) только соединением четвертой схемы совпадения со вторым PS-триггером. Использование предлагаемого устройства импульсно-фазового управления позволяет достаточно просто осуществлять ввод сигналов управления, обратных связей и коррекций, что способстует значительному расширению функциональных возможностей. Кроме того, существенно упрощается сопряжение с ЧПУ. Формула изобретения Устройсто для фазового управления статическими преобразователями, содержащее источники сигналов управления, положительных и отрицательных коррекций и обратных связей, счетчик импульсов, установочный вход которого подключен к выходу нульоргана, соединенного с питающей сетью, а выход счетчика - к первым входам схем совпадений, выходы которых подключены к оконечным каскадам, причем вторые входы схем совпадений попарно соединены с соответствующими выходами нуль-органа, а третьи входы также попарно подключены к программным источникам реверсивного управления, отличающееся тем, что, с целью упрощения и расщирения функциональных возможностей, оно дополнительно снабжено сумматором частотно-импульсных сигналов, состоящим из логического элемента ИЛИ и п формирователей с разрешающими и запрещающими выходами, последовательно-параллельно соединенными между собой, причем каждый формирователь состоит из двух PS-триггеров и четырех схем совпадений, при этом источники сигналов управления и положительных коррекций подключены ко входам формирователей с разрещающим выходом, а источники сигналов обратных связей и отрицательных коррекций подключены ко входам формирователей с запрещающим выходом, при этом выходы последовательно соединенных формирователей и выходы параллельно включенных формирователи с разрешающим выходом подключены к логическому элементу ИЛИ, а его выход соединен со счетным входом счетчика. Источники информации, принятые во внимание при экспертизе 1. Донской Н.В., Горчаков В. В. Системы управления вентильными преобразователями, реагирующие на среднее значение управляющего напряжения. М., «Информстандартэлектро, вып. П, 1967. 2. Козин В. М., Марченко Л. Е. Управляющие устройства тиристорных преобразователей для электроприводов постоянного тока. М., «Энергия, 1971. 3. Горский Ю. М., Могирев В. В., Фомин В. Д. Преобразователь цифрового хода в импульсы «зажигания полупроводниковых и ионных вентилей. М., «Электричество, 1966, N° 3.

,Uc

t

и

n п п п

(

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения логарифмического декремента затухания механических колебаний | 1971 |

|

SU506767A1 |

| Устройство для управления тиристор-НыМ пРЕОбРАзОВАТЕлЕМ | 1979 |

|

SU817975A1 |

| Устройство для несимметричного управления последовательно включенными преобразователями | 1977 |

|

SU736353A1 |

| Устройство для регулирования мощности | 1986 |

|

SU1422230A1 |

| Способ цифрового управления многофазным инвертором | 1989 |

|

SU1683154A1 |

| НИЗКОВОЛЬТНЫЙ СИЛЬНОТОЧНЫЙ ИСТОЧНИК ПИТАНИЯ ДЛЯ СТАНКОВ ЭЛЕКТРОХИМИЧЕСКОЙ ОБРАБОТКИ МЕТАЛЛОВ | 1991 |

|

RU2025031C1 |

| Фазосдвигающее устройство | 1981 |

|

SU957124A1 |

| УСТРОЙСТВО для УПРАВЛЕНИЯ ТИРИСТОРНЫМ ПРЕОБРАЗОВАТЕЛЕМ ЧАСТОТЫ С НЕПОСРЕДСТВЕННОЙСВЯЗЬЮ | 1969 |

|

SU257588A1 |

| Устройство для управления встречно-параллельно включенными тиристорами | 1989 |

|

SU1697211A1 |

| Вибрационный источник сейсмических сигналов | 1983 |

|

SU1138772A1 |

7)11а

Авторы

Даты

1979-04-25—Публикация

1976-03-01—Подача