1

Изобретение относится к электроизмерительной технике, может быть применено для измерения составляющих комплексного сопротивления в широкой полосе частот с большим быстродействием.

Известен измеритель комплексного коэффициента передачи, содержащий инвертор, нуль-орган, связанный с блоком управления, который подключен к усилителям-ограничителям, первый из которых непосредственно, а второй через фазовращатель подключен ко входному зажиму устройства, который через выпрямитель, первый ключ, первый интегратор и второй ключ соединен со входом второго интегратора, причем управляющие входы ключей через блок управления подключены к третьему ключу, вход которого связан с генератором опорной частоты, а выход - со счетчиком импульсов 1.

Недостатком этого устройства является узкий диапазон измерения.

Цель изобретения - расщирение диапазона измерения без снижения точности.

Эта цель достигается тем, что цифровой измеритель составляющих полного сопротивления, содержащий инвертор, нуль-орган, связанный с блоком управления, который

подключен к усилителям-ограничителям, первый из которых непосредственно, а второй через фазовращатель подключен ко входному зажиму устройства, который через выпрямитель, первый ключ, первый интегратор и второй ключ соединен со входом второго интегратора, причем управляющие входы ключей через блок управления подключены к третьему ключу, вход которого связан с генератором опорной частоты, а выход - со счетчиком импульсов, снабжен двумя переключателями, двумя преобразователями, цепью вторичного двойного интегрирования, тремя ключами и источником опорного напряжения, соединенным с первым входом цепи вторичного двойного интегрирования и через первый преобразователь - с блоком управления, вторым входом упомянутой цепи и первым ключом, связанным с блоком управления, причем один из неподвижных контактов первого переключателя соединен со вторым ключом, другой неподвижпый контакт через четвертый ключ соединен с выхо0дом второго интегратора и одним неподвижным контактом второго переключателя, другой неподвижный контакт которого связан с выходом первого интегратора, а входная

клемма через второй преобразователь подключена к пятому Котючу и последовательно соединенным инвертору и шестодму ключу; пятый и шестой ключи соединены со входом второго интегратора и блоком управления. Цепь вторичного двойного интегрирования содержит интегратор, нуль-орган и два ключа, включенных между соответствующим входом устройства и входом интегратора, выход которого подключен к нуль-органу, а оба. ключа, интегратор и нуль-орган связаны с блоком управления.

Блок управления содержит триггер со счетным входом, схемы совпадения, перекрестный переключатель на два входа и два выхода и два синхронно переключаемых переключателя, причем вход триггера подключен к выходу первого усилителя-ограничителя, а каждый из выходов соединен с одним из входов двух схем совпадения соответственно, вторые входы первых двух схем совпадения один непосредственно, а другой через инвертор соединены с подвижным контактом третьего переключателя, первый и второй неподвижные контакты которого подключены соответственно к выходам первого и второго усилителей-ограничителей; выходы вышеупомянутых первых двух схем совпадения через перекрестный переключатель подключены к управляюш.им входам пятого и шестого ключей, вторые входы других двух схем совпадения один непосредственно, а другой через инвертор соединены с выходом первого нуль-органа; выход схемы совпадения, подключенной к выходу нуль-органа, через инвертор,соединен с нулевыми входами первых двух интеграторов, а выход другой схемы совпадения подключен к подвижному контакту первого переключателя и к управляющему входу ключа, включенного между выходом первого преобразователя и входом дополнительного интегратора, а также к первому неподвижному контакту четвертого переключателя, подвижный контакт которого соединен с управляющим входом ключа, включенного между счетчиком импульсов и генератором опорной частоты, и к первым входам двух третьих схем совпадения, два других входа которых соединены один - непосредственно, а другой через инвертор с выходом нуль-органа вторичной цепи двойного интегрирования, причем выход схеми совпадения, непосредственно соединенной с выходо.м второго нуль-органа, подключен к управляющему входу ключа, включенного между источником опорного напряжения и входом дополнительного интегратора, а также ко второму неподвижному контакту четвертого переключателя; выход другой схемы совпадения соединен с нулевыми входами первого преобразователя и дополнительного интегратора, причем управляющие входы первого ключа и первого преобразователя соединены со вторым выходом триггера.

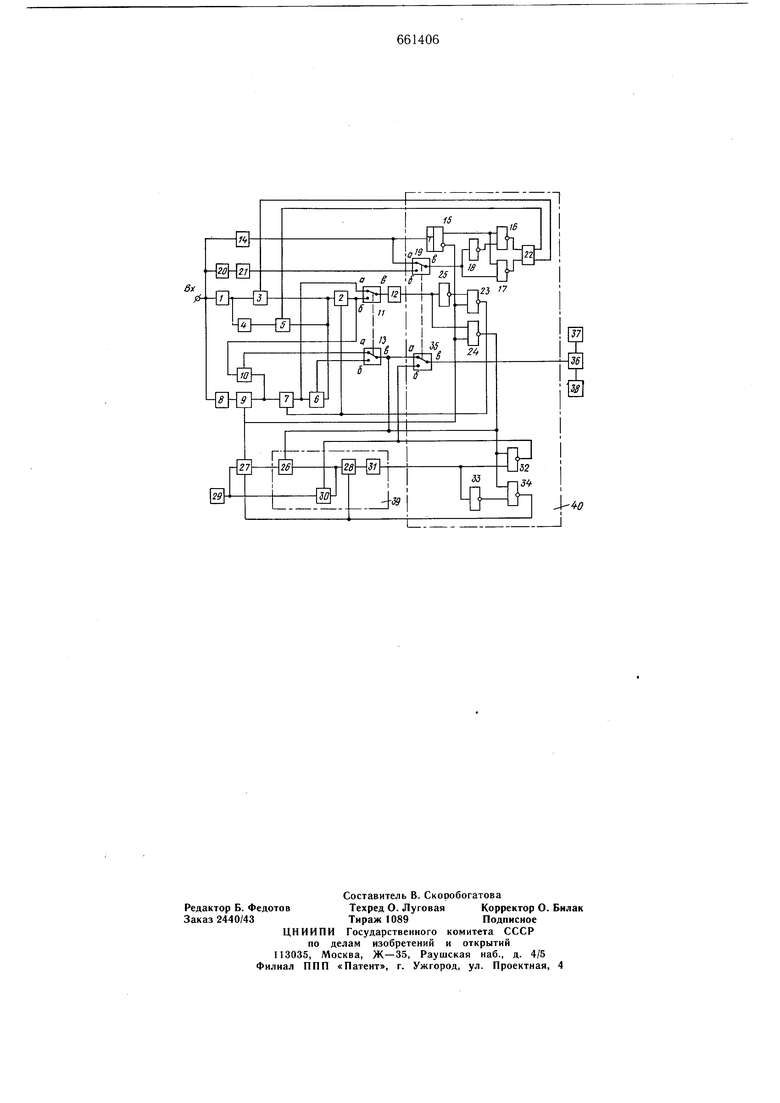

Структурная электрическая схема цифрового измерителя составляющих полного сопротивления представлена на чертеже. Вход преобразователя полного сопротив5 ления 1 соединен со входной клеммой устройства, а выход - со входом интегратора 2 через ключ 3 и через последовательно соединенные инвертор 4 и ключ 5. Вход интегра. тора 2 соединен через ключ 6 с выходом инQ тегратора 7, вход которого через последовательно соединенные выпрямитель 8 и ключ 9 подключены ко входу устройства. Выход интегратора 2 соединен через ключ 10 со входом интегратора 7. Выходы интеграторов 7 и 2 подключены соответственно к контактам «а и «б переключателя 11, контакт «в которого соединен со входом нуль-органа 12. Управляющие входы ключей 10 и 6 подключены соответственно к контактам «а и «б переключателя 13. Переключатели 11 и 13 переключаются синхронно. Вход усилителя-ограничителя 14 соединен со входом устройства, а выход - со счетным входом триггера 15. Первый выход триггера 15 подключен к одному из входов схем совпадения 16 и 17, вторые входы которых соответственно - один через инвертор 18, другой непосредственно - соединены с контактом «б переключателя 19, контакт «а которого подключен к выходу усилителя-ограничителя 14, а контакт «б через последовательно соединенные фазовращатель 20 и усилитель0 ограничитель 21 подключен ко входу устройства. Выходы схем совпадения 16 и 17 через перекрестный переключатель 22 соединены с управляющими входами ключей 3 и 5. Второй выход триггера 15 подключен к одному из входов схем совпадения 23 и 24. Второй вход схемы совпадения 23 соединен с выходом нуль-органа 12 через инвертор 25. Выход схемы совпадения 23 подключен ко входам «зануления интеграторов 2 и 7. Выход нуль-органа 12 соединен со вторым

входом схемы совпадения 24, выход которой подключен к контакту «0 переключателя 13 и к управляющему входу ключа 26, включенного между выходом преобразователя «период-напряжение 27 и входом интегратора 28. Псточник опорного напряжения 29 через ключ 30 также подключен ко входу интегратора 28, выход которого через нульорган 31 соединен с одним из входов схемы совпадения 32, и через инвертор 33 - с одним из входов схемы совпадения 34. Выход схемы совпадения 34 подключен ко входам «зануления интегратора 28 и преобразователя «период-напряжение 27. Выход схемы совпадения 24 соединен с контактом «а переключателя 35 и со вторыми входами схем совпадения 34 и 32, выход последней

подключен к управляющему входу ключа 30, а также к контакту «б переключателя 35. Контакт «0 переключателя 35 соединен с управляющим входом ключа 36,-включенного между генератором опорной частоты 37 и счетчиком импульсов 38. Переключатели 19 и 35 переключаются синхронно. Управляюш,ие входы ключа 9 и преобразователя «период-напряжение 27 соединены со вторым выходом триггера 15. Ключи 26, 30, интегратор 28 и нуль-орган 31 образуют цепь вторичного двойного интегрирования 39. Триггер со счетным входом 15, элементы логики 16-18, 23-25, 32-34, переключатели 19, 35, 22 образуют блок управления 40. Работу устройства рассмотрим на примере получения цифрового отсчета, пропорционального составляющей полного сопротивления для случая, когда она носит частотнозависимый характер. Выходное напряжение преобразователя полного сопротивления в наиболее общем случае состоит из двух квадратурных напряжений (одно из них в фазе со входным илн противофазно входному), амплитуда которых прямо (или обратно) пропорциональна либо измеряемому пара.метру полного сопротивления, либо произведению частоты входного сигнала на измеряемый параметр полного сопротивления (частотнозависима квадратурная составляющая), сдвиг фаз ф между входным и выходным напряжением преобразователя полного сопротивления может быть в пределах ±90°. В зависимости от знака сдвига фаз перекрестный переключатель 22 соединяет выход схемы совпадения 16 с управляющим входом ключа 3 и выход схемы совпадения 17 - с управляющим входом ключа 5 (если ) и наоборот, если ф 0. Следует сразу оговориться, что все усилители-ограничители, нуль-органы (представляющие собой также усилители-ограничители), интеграторы, элементы совпадения - инвертирующие, ключи открываются низким потенциалом по управляющему входу, а фазовращатель 20 - интегрирующая цепь. Переключатели II и 13 находятся в первом положении (т. е. соединены контакты а и б), если зависимость между амплитудой квадратурных составляющих выходного напряжения преобразователя 1 и измеряемым параметром обратно пропорциональная, и во втором положении (т. е. соединены контакты бив), если она прямо пропорциональная. Переключатели 19 и 35 находятся в первом положении, если определяется синфазная составляющая выходного напряжения преобразователя 1, и во втором положении, если квадратурная (частотнозависимая). Если переключатели 11 и 13, 19 и 35 находятся во втором положении, т. е. соединены контакты 2 и 3, триггер 15 управляется по счетному входу усилителем-ограничителем 14 и изменяет свое состояние по нуль-переходам входного сигнала устройства с минуса на плюс. Во время существования высокого потенциала на первом выходе триггера 15 выходное напряжение усилителя-органичителя 21 изменяет выходное напряжение схем совпадения 16 и 17. В течение времени существования низкого потенциала на выходах схем совпадения 16 и 17 ключи 3 и 5 открываются, обеспечивая поступление на интегратор 2 соответствующих участков выходного нап-ряжения преобразователя 1 и инвертора 4. В течение этого же периода напряжение со второго выхода триггера 15 держит открытым ключ 9, обеспечивая заряд интегратора 7 выходным напряжением двухполупериодного выпрямителя 8, а также заряд преобразователей «период-напряжение 8 и 27. По окончании периода интегрирования триггер 15 изменяет свое состояние, и теперь высокий потенциал появляется на его втором выходе. При этом на выходе схемы совпадения 24 позникает низкий потенциал как результат совпадения высокого потенциала с нуль-органа 12 и со второго выхода триггера 15, обеспечивая открывание ключей 6 и 26. Начинается разряд интегратора 2 выходным напряжением интегратора 7 (последний находится все это время в режиме памяти) и заряд интегратора 28 выходным напряжением преобразователя «период-напряжение 27 (последний также находится это время в режиме памяти). По окончании разряда интегратора 2 на входе нуль-органа 12 появляется низкий потенциал. При этом на выходе схе.мы совпадения 23 также появляется низкий потенциал, обеспечивающий восстановление начальных условий интегрирования интеграторов 2, 7 и удержание их до начала следующего периода интегрирования. Па выходе схемы совпадения 24 в это время появляется высокий потенциал, ключи 6 и 26 закрываются, а на выходе схемы совпадения 32 появляется низкий потенциал, как результат совпадения высокого потенциала с нуль-органа 31 и со схемы совпадения 24. Ключи 30 и 36 открываются, начинается разряд интегратора 28, в течение которого в счетчике 38 накапливаются импульсы от генератора 37. В конце интервала на выходе нуль-органа 31 появляется низкий потенциал, что вызывает изменение потенциалов на выходе схем совпадения 32 и 34. В результате ключ 30 закрывается, а в интеграторе 28 и преобразователе 27 восстанавливаются начальные условия интегрирования, которые сохраняются там низким выходным напряжением схемы совпадения 34 до начала следующего интервала интегрирования. В счетчике 38 и конце интервала времени получают код. Отсчет счетчика 38 возобновляется через период входного сигнала. Он не зависит от частоты и амплитуды входного сигнала. При других положениях переключателей схема функционирует аналогичным образом. Следовательно, введение в структуру прототипа переключателей, двух преобразователей «период-напряжение и пени вторичного двойного инте1рирования позволяет расширить функциональные возможности устройства - измерять составляющие нолного сопротнвления исследуемых цепей. При SITOM обеспечивается быстродействие.

Формула изобретения

1. Цифровой изме|1итель составляющн.х нолиого сонротивле(П1я, содержащий инвертор, нуль-орган, связанн1|И1 с блоком управления, который подключен к усилителям-oiраничителям, первый из которых неиосредственно, а второй через фазовран1атель нодключен ко входному зажиму устройства, который через вьтрямитель, нервый ключ, первый интегратор и второй ключ соединен со входом второго интегратора, причем управляющие входы ключей через блок ynpaB.ieния подключены к третьему ключу, вход которого связан с генератором опорной частоты, а вьгход - со счетчиком импульсов, отличающийся тем, что, с целью расщиреипя диапазона из.мерения без снижения точности, он снабжен двумя нереключателями, двумя преобразователями, цепью вторичпого двойного интегрирования, тремя ключами и источиико.м онориого напряжения, соединенным с первым входом цепи вторичного двойного ннтегрирования и через первый преобразователь - с блоком управления, вторым входом уномянутой цепи и первым ключом, связанным с б.ооком управления, при этом один из неподвижных контактов первого переключателя соединен со вторым ключом, другой неподвижный контакт через четвертый ключ соединен с выходом второго интегратора и одним неподвижным контактом второго переключателя, другой неподвижный контакт которого связан с выходом первого интегратора, а входная клем.ма через второй преобразователь подключена к г.ятому ключу и последовательно соединен} }лм инвертору и щесто.му ключу, при этом пятый и шестой ключи соединены со входом второго интегратора и с блоком управления.

2.Устройство но п. 1, отличаюш,ееся тем, что цень вторичного двойного интегрироваHiin содержит интегратор, нуль-орган и два ключа, включеиных между соответствуюниьм входом устройства и входом интегратора, выход которого нодключен к нуль-органу, а оба ключа, И1ггегратор и нуль-орган связаны е блоком унравления.

3.Устройство по п. 1, отличающееся тем, что блок управления содержит триггер со

счетным входом, схемы coвпaдeJH- я, иерекрест Н)1Й нсреключатель на два входа и два выхода и два синхронно переключаемых переключателя, причем вход триггера подключен

к выходу первого уснлнте,:|я-ограничителя, а каждь й из выходов соединен с одним из входов двух схем совнядепия соответственно, вторые вход1)1 первых двух схем совпадения один непосредственно, а другой через ииQ вертор соединены с нодвижным контактом трстьего нереключателя, перВ1з1Й и второй иеподвижиые KOHTaKTi i которого подключены соответственно к выходам нервого и второго усилителей-ограничителей, выходы выП1еуиомянутых нервых двух схем совиадения

5 через перекрестный псреключател1 подключены к управляющим входам иятого и 1иестого ключей, BTopiiie входы других схем совпадения одни непосредственно, а дру|ч)й через инвертор соедннены с выходом нуль-органа, нричем выход схемы совпадения, подключенной к выходу ну.п -органа через инвертор, с{)ед1Н1ен с нулег ыми входами нервых двух интеграторов, а выход другой схемы совпадения подключен к нодвижЕюму контакту nepBoiO переключателя

5 и к управля1оп1,ему входу ключа, вк;1юченного между 1 ыходом нервого преобразователя н входом донолнительного интегратора, а также к первому ненодвижиому контакту четвертого переключателя, нодвижиый контакт которого соединен е управляющим входом ключа, включенного между счетчиком и генератором опорной частоты, н к нервы.м входа.м двух третьих ехем совпадения, два других входа котор1 гх соединены один иеносредственно, а другой через инвертор е выходом нуль-органа вторичной цени двойного интегрирования, причем выход схемы совиадения, непоередственно соединенной с выходом второго нуль-органа, нодключен к управляющему входу ключа, включенного между источником опорного напряжения и входом дополиительного интегратора, а также ко второму неподвижному контакту четвертого переключателя, выход другой схемы еовпадения соединен с нулевыми входами нервого преобразователя и дополнительного интегратора, ириче.м 5 унравляющие входы первого ключа и первого преобразователя соединены со вторым выходом триггера.

Источники информации,принятые во вни0 маиие при экспертизе

1. Авторское свидетельство СССР h 516975, О 01 R 27/28, 15.08.75.

Р

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель коэффициента мощности | 1977 |

|

SU746314A1 |

| ЦИФРОВОЙ ИНФРАНИЗКОЧАСТОТНЫЙ ШИРОКОПОЛОСНЫЙ ФАЗОМЕТР МГНОВЕННЫХ ЗНАЧЕНИЙ | 1973 |

|

SU453647A1 |

| Функциональный частотный преобразователь | 1983 |

|

SU1120365A1 |

| Умножитель частоты следования им-пульсов | 1974 |

|

SU508939A1 |

| Устройство для моделирования вентильного преобразователя | 1981 |

|

SU993293A1 |

| Устройство для измерения сдвига фаз инфранизкочастотных сигналов | 1976 |

|

SU600474A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ИЗНОСА РЕЖУЩЕГО ИНСТРУМЕНТА | 2004 |

|

RU2263300C1 |

| Устройство для определения статистических моментов | 1978 |

|

SU723589A1 |

| Множительно-делительное устройство | 1977 |

|

SU696444A1 |

| Цифровой измеритель коэффициента передачи четырехполюсника | 1986 |

|

SU1323985A1 |

Авторы

Даты

1979-05-05—Публикация

1976-11-26—Подача