(54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ .СТИРАНИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ФИЛЬТРАЦИИ НЕРАВНОМЕРНЫХ КОДОВ | 2009 |

|

RU2400934C1 |

| СИСТЕМА ИСПРАВЛЕНИЯ СТИРАНИЙ С ЗАЩИТОЙ НОМЕРА КЛАСТЕРА | 2012 |

|

RU2485702C1 |

| УСТРОЙСТВО ВОССТАНОВЛЕНИЯ КОДОВОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2003 |

|

RU2256294C1 |

| УСТРОЙСТВО ВОССТАНОВЛЕНИЯ СТИРАНИЙ | 2007 |

|

RU2345493C1 |

| ДЕКОДЕР С ПОВЫШЕННОЙ КОРРЕКТИРУЮЩЕЙ СПОСОБНОСТЬЮ | 2010 |

|

RU2438252C1 |

| ДЕКОДЕР С ИСПРАВЛЕНИЕМ СТИРАНИЙ | 2007 |

|

RU2344556C1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМНО-ДЕМОДУЛИРУЮЩЕЕ УСТРОЙСТВО ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ СИСТЕМ СВЯЗИ | 2005 |

|

RU2305375C2 |

| ДЕКОДЕР С ИСПРАВЛЕНИЕМ СТИРАНИЙ | 2008 |

|

RU2379841C1 |

| Способ и устройство обработки ФТ сигнала с дискретной подстройкой фазы в экономичном режиме | 2019 |

|

RU2729042C1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2556439C2 |

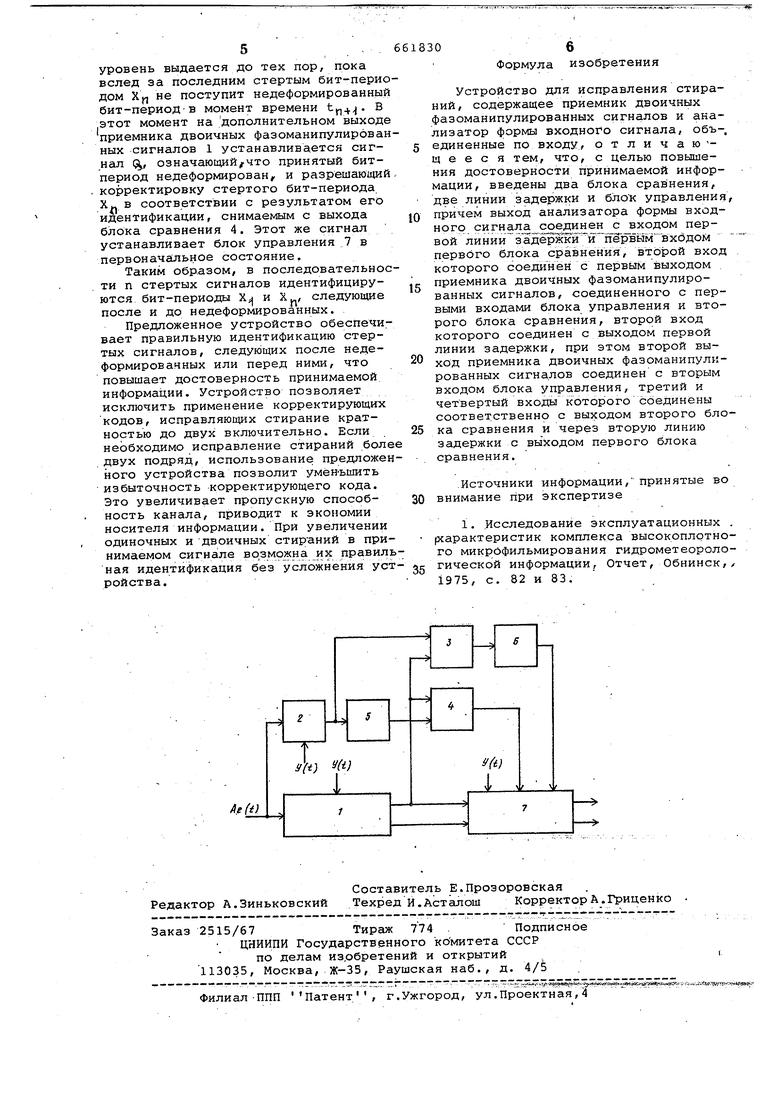

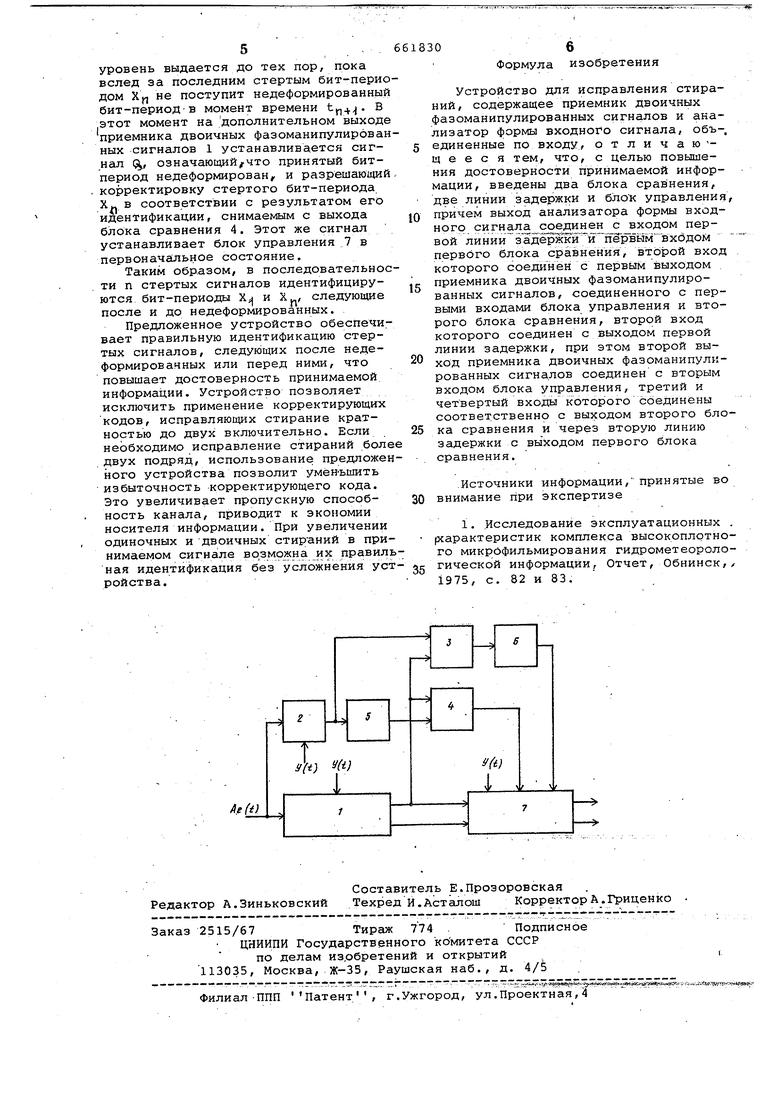

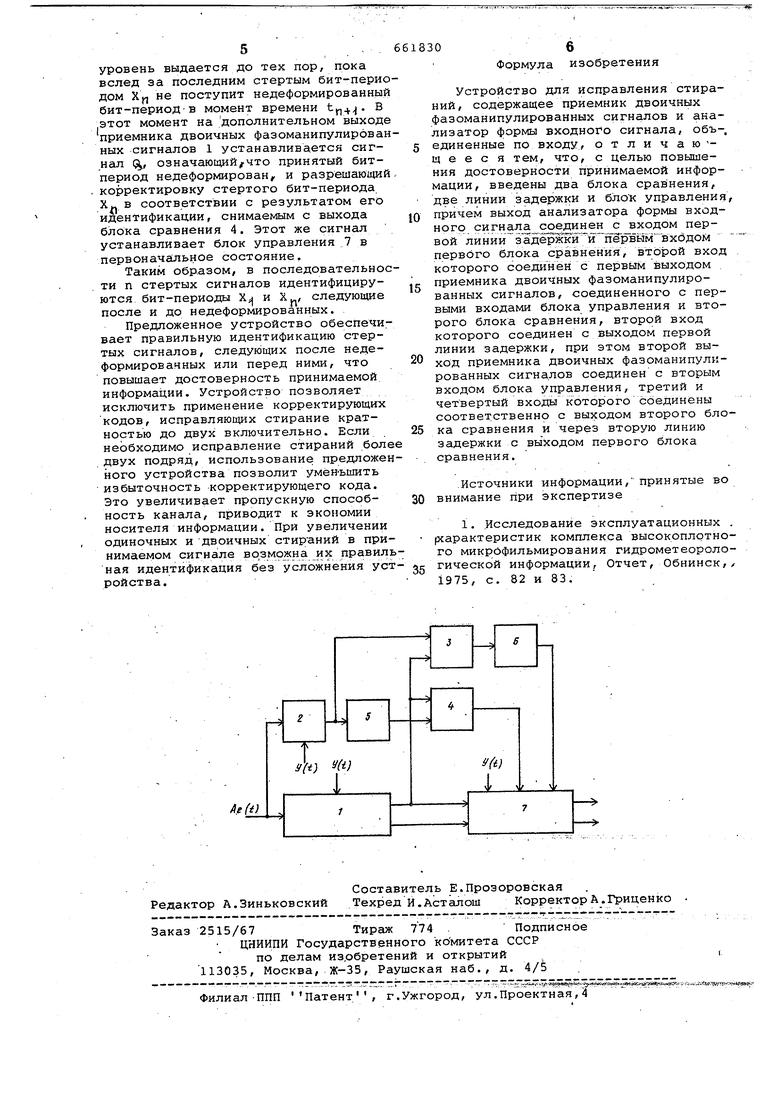

Изобретение относится к радиотех.нике и может быть использовано в уст ройствах, предназначенных для приема или считывания двоичных фазоманипулированных. сигналов со стираниями. Известно устройство для исправления стираний, содержащее приемник двоичных фазрманйпулированных сигналов -и анализатор формы входного сигнала, объединенные по входу Ц. Однако известное устройство для исправления .стираний обладает низкой достоверностью принимаемой информации. Целью изобретения является повыше ние достоверности принимаемой информации . Для этого в устройство для исправ ления стираний, содержащее приемник .двоичных фазоманипулИрованных сигналов и анализ атсэр формы входного сигн ла, объединенные по входу, введены два блока сравнения, две линии задержки иблок управления, причем выход анализатора формы входного сигнала соединен с входом первой линии задержки и первым входом первого бло ка сравнения, второй вход которого соединен с первым выходом приемника двоичных фазоманипулИрованных;оигналов, соединенного с первыми входами блока управления и второго блока сравнения, второй вход которого соединен с выходом первой линии задержки, при этом второй выход приемника двоичных фазоманипулИрованных сигналов соединен с вторым входом блока управления, третий и четвертый входы которого соединены соответственно с выходом йторого блока сравнения и через вторую линию задержки с выходом первого блока сравнения. На чертеже приведена структурная электрическая схема устройства. Устройство для исправления стира,ний содержит приемник двоичных фазоманипулИрованных сигналой 1 и анализатор формы входного сигнала 2, объединенные по входу, два блока сравнения 3 и 4, две линии задержки 5 и 6 и блок управления 7. Причем выход анализатора формы входного сигнала 2 соединен с входом первой линии .задержки 5 и первым входом первого блока сравнения 3, второй вход которого соединен с первым выходом приемника двоичных фазоманипулИрованных сигналов , соединенного с первыми входами блока управления 7 и второго блока сравнения 4, второй вход которого соединен с выходом первой линии задержки 5, при этом второй выход при ёмника двоичных фазоманипулированных сигналов 1-соединен с вторым входом блока управления 7, третий и четвертый входы которого соединены соответ ственно с выходом второго блока срав нения 4 и через вторую линию задержки 6 с выходом первого блока сравнения 3. Устройство работает следующим образом. Принятый двоичный фазоманипулированный сигнал поступает на первый приемника двоичных фазоманипулированных сигналов 1 и на первый вход анализатора формы входного сигнала 2, на; вторые входы этих устройств подается синхросигнал y(t), квазикогерентный входному. Синхросигнал y{t) подается также на блок управления 7 для синхронизации работы всего устройства. Если входной сигнал недеформирован, то на основном выходе приемника двоичных фазома нипулированных сигналов 1, подключенном к блоку управления , блокам срЖвйёнйя 3 и 4, появится послёдЬ вйтельность двоичных единиц и нулей-, соответствующая входному сигналу. На дополнительном выходе приемника двоичных фазоманипулированных .сиг налов 1, подключенном только к блоку управления 7, вырабатывается сигнал Q, означающий, что принятый бит-период недеформирован , Этот сигнал G, разрешает выход сигнала изблока управления 7 по первому выходу без корректировки, но с задержкой на один бит-период в блоке управления 7 На втором выходе блока управления 7 устанаёливается уровень, пбдТвёрждаю щий достоверность выдаваемой информации . Одновременновходной сигнал посту пает на анализатор формы входного .сигнала 2, который выделяет область -Г на границе двух соседних бит-периодов такой величины, чтобы обеспечить надежное обнаружение переходной области X при минимальной вероятност ошибки. Если переходная область А обнаруживается, то на выходе анализа тора формы входного сигнала 2 формируется импульс длительностью в половину бит-периода и соответствующий, например, уровню логической единицы. Сигнал с .го выхода приемни кадвоичных фазоманипулированных сиг налов 1, соответствующий предыдущему бит-Периоду входного сигнала, посту.пает .на один из входов блока сравнения 3, (эдновремённо на второй вход rto ступает сигнал с выхода анализатора формы входного сигнала 2; соответствугощий рёзулЁт-ату анализафЬрШГ в}56д ного сигнала в области Т на рс1йй Це между предыдущим и поступающим сигналами. С выхода блока сравнения 3 идентифицированный сигнал через линию задержки 6 на один бит-период поступает в блок управления 7. Сигнал с выхода анализатора .формы входного сигнала 2, соответствующий результату анализа формы входного сигнала в области t на границе между поступивиШм и последующим, сигналами, задерживается на один бит-период линией задержки 5 и поступает на вход блока сравнения 4 одновременно с cигнaлo i, соответствующий результату идентификаций последующего бит-периода, и далее в блок управления 7. Блок управления 7 при поступлении на Вход устройства недеформированных сигналов н аходится в первоначальном состЪянии; запрещающем корректировку правильно идентифицированных сигналов, поступающих с основного выхода приемника двоичных фазоманипулированных сигналов 1, сигналами, поступающими с линии задержки бис выхода блока сравнения 4. Если вслед за последним недеформированным бит-периодом на вход устройства поступает последовательность стертых бит-периодов Хц, где k 1,2,...п, то при работке .этих бит-периодов входного сигнала на основном выходе приемника двоичных фазоманипулированных сигналов 1 появляется сигнал, соответствующий логическому нулю, а на дополнительном выходе - импульс Q, соответствующий логической единице и означающий, что принятый бит-период стерт. При поступлении на вход устройства деформированного бит-периода Х в момент t импульс Q, поступая в блок управления 7, разрешает корректировку стертого бит-периода Х., в соответствии с результатом его идентификации, и с основного выхода блока управления 7 снимается откорректированный сигнал. Одновременно первый импульс О., соответствующий Х, подготавливает блок управления 7 та-, КИМ образом, что в случае приема следующего стертого бит-периода.XjV .и выдачи в момент времени tj на дополнительном выходе приемника двоич. ных фазоманипулированных сигналов 1 второго импульса Gl, подряд запрещается идентификация Х по Х, т.е. запрещается снятие сигнала с линии задержки 6 и разрешается и-дентификация поПоследующему, который поступит в момент времени tj. Если в это время приходит стертый бит-период X g и в блок управления 7 с дополнительного выхода приемника двоичных фазоманипулированных сигналов 1 в момент времени t, поступит третий импульс U подряд, то на втором выходе блока управления 7 появляется высокий уровень, соответствующий логической единице и означающий, что с первого выхода выдаются сигналы, соответствующие деформированным символам. Этот

Авторы

Даты

1979-05-05—Публикация

1976-09-14—Подача