Изобретение относится к области радиотехники и цифровой техники и может быть использовано при приеме, демодуляции и обработке фазоманипулированных сигналов спутниковых и радиорелейных линий связи.

Существующая отечественная и зарубежная элементная база, а также технология изготовления многослойных печатных плат 4-5 класса позволяют создать приемно-демодулирующие устройства, размещаемые в одном конструктиве, в частности на плате размера 6U, вставляемой в Евроблок типа "крейт" - с использованием шины VME.

Так в [1, патент №32346 от 20.02.2003 г. на полезную модель "Демодулятор фазоманипулированных сигналов"] предложен цифровой демодулятор, содержащий входное устройство со схемой автоматической регулировки усиления, аналого-цифровой преобразователь сигнала промежуточной частоты в цифровой код с преобразователем Гильберта и непосредственно демодулятор, выполненный на цифровых элементах.

Недостатком такого демодулятора является его одноканальность.

В [2, заявка №2004106426 от 04.03.04 г. на полезную модель "Многоканальное приемно-демодулирующее устройство..."] предложено устройство, содержащее последовательно соединенные радиоприемное устройство, аналого-цифровой преобразователь с цифровым кольцом автоматической регулировки усиления (АРУ) и преобразователь Гильберта, к выходу которого подключено n трактов цифровых демодулирующих устройств фазоманипулированных сигналов.

Недостатком такого устройства являются малые функциональные возможности, так как оно обеспечивает только демодуляцию n фазоманипулированных сигналов, но не обеспечивает операций предварительной обработки сигналов, таких как:

- помехоустойчивое декодирование;

- дифференциальное декодирование;

- дескремблирование;

- деперемежение;

- декодирование кодов Рида-Соломона.

Целесообразность расположения элементов, выполняющих эти операции, в одном конструктиве диктуется тем, что в существующих спутниковых системах связи практически все сигналы подвергаются указанным выше операциям на передающей стороне и только этап мультиплексирования/демультиплексирования характеризуется большим разнообразием вариантов.

Необходимость размещения функциональных устройств, выполняющих эти операции, в одном конструктиве с приемно-демодулирующим устройством диктуется также упрощением схемы соединений, т.к. после каждого демодулирующего устройства формируется 6-8-битовое мягкое решение в сопровождении тактовой частоты, что усложняет схему соединений, если эти функциональные модули будут размещены в другом конструктиве.

Целью изобретения является создание многоканального устройства приема, демодуляции и предварительной обработки сигналов в одном конструктиве и расширение его функциональных возможностей.

Для достижения указанной цели предлагается многоканальное приемно-демодулирующее устройство фазоманипулированных сигналов систем связи, содержащее последовательно соединенные радиоприемное устройство (РПУ) и блок аналого-цифрового преобразования (АЦП), выход которого подключен ко входам n каналов цифровых демодуляторов. Согласно изобретению в его состав введен блок управления устройством и отображения его состояния с персональной ЭВМ (ПЭВМ), обеспечивающий автоматическую настройку на сигнал с априорно неизвестными параметрами, выход которого через интерфейс шины VME подключен к управляющим входам РПУ, АЦП и n каналов цифровых демодуляторов, причем каждый из n каналов цифровых демодуляторов содержит демодулятор с мягким решением, выход которого подключен к входам параллельно соединенных перестраиваемых декодеру несистематических сверточных кодов (НСК), декодеру систематических сверточных кодов (ССК), декодеру решетчатых кодов и блочных турбокодов, подключенных к соответствующим входам мультиплексора, выход которого подключен к последовательно соединенным перестраиваемым дифференциальному декодеру, первому дескремблеру, деперемежителю, декодеру кодов Рида-Соломона и второму дескремблеру с соответствующими ключами для обеспечения режима транзита.

Подробное решение в литературе не описано, поэтому оно соответствует критериям новизны и изобретательского уровня.

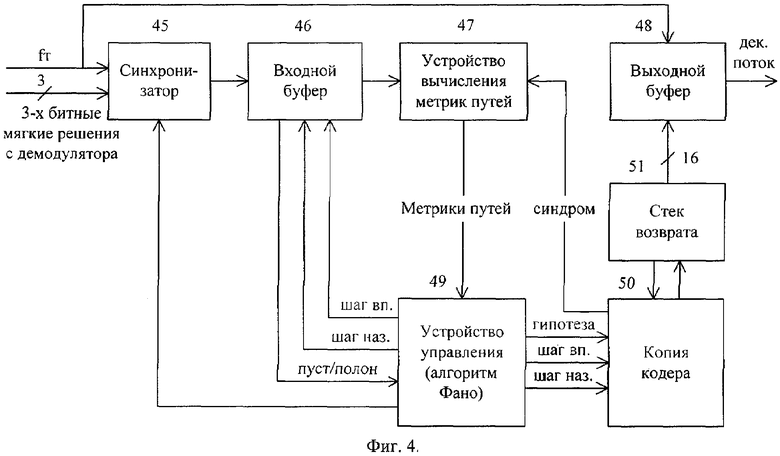

Функциональная схема многоканального устройства приема, демодуляции и обработки фазоманипулированных сигналов систем связи приведена на фиг.1.

Структурная схема универсального декодера НСК (декодера Витерби) приведена на фиг.2, функциональная схема декодера решетчатых кодов приведена на фиг.3, функциональная схема последовательного декодера ССК приведена на фиг.4, функциональная схема универсального мультипликативного дескремблера приведена на фиг.5.

В состав предлагаемого устройства входят последовательно соединенные РПУ (блоки: фильтр преселекторов - 1, усилитель системы АРУ - 2, детектор АРУ - 3, преобразователь частоты - 4, гетеродин - 5, полосовой фильтр - 6), блок АЦП (блоки: усилитель схемы АРУ - 7, АЦП - 8, цифровой детектор АРУ - 9, ЦАП - 10, генератор - 11, преобразователь Гильберта - 12). К выходу преобразователя Гильберта подключены n каналов, каждый из которых представляет собой последовательно соединенные цифровой демодулятор 13, набор помехоустойчивых декодеров (блоки: декодер несистематических сверточных кодов - 14, декодер решетчатых кодов (Trellis) - 15, декодер систематических сверточных кодов - 16, декодер блочных турбокодов - 17), мультиплексор 18, диф. декодер 19, дескремблер 20, деперемежитель 21, декодер кодов Рида-Соломона 22, второй дескремблер 23, блоки 19-23 имеют режим транзита с использованием соответствующих коммутаторов 24, 25, 26, 27, а также содержит последовательно соединенные блок программного обеспечения (ПО) 28 с ПЭВМ управления 29, интерфейс шины VME 30, выход которого подключен к управляющим входам РПУ, блока АЦП и ко входам n каналов цифровых демодуляторов.

Мультиплексор 18', ключи 24', 25', 26', 27', дифференциальный декодер 19,' универсальные самосинхронизирующиеся дескремблеры 20' и 23', а также деперемежитель 21' и декодер Рида-Соломона 22' реализованы на перепрограммируемой логической интегральной схеме (ПЛИС).

Устройство работает следующим образом. Входной сигнал в диапазоне частот 950-2050 МГц поступает на вход общего для всех каналов радиоприемного устройства. Там интересующая часть диапазона входного сигнала предварительно отфильтровывается перестраиваемым фильтром преселектора 1. Это необходимо для защиты от зеркального и побочных каналов приема. Далее сигнал поступает на регулируемый усилитель 2 системы АРУ приемника. Управляющий сигнал на усилитель 2 поступает с детектора АРУ 3. Далее сигнал поступает на преобразователь частоты 4, где перемножается с сигналом гетеродина 5. Для расширения рабочей полосы частот каждого канала демодулятора промежуточная частота выбрана равной 140 МГц. С помощью полосового фильтра 6 выделяется рабочая полоса частот (72 МГц). Полосовой фильтр 6 необходим для предотвращения наложений спектра при дискретизации сигнала. Групповой сигнал с выхода полосового фильтра 6 поступает на усилитель схемы АРУ 7. Коэффициент усиления усилителя 7 регулируется управляющим напряжением, которое поступает с выхода цифроаналогового преобразователя (ЦАП) 10. Управляющий код на ЦАП 10 поступает с выхода цифрового детектора АРУ 9. С выхода усилителя 7 сигнал промежуточной частоты поступает на вход АЦП 8 (12 разрядов). Тактовый сигнал для АЦП 8 обеспечивает генератор 11. Аналого-цифровое преобразование выполняется с использованием субдискретизации с частотой выборок 186,66 МГц. Таким образом, частота дискретизации составляет 4/3 от промежуточной частоты сигнала. Это обеспечивает максимальную ширину рабочего диапазона частот и предотвращает наложение спектров при дискретизации. Дальнейшая обработка сигнала производится в цифровом виде. Оцифрованный сигнал разделяется на квадратурные составляющие с помощью преобразователя Гильберта 12.

Затем оцифрованный групповой сигнал подается на n каналов цифровых демодуляторов. Каждый из n каналов содержит цифровой демодулятор 13'. В демодуляторах 13' осуществляется когерентная демодуляция фазоманипулированных сигналов (ФМ) и сигналов квадратурной амплитудной манипуляции (КАМ), а также оптимальная фильтрация по маске с различными коэффициентами крутизны ската. На выходе демодулятора 13' образуются выборки синфазного и квадратурного каналов, которые в сопровождении восстановленной тактовой частоты подаются на помехоустойчивые декодеры 14'-17'. С помощью мультиплексора 18' осуществляется выбор декодера несистематических сверточных кодов по алгоритму Витерби - 14', систематических сверточных кодов 16', декодера решетчатых кодов (Trellis декодер) 15' или декодера турбокодов 17' в зависимости от используемого в обрабатываемой системе связи типа помехоустойчивого (ПУ) кодирования. Турбодекодер 17' реализован на специализированной микросхеме фирмы AHA, остальные ПУ декодеры 14'-16' - на ПЛИС фирмы Xilinx. Параметры каждого ПУ декодера (образующие полиномы, относительная скорость кодирования, параметры выкалывания) также настраиваются. С выхода ПУ декодеров 14'-17' битовый поток поступает на последовательно соединенные дифференциальный декодер 19', универсальный самосинхронизирующийся дескремблер 20', деперемежитель 21', декодер кодов Рида-Соломона 22' и второй универсальный самосинхронизирующийся дескремблер 23'. Полиномы дескремблеров, параметры перемежения и блочного кодирования могут настраиваться. При необходимости отдельные этапы обработки можно исключать с помощью ключей 24', 25', 26', 27'. В результате обеспечивается оперативная адаптация параметров устройства под обрабатываемый сигнал.

Конструктивно устройство выполнено в виде модуля шины VME. Управление устройством и отображение его состояния осуществляет блок ПО 28 управляющей ПЭВМ 29 через интерфейс шины VME 30. Управляющая программа блок 29 в автоматическом режиме определяет вид модуляции, несущую и тактовую частоты, вид ПУ кодирования для каждого канала демодуляции, что обеспечивает автоматическую настройку на сигнал с априорно неизвестными параметрами.

Мягкие решения с выхода демодулятора 13 через коммутатор 31 поступают на устройство вставки "стертых" символов 32. Вставка "стертых" символов необходима для приведения перфорированных кодов к стандартному коду с относительной скоростью 1/2. Все параметры выколки в устройстве вставки "стертых" символов 32 полностью программируются, что позволяет одним декодером обрабатывать все варианты перфорированных кодов, полученных из базового кода с относительной скоростью 1/2. На выходе устройства вставки "стертых" символов 32 формируются мягкие решения квадратурных каналов I и Q, а также стробы Erase I и Erase Q, которые показывают, что текущий символ в соответствующем канале "стерт". При появлении "стертого" символа вычислитель метрик 33 формирует метрики только на основе одного, не "стертого" подканала. С выхода вычислителя метрик 33 значения четырех метрик поступают на процессор 34, устроенный так же, как и в прототипе. На выходе процессора 34 формируются данные о наиболее вероятных переходах на решетчатой диаграмме, которые поступают на устройство памяти выживших путей 35. Там данные о переходах на решетчатой диаграмме запоминаются, а затем для каждого выходного бита производится поиск наиболее вероятного пути на решетчатой диаграмме, начиная от самого раннего принятого символа к самому последнему. Решение о выходном символе декодера 14 принимается по большинству путей, соответствующих нулю или единице. Для определения синхронизации декодера 14 используется не логика неединогласия, а анализируется частота импульсов нормализации сумматоров ячеек ССВ процессора 34, что несколько снижает аппаратные затраты. Блок 36 обеспечивает ветвевую синхронизацию и устранение фазовой неоднозначности демодулятора 13. В блоке 37 производится оценка качества каналов.

Декодер решетчатых кодов 15 (фиг.3) реализован на ПЛИС по классической схеме и содержит последовательно соединенные коммутатор 38, декодер Витерби 39, кодер несистематических сверточных кодов (НСК) 40, решающее устройство 41, а также линию задержки 42, соединяющую выходы коммутатора 38 со вторыми входами решающего устройства 41 и входами устройства оценки качества канала 44 и систему ветвевой синхронизации и устранения неоднозначности 43, вход которой подключен к выходу блока 39, а выход ко второму входу коммутатора 38. Выход решающего устройства 41 подключен к третьему входу устройства оценки качества канала 44.

Декодер работает следующим образом. Мягкие решения квадратур I и Q с АЦП демодулятора 13 поступают на коммутатор 38, который служит для устранения неоднозначностей захвата демодулятора 13. Коммутатором 38 управляет система ветвевой синхронизации и устранения неоднозначности 43, которая по порядку меняет неоднозначности до тех пор, пока не будет достигнута синхронизация декодера Витерби 39. С помощью декодера Витерби 39 производится помехоустойчивое декодирование тех бит сигнального созвездия, которые были подвергнуты ПУ кодированию. С выхода декодера Витерби 39 декодированные биты поступают на кодер НСК 40, где заново кодируются. В результате на выходе кодера НСК 40 восстанавливаются кодированные биты сигнального созвездия, но уже с исправленными ошибками, которые поступают на решающее устройство 41. На решающее устройство 41 также поступают выборки синфазного и квадратурного каналов, задержанные в линии задержки 42. Линия задержки 42 служит для компенсации задержки в декодере Витерби 39 и в кодере НСК 40. В рещающем устройстве 41 на основании информации с выхода кодера НСК 40 и исходных канальных символов принимается решение о наиболее правдоподобном принятом символе. Устройство оценки качества канала 44 измеряет вероятность ошибки в канале, сравнивая информационные символы на входе и выходе ПУ декодера 15.

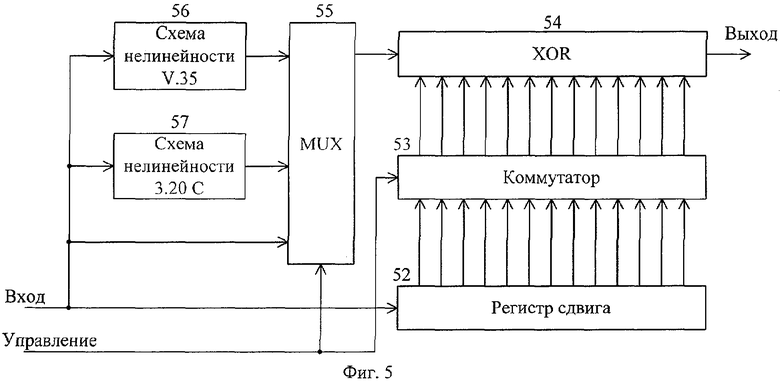

Универсальный декодер систематических сверточных кодов (ССК) 16 (декодер ФАНО), реализованный по последовательному алгоритму (фиг.4), содержит последовательно соединенные синхронизатор 45, входной буфер 46, устройство вычисления метрик путей 47, а также выходной буфер 48, вход которого соединен с первым входом синхронизатора 45, и последовательно соединенные устройство управления 49, копию кодера 50, второй выход которого подключен ко второму входу блока 47 и стек возврата 51, выход которого подключен ко второму входу блока 48, при этом четвертый и пятый выходы блока 49 подключены ко второму и третьему входам блока 46, пятый выход блока 49 подключен к третьему входу блока 45, второй выход блока 46 подключен ко входу блока 49, а ко второму его входу подключен выход блока 47, второй выход блока 51 подключен к четвертому входу блока 50.

Декодер 16 работает следующим образом. Мягкие решения демодулятора 13 урезаются до трех бит и подаются на синхронизатор 45. Трехбитного мягкого решения вполне достаточно, т.к. при переходе от 3-битного решения к 4-битному помехоустойчивость возрастает менее чем на 0,25 дБ, а сложность входного буфера 46 и устройства вычисления метрик 47 существенно возрастает. В синхронизаторе 45 осуществляется синхронизация входных данных по ребрам кодового дерева и вставка выколотых символов (для кодовых скоростей 3/4 и 7/8). При этом вместо выколотых символов вставляются символы с нулевыми метриками. При этом метрика текущего узла не изменяется и декодер 16 продолжает движение по ранее выбранному пути. Кроме того, в синхронизаторе 45 осуществляется перестановка кодовых ребер при работе с различными вариантами ССК кода. Далее информационные и проверочные символы с синхронизатора 45 поступают на входной буфер 46 и записываются в него по тактам информационной тактовой частоты. Входной буфер 46 необходим для исключения потерь входных данных, так как время декодирования символа в декодере Фано 16 существенно зависит от количества и взаимного положения ошибок во входной информации. Практически выяснено, что размер буфера 46 должен составлять несколько десятков тысяч символов и его дальнейшее увеличение значительного улучшения характеристик не дает.

С выхода входного буфера 46 мягкие решения поступают на устройство вычисления метрик путей 47. Наиболее просто его реализовать в виде постоянного запоминающего устройства (ПЗУ) с прошитой в него таблицей метрик. При последовательном декодировании значения метрик изменяются по логарифмическому закону. Практически установлено, что вполне достаточно семиразрядного представления метрик (диапазон значений от -64 до +63 в дополнительном коде). Вычисленные метрики подаются на устройство управления 49, реализующее алгоритм Фано. Там происходит выбор пути с наилучшей метрикой. Алгоритм Фано движется вперед по текущему пути до тех пор, пока метрика пути остается выше заданного порога. Если же метрика пути оказывается ниже порога, алгоритм возвращается назад и пробует другой путь. Устройство управления декодером 49 также постоянно отслеживает состояние входного буфера 46 и наличие синхронизации декодера 16. При пустом входном буфере 46 устройство управления 49 приостанавливает работу декодера 16 до поступления во входной буфер 46 недекодированных данных. В случае переполнения входного буфера 46 происходит полный сброс и пересинхронизация декодера 16. Если синхронизация отсутствует, устройство управления 49 изменяет фазу синхронизатора 45 до тех пор, пока правильная синхронизация не будет достигнута.

На основании анализа метрик путей формируется предполагаемое значение текущего информационного бита (гипотеза), которое подается на копию кодера 50. Изменяя отводы регистра сдвига в копии кодера 50, можно настроить декодер 16 на декодирование систематического сверточного кода с произвольными образующими полиномами. Вычисленный в копии кодера 50 синдром подается на устройство вычисления метрик 47 для выбора пути с лучшей метрикой. При движении вперед старые данные из копии кодера 50 подаются в стек возврата 51. Если происходит возврат назад, в копию кодера 50 загружаются старые данные из стека 51. Глубина возврата (т.е. количество символов, сохраняемых в стеке) обычно выбирается примерно в 5 раз больше длины кодового ограничения используемого кода. Для декодирования ССК кода с относительной скоростью 7/8 и длиной кодового ограничения 104 достаточно глубины возврата в 500 символов.

Если число ошибок в канале не слишком велико, то алгоритм Фано в основном делает шаги вперед. В результате стек возврата 51 постепенно заполняется. При полном заполнении стека возврата 51 последние информационные символы из него переписываются в выходной буфер 48. Данные из выходного буфера 48 подаются на выход декодера Фано 16 по тактам информационной тактовой частоты.

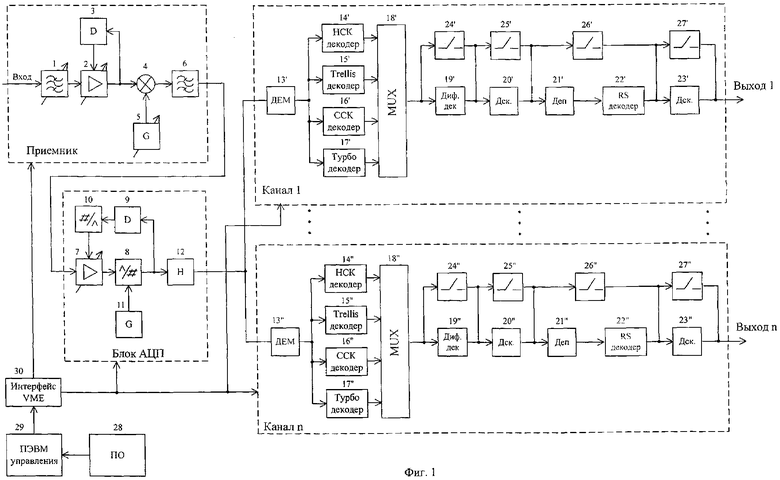

Универсальный самосинхронизирующийся дескремблер 17 (фиг.5) содержит регистр сдвига 52 длиной 32 бита, коммутатор 53 на 32 бита, схему ИСКЛЮЧАЮЩЕЕ ИЛИ 54, мультиплексор 55, схемы нелинейности 56 и 57 для дескремблеров V35 и 3.20С соответственно. При задании произвольного линейного самосинхронизирующегося скремблера с помощью коммутатора 53 отводы регистра сдвига, соответствующие полиному скремблера, подаются на логический элемент исключающее ИЛИ 54. С помощью мультиплексора 55 на логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 54 также подается исходный входной сигнал. В результате образуется схема линейного самосинхронизирующегося дескремблера. При задании нелинейного дескремблера V.35 или 3.20С с помощью мультиплексора 55 на логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 54 подаются данные с выхода соответствующей схемы нелинейности 56 и 57, а с коммутатора 53 - данные с 3 и 20 отводов регистра сдвига. В результате в схему дескремблера вносится дополнительная нелинейность.

Дифференциальный декодер 19, деперемежитель 21, декодер кодов Рида-Соломона 22 и аддитивный дескремблер 20, 23 выполнены на ПЛИС по классическим схемам в соответствии со спецификациями IESS 308, 309, 310 и EN300421.

В настоящее время в РНИИРС создано и изготовлено двухканальное устройство приема, демодуляции и обработки фазоманипулированных сигналов в одном конструктиве (ПДМ-2К ИУЯД.467747.061). Фото устройства приведено на фиг.2.

В результате использования предлагаемого построения устройство обеспечило следующий эффект:

- прием сигналов в диапазоне частот 950-2150 МГц и преобразование в сигнал ПЧ 140 МГц полосой 48 МГц; оптимальную фильтрацию;

- обзор панорамы в диапазоне частот 950-2150 МГц с визуализацией на мониторе и возможностью настройки на любой сигнал;

- преобразование сигнала ПЧ 140 МГц в 12-разрядный цифровой код;

- цифровую демодуляцию сигналов с фазовой модуляцией ФМ2, ФМ4, ФМ4С, ФМ8, KAM16 с цифровой фильтрацией и коррекцией амплитудно-частотной характеристики (АЧХ) и группового времени запаздывания (ГВЗ);

- демодуляцию сигналов при следующих отношениях сигнал/шум ФМ2≥0 дБ; ФМ4, ФМ4С≥6 дБ; ФМ8≥10,5 дБ; KAM16≥12 дБ;

- диапазон скоростей от 1,5 кбод до 10 Мбод;

- дифференциальное декодирование цифровых потоков;

- помехоустойчивое декодирование практически всех известных несистематических кодов по алгоритму Витерби с мягким решением;

- помехоустойчивое декодирование практически всех известных систематических кодов по алгоритму (усеченный алгоритм ФАНО) с мягким решением;

- дескремблирование аддитивных и мультипликативных скремблеров, в том числе и по рекомендациям V35 и V35c;

- деперемежение цифровых потоков по матричному и регистровому закону;

- декодирование известных кодов Рида-Соломона;

- декодирование турбокодов;

- построение помехоустойчивых декодеров, дифференциальных декодеров, деск-ремблера, деперемежителей, декодера Рида-Соломона на ПЛИС и микропроцессорах обеспечивает возможность программной обработки по модели сигнала и адаптации к изменяющейся радиообстановке;

- компоновку устройства в одном конструктиве с оптимальным составом ПЛИС, ОЗУ, ПЗУ и микропроцессоров.

Испытания устройства по реальным сигналам показали положительные результаты.

Помехоустойчивый декодер НСК выполнен на ПЛИС по схеме, приведенной в заявке №2003129224 от 30.09.03 г. на полезную модель "Универсальный помехоустойчивый декодер НСК" и реализует "Способ обработки цифровых потоков по модели сигнала и перепрограммируемым схемам электрическим" по патенту №2220498 от 27.12.03 г. На этой же ПЛИС реализован декодер ССК методом изменения схемы и создания загрузочного модуля под декодер ССК.

На ПЛИС по этому же способу реализованы дифференциальный декодер, дескремблер, деперемежитель, декодер Рида-Соломона.

Если все данные о сигнале заранее известны, то эти данные и являются моделью сигнала. Если же данные априори о сигнале неизвестны, то они добываются в процессе анализа и по этим данным синтезируется модель сигнала.

Поскольку устройство в целом реализует "Способ обработки цифровых потоков по модели сигнала и перепрограммируемым схемам электрическим" (патент №2220498), то в состав устройства введены блок ПО 28, ПЭВМ управления 29 и интерфейс шины VME 30.

В блоке ПО 28 хранятся схемы электрические на ПЛИС, ОЗУ, ПЗУ, микропроцессорах, выполненные в виде загрузочных модулей под сигналы с известной структурой. С помощью меню выбирается загрузочный модуль под интересующий сигнал и запускается программа, в результате которой устройство автоматически настраивается на сигнал и производится его обработка.

В случае отсутствия априорных данных о сигнале производится поэтапный анализ его структуры, по данным которого синтезируется модель сигнала, создается схема электрическая в виде загрузочного модуля в блоке ПО 28 и дальнейшая обработка ведется аналогично по модели сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО ОБРАБОТКИ СИГНАЛОВ ЛИНИЙ СВЯЗИ ПО МОДЕЛИ СИГНАЛА И ПЕРЕПРОГРАММИРУЕМЫМ ЭЛЕКТРИЧЕСКИМ СХЕМАМ | 2005 |

|

RU2317641C2 |

| ИМИТАЦИОННОЕ ОБОРУДОВАНИЕ ДЛЯ ПРОВЕРКИ ПРИЕМНОЙ АППАРАТУРЫ ЛИНИЙ СВЯЗИ С ЧАСТОТНЫМ, ВРЕМЕННЫМ И КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 2005 |

|

RU2277308C1 |

| СПОСОБ БЫСТРОЙ АВТОМАТИЧЕСКОЙ НАСТРОЙКИ НА СИГНАЛ И ЕГО ОБРАБОТКИ | 2004 |

|

RU2263394C1 |

| МНОГОФУНКЦИОНАЛЬНАЯ СИСТЕМА ПРИЕМА, ДЕМОДУЛЯЦИИ И ОБРАБОТКИ СИГНАЛОВ I-IV УРОВНЕЙ ИЕРАРХИЧЕСКОГО УПЛОТНЕНИЯ | 2001 |

|

RU2224375C2 |

| СТАНЦИЯ ТЕХНИЧЕСКОГО КОНТРОЛЯ СИГНАЛОВ СПУТНИКОВЫХ ЛИНИЙ СВЯЗИ | 2002 |

|

RU2224373C2 |

| УСТРОЙСТВО ДЛЯ ДЕМОДУЛИРОВАНИЯ И ДЕКОДИРОВАНИЯ ВИДЕОСИГНАЛОВ | 1996 |

|

RU2172566C2 |

| СПОСОБ ДЕКОДИРОВАНИЯ СВЕРТОЧНЫХ КОДОВ | 2012 |

|

RU2516624C1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ВИДЕОСИГНАЛОВ, КОДИРОВАННЫХ В РАЗНЫХ ФОРМАТАХ | 1996 |

|

RU2171548C2 |

| СПОСОБ ФОРМИРОВАНИЯ И ПЕРЕДАЧИ ДВУХКАНАЛЬНЫХ, В ТОМ ЧИСЛЕ СТЕРЕОФОНИЧЕСКИХ, СИГНАЛОВ ЗВУКОВОГО СОПРОВОЖДЕНИЯ, РАДИОВЕЩАНИЯ, ДАННЫХ И КОМАНД УПРАВЛЕНИЯ В СЕТЯХ ЭФИРНОГО И КАБЕЛЬНОГО ВЕЩАНИЯ (ВАРИАНТЫ), СИСТЕМА ПЕРЕДАЧИ СИГНАЛОВ МНОГОКАНАЛЬНОГО ЗВУКОВОГО СОПРОВОЖДЕНИЯ, РАДИОВЕЩАНИЯ, ДАННЫХ И КОМАНД УПРАВЛЕНИЯ В СЕТЯХ ЭФИРНОГО И КАБЕЛЬНОГО ВЕЩАНИЯ | 1999 |

|

RU2163420C2 |

| Кодек для системы связи с многократной фазовой модуляцией | 1987 |

|

SU1629992A1 |

Изобретение относится к области радиотехники и цифровой техники и может быть использовано при приеме, демодуляции и предварительной обработке фазоманипулированных сигналов систем связи. Многоканальное приемно-демодулирующее устройство, содержащее радиоприемное устройство, аналого-цифровой преобразователь с цифровым кольцом автоматической регулировки, преобразователь Гильберта и n каналов цифровых демодуляторов, в каждый из которых введены набор помехоустойчивых декодеров, мультиплексор, дифференциальный декодер, первый дескремблер, деперемежитель, декодер кода Рида-Соломона, второй дескремблер, каждый из цифровых блоков имеет режим транзита. Технический результат обеспечивает возможность создания различной конфигурации обработки цифровых потоков. 5 ил.

Многоканальное приемно-демодулирующее устройство фазоманипулированных сигналов систем связи, содержащее последовательно соединенные радиоприемное устройство и блок аналого-цифрового преобразования (АЦП), выход которого подключен ко входам n каналов цифровых демодуляторов, отличающееся тем, что в его состав введен блок управления устройством и отображения его состояния с ПЭВМ, обеспечивающий автоматическую настройку на сигнал с априорно неизвестными параметрами, выход которого через интерфейс шины VME подключен к управляющим входам радиоприемного устройства, АЦП и n каналов цифровых демодуляторов, причем каждый из n каналов цифровых демодуляторов содержит демодулятор с мягким решением, выход которого подключен к входам параллельно соединенных перестраиваемых декодеру несистематических сверточных кодов, декодеру систематических сверточных кодов, декодеру решетчатых кодов и декодеру блочных турбокодов, выходы которых подключены к соответствующим входам мультиплексора, выход которого подключен к последовательно соединенным перестраиваемым дифференциальному декодеру, первому дескремблеру, деперемежителю, декодеру кодов Рида-Соломона и второму дескремблеру с соответствующими ключами для обеспечения режима транзита.

| Микроманипулятор | 1934 |

|

SU41217A1 |

| Барабан для обмолота растений, например, конопли | 1932 |

|

SU32246A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| СПОСОБ ОБРАБОТКИ ЦИФРОВЫХ ПОТОКОВ ПО МОДЕЛИ СИГНАЛА И ПЕРЕПРОГРАММИРУЕМЫМ СХЕМАМ ЭЛЕКТРИЧЕСКИМ | 2001 |

|

RU2220498C2 |

| US 6882636 A, 19.04.2005. | |||

Авторы

Даты

2007-08-27—Публикация

2005-05-13—Подача