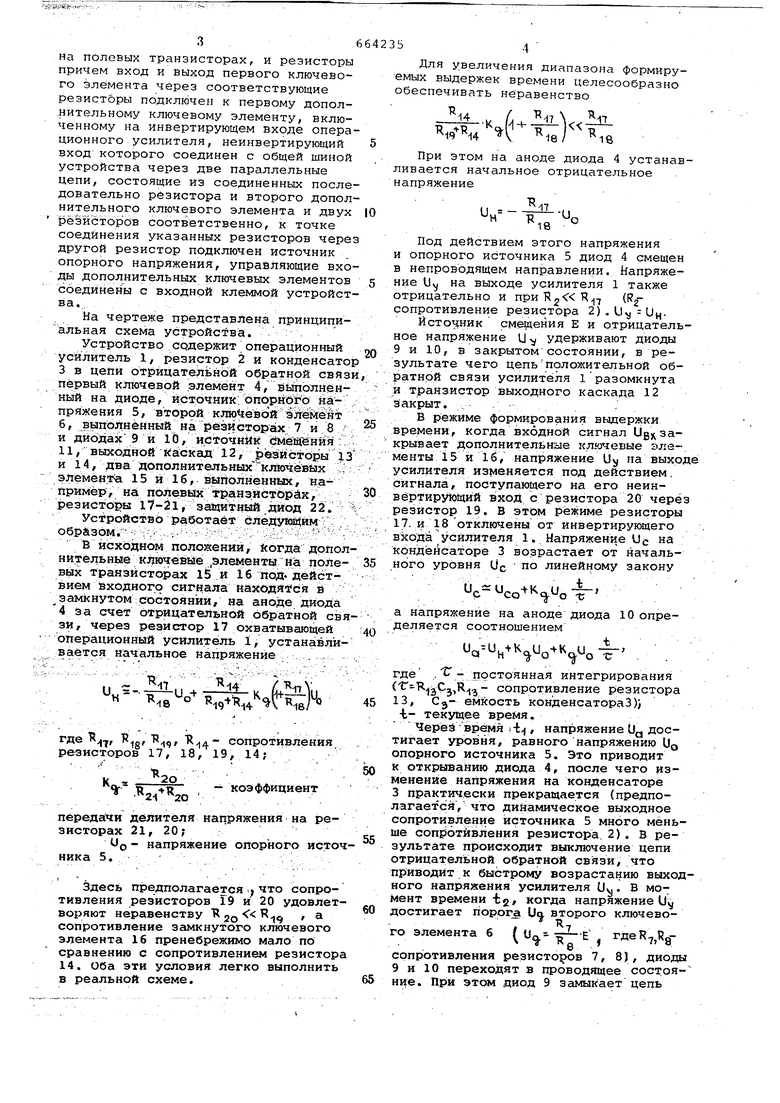

(54) РЕЛЕ ВРЕМЕНИ 3 , на полевых транзисторах, и резисторы вход и выход первого ключевого элемента через соответствующие резисторы подключен к первому допол.нительному ключевому элементу, включенному на инвертирующем входе опера ционного усилителя, неинвертирующий вход которого соединен с общей шиной устройства через две параллельные цепи, состоящие из соединенных после довательно резистора и второго допол нительного ключевого элемента и двух резисторов соответственно, к точке соединения указанных резисторов чере другой резистор подключен источник опорного напряжения, упрайляющие вхо ды дополнительных ключевых элементов соединены с входной клеммой устройст ва. На чертеже представлена принципиальная схема устройства. Устройство содержит операционный усилитель 1, резистор 2 и конденсато 3 в цепи отрйца ел11нЬй обратной свя первый ключевой элемент 4, вьтолненный на диоде, источник опорного напряжения 5, второй клю 1евой эяемент 6, выполненный на резисторах 7 и 8 и диодах 9 и 10, источник 11, выходной каскал 12, резисторы 1 и 14, два Дополнитель ключевых . элемента 15 и 16, выполненных, например, на полевых -rpaHaHCTOpcix, резисторы 17-21, защитный диод 22 Устройство работает следующим образом. . В исходном положении, Когда допол нительные ключевые .элементы на поле вых транзисторах 15 и 16 под-действием входного сигнала иаходя ся и замкнутом состоянии, на аноде диода 4 за счет отрицательной обратной св зи, через резистор 17 охватывающей операционный усилитель 1, устанавли вается начальное напряжение . и где R, 1с,Т-,9 сопротивления резисторов 17, 18, 19, 14; - коэффициент 2.20 передачи делителя напряжения на резисторах 21, 20; UQ - напряжение опорного исто ника 5. . Здесь предполагается - что сопротивления резисторов 19 и 20 удовлет воряют неравенству сопротивление замкнутого ключевого элемента 16 пренебрежимо мало по сравнению с сопротивлением резистор 14. Оба эти условия легко выполнить в реальной схеме. 5 Для увеличения диапазона формирумых выдержек времени целесообразно беспечивать неравенство Н ( -«Лсс 19.4П При этом на аноде диода 4 устанавивается начальное отрицательное апряжение Под действием этого напряжения и опорного источника 5 диод 4 смещен в непроводящем направлении. Йапряжение и( на выходе усилителя 1 также отрицательно и Сг сопротивление резистора 2).Uv|:Un. Источник смещения Е и отрицательное напряжение U удерживают диоды 9 и 10, в закрытом состоянии, в результате чего цепьполохоттельной обратной связи усилителя 1 разомкнута и транзистор выходного каскада 12 закрыт. В режиме формирования выдержки времени, когда входной сигнал Ugxзакрывает дополнительные ключевые эле-, менты 15 и 16, напряжение Uy на выходе усилителя изменяется под действием, сигнала, поступающего на его неинвёртируйщий вход с резистора 20 через резистор 19. В этом режиме резисторы 17. и 18отключены от инвертирукадего входа усилителя 1. Напряжение Uc на кондёйсаторе 3 возрастает от начального уровня (Jc по линейному закону IJc-Jco- Joа напряжение на аноде диода 10 определяется соотношением WVo S o-l- . . где .-постоянная интегрирования (,R - сопротивление резистора 13, Сд- емкость конденсатораЗ); -t- текзоцее время. Через время -fc, напряжение Ug достигает уровня, равного напряжению UQ опорного источника 5. Это приводит к открыванию диода 4, после чего изменение напряжения на конденсаторе 3 практически прекращается (предполагается,что динамическое выходное сопротивление источника 5 много меньше сопротивления резистора 2). В результате происходит выключение цепи отрицательной обратной связи, что приводит к быстрому возрастанию выходного напряжения усилителя Uy. В момент времени -fcg, когда напряжение Uy достигает порога Ua второго ключево R го элемента 6 ( д.- , ъ асопротивления резисторов 7, 8), диоды 9 и 10 переходят в проводящее состоя- ние. При этсж диод 9 замыкает цепь 5 . положительной обратной связи операционного усилителя 1, под действием которой усилитель переходит в релейный режим и еговыходное напряжение Uv, скачком достигает уровня поло жительного насыщения. Скачок напряжения Uv) через диод 10 передается- па базу транзистора выходного каскада 12, на коллекторе которого возникает отрицательный перепад напряжения, свидетельствующий об окончании выде ки времени. Таким образом, .за время выдержки времени напряжениеУна аноде диода 4 изменяется от начального уровня UK до напряжения Un открывания второго ключевого элемента б. Пренебрегая интервалом времени Л.Ь от начала открывания диода 4 (t) до момента включения положительной обратной связи через диод 9 (-tg) можем найти выдержку времени Т 4. из следующего соотношения Отсюда «Э- т.е. выдержка времени не зависит от напряжения опорного источника OQ. Перевод реле времени в исходное положе.ние осуществляется переключением входного сигнала, в результате чего дополнительные ключевые элементы 15 и 16 переходят в замкнутое сое тояние. При этом к инвертирующему входу усилител 1 подключаются резис торы 17 и 18, обеспечивающие работы усилителя в режиме ацериолического звена с постоянной времени Tgsft -C поэтому время восстановления Tg еле времени определяется.постоянной Т и допустимой погрешностью установления начального уровня Оц второго доподнительного ключевого элемента. Отметим, что применение транзисторного ключа 16 позволяет yipaBHHTb эквивалентные сопротивления на вгсода 5 операционного усилителя как в режиме формирования выдержки времени ( RJQ), так и в режиме восстановления 11 благодаря чему сни -П 18жается погрешность реле от входных токов операционного усилителя. Формула изобретения Реле времени, содержащее операционный усилитель с последовательно включенными резистором и конденсатором в цепи отрицательной обратной связи, к точке соединения которых . между собой через первый ключевой элемент подключен источник опорного напряжения, выход операционного усилителя через второй ключевой элемент, подключенный к источнику смещения, соединен с неинвертируювдим входом оп ерационмого усилителя и входом выходного каскада, резистора на инвертирующем и нейнвертирующем входах операционйогб усилители, ъ т л и 4 а ю at е е ся тем, что, с целью повышения точности выдержки времени, в него введены два дополнительных KJ eBbJx элемента, выполненные, напрймер, на ;пЬле$ых :трё1нзисторах, и резисторы, причем вход и выход hepврго ключевого элемента через соответствующиё резисторы подключен к первому дополнительному ключевому элементу, включенному на инвертирую-. щем входе операционного усилителя, нёинвертирующий вход которого соединен с общей шиной устройства через две параллельные цепи, состоящие из соединенных последовательно резистора и второго дополнительного ключевого элемента и двухрезисторов соответственно, к точке соединений указанных резисторов ч.ерез другой резистор подключен источник опорного напряжения, управляющие входы доцолнительных ключевых элементов соединены с входной клеммой устрЬйства.

18 -С1

П

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Реле времени | 1975 |

|

SU657476A1 |

| Аналого-цифровой интегратор | 1977 |

|

SU732905A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СТЕКЛООЧИСТИТЕЛЕМ ТРАНСПОРТНОГО СРЕДСТВА (ЕГО ВАРИАНТЫ) | 1992 |

|

RU2040417C1 |

| Компаратор для релейной защиты | 1990 |

|

SU1797092A1 |

| Устройство для управления четырехфазным двигателем переменного тока | 1980 |

|

SU886182A1 |

| Устройство для моделирования тиристора | 1983 |

|

SU1091190A1 |

| Реле времени периодических включений | 1980 |

|

SU868871A1 |

| Устройство для контроля пламени | 1983 |

|

SU1129467A1 |

| Многофазное реле минимального и максимального напряжения | 1980 |

|

SU904069A1 |

| Устройство для моделированияиМпульСНОгО дАТчиКА чАСТОТы ВРАщЕНия | 1979 |

|

SU849245A1 |

Авторы

Даты

1979-05-25—Публикация

1975-11-05—Подача