ход которого соединен с входом счетной декады старшего разряда, выход :Счетной декады младшего разряда через инвертор соединен с другим (входоМ третьего логического элемента И-НЕ, а выход цифро-анаЛОГ01ВОГО преобразователя подключен к другим .входам нуль-.органов.

Кроме того, в устройство донолнительно введены две счетные декады младшего разряда и две счетные декады старшего разряда, четыре лопичеоких элемента И и триггер улра-вления, первый выход которого подключен к одним вxoдa м первого и второго логических элементов И, второй выход триггера у пра1вления соединен с одними входами третьего « четвертого логических элементов И, другие входы первого и третьего логических злементов И подключены к выходу третьего логического элемента И-НЕ, другие входы второго и четвертого логических элементов И соединены с выходом первого логического элемента И-НЕ, выходы первого и третьего логических элементов И подключены к входам соответствующих дополнительных счетных декад старшего разряда, а выходы второго и четвертого логических элементов И соединены с входами соответствующих дополнительных счетных декад младшего разряда.

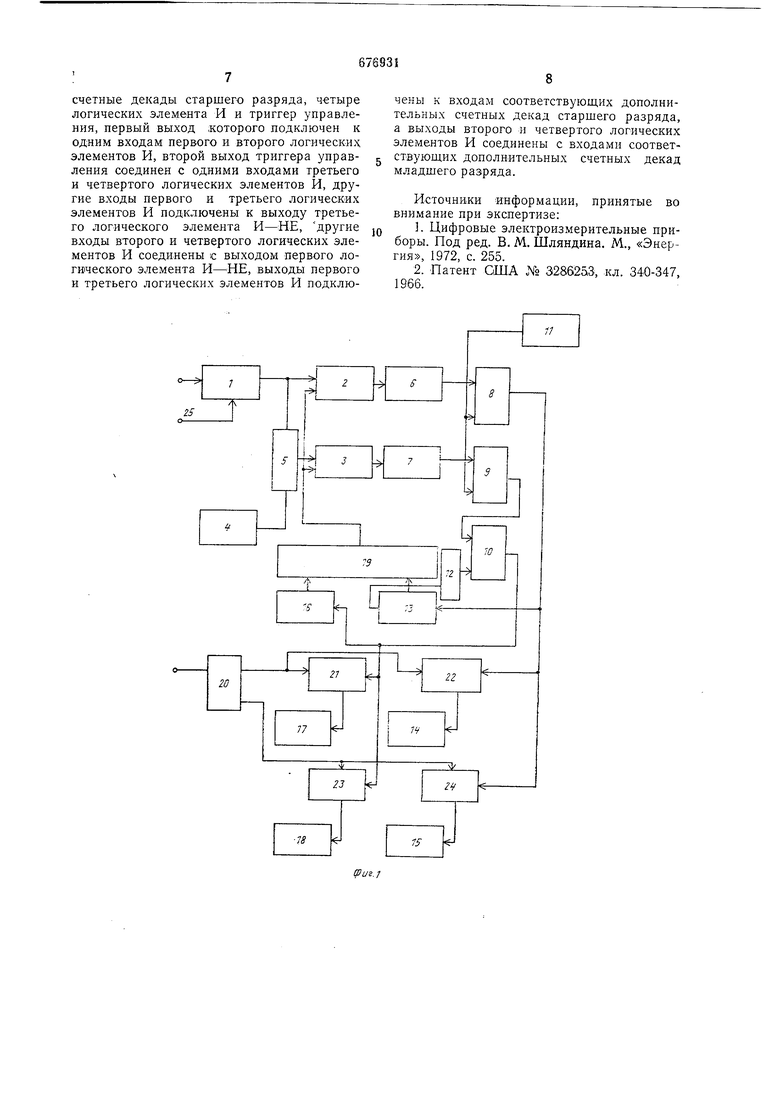

На фнг. 1 приведена блок-схема цифрового устройства для измерения параметров ударного нмпульса; на ф,иг. 2 и 3 - эпюры, поясняющие p aidory устройства.

Цифровое устройство для измерения параметров ударного км.пульса содержит интегратор / с логическим управлением, нуль-органы 2 к 3, источник опорного напряжения, соединенный с делителем 5 напряжения, формирователи 5 и 7 сигнала, логические элементы И-НЕ 5, 9 и 10, генератор // опорной частоты, инвертор 12, счетные декады 13-15 младшего разряда, счетные декады 16-18 старшего разряда, цифро-аиалоговый преОбразователь 19, триггер управления 20 и логические элементы И 21-S4.

Устройство работает следующим образом..

В начальный момент импульсом (фиг. 2 б), приходящим на шину «Сброс (не показана), счетные декады 13-15 младшего разряда и счетные декады 16- 18 старшего разряда устанавливаются в положение «О, на выходе цифро-аналогового преобразователя 19 образуется напряжение, равное нулю. При измерении пикового з-на-чения ударного импульса на управляющем входе 25 интегратора 1 с логическим отравлением отсутствует управляющий сигнал. При этом интегратор / с логическим улравлевие.м работает в режиме усиления. Выход интегратора 1 с логическим управлением соел1Инен непосредственно с одним входом нуль-органа 2 и чергз

делитель 5 напряжения с одним входом нуль-органа 3. На другие входы нуль-органов 2 и 3 поступает напряжение с выхода цифро-аналогового преобразователя 19.

На выходе нуль-органов 2 и 5 образуется положительный перепад напряжения, если входное .напряжение превышает нулевой уровень. Формирователи 6 н 7 сигнала преобразуют этот положительный перепад напряжения в сигнал, необходимый для упр авления логическими элементами И-НЕ 5, 9 и 10, логическая единица. Логические элементы И-НЕ 8, 9 vi 10 пропускают на входы счетных декад 13 и 16 младщего и старшего разрядов Импульсы с выхода генератора 11 опорной частоты. Напряже.ние на выходе цифро-аналогового преобразователя 19 повышается до тех пор, пожа не сравняется с измеряемым входным напряжением (фиг. 2а). При этом нуль-органы 2 Vi 3 будут иметь на выходах отрицательное напряжение, на выходах формирователей 6 и 7 сигнала появляется напряжение, соответствующее логическому нулю, и импульсы счета с генератора 11 опорной частоты на входы счетных декад 13 и 16 младшего и старшего разрядов не поступают, так как логические элементы И-НЕ 8, 9 н 10 закрыты.

При увеличении измеряемого входного нанряжения в счетные декады 13 и 16 младшего и старщего разрядов вновь будут поступать имтульсы до выравнивания напряжения на выходе цифро-аналогового преобразователя 19 с измеряемым входным напряжением.

При уменьшении измеряемого входного напряжения импульсы счета с генератора // опорной частоты в счетные декады 13 и 16 младщего и старшего разрядов не поступают, и напряжение на выходе цифро-аналогового преобразователя 19 остается на прежнем уровне до тех пор, пока на щину сброса не поступит импульс сброса или .входное измеряемое напряжение вновь не начнет увеличиваться и не превысит ранее измеренный уровень напряжения. Для повышения быстродействия устройства и для обеспечения возможности измерения импульсов малой длительности в устройстве используется принцип параллельного поступления счетных импульсов на входы счетных декад 13 и 16 младшего и старшего разрядов.

Измеряемый входной сигнал поступает непосредственно на вход нуль-органа 2. выходное .напряжение которого управляет поступлением счетных импульсов на счетн 1о декаду 13 младшего разряда. На вход нуль-органа 3, заправляющего счетной декадой 16 старщего разряда, из.меряемое напряжение поступает с коэффициентом передачи 0,85-0,9. Значение резисторов делителя 5 напряжения подобраны таким образом, что по окончании поступления счетных импульсов 1В счетную декаду 16 старшего разряда (фиг. 2в) на вход счетной декады 13 младшего разряда до момента сравнения наяряжений постулит еще 10- 15 импульсов (фиг. 2г).

Тажим образом, иуль-орган 5 сработает раньше, чем нуль-орган 2, и на вход счетной декады 16 старшего разряда кмпульсы могут поступать только с выхода счетной декады 13 младшего разряда через логичеокий элемент 10 и инвертор 12.

В момент сравнения измеряемого входного напряжения с выхода цифро-аналогового преобразователя 19 счетные имлульсы перестают поступать и на вход счетной декады 13 младшего разряда.

При работе устройства в режвме измерения плош;ади нарастания и шада импульса напряжения измеряемый импульс ударного ускорения, имеюш,ий один экстремум (фиг. За), поступает на вход интегратора / с логическим управлением, на у|Правляюш;ий вход которого одновременно подается прямоугольный импульс (фиг. 36) длительностью, равной длительности измеряемого импульса на нулевом уровне. При этом разрывается цепь обратной связи интегратора / с логическим упра/влением, который из режима усиления переходит в режим интегратора. На выходе интегратора / с логическим управлением появляется напряжение, пропорциональное площади измеряемого импульса (фиг. 30).

Сигнал с выхода интегратора / с логичеок|им управлением измеряется а)Налогично из;мерению пикового значения импульса, описанного ранее (фиг. 3 г, д, е).

До момента прохождения максимума измеряемого импульса напряжения триггер управления 20 находится в нулевом состояНИИ, при этом положительный уровень напряжения (фиг. Зж) с инвертированного выхода триггера управления 20 подается на одни входы логичеак1их элементов И 21 и 22, на другие входы которых поступают импульсы высокой частоты с выходов логических элементов И-НЕ 8 и 10.

С выходов логических элеметов И 21 ц 22 информация о площади нарастания импульсного напряжения в последовательнопараллельном коде подается в счетные декады 14 и 17 (фиг. Зз, ы). При прохождении максимума измеряемого напряжения на установочный вход триггера управления 20 приходит импульс (фиг. З/с), который О1пр01кидывает триггер управления 20, на входах логических элементов И 23 -я 24 образуется положительный потенциал (фиг. 3л), а на входах логических элементов И 21 22 - нулевой потенциал (фиг. Зж). В результате этого импульсы высокой частоты начинают поступать с выходов логических элементов И-НЕ 8 и JO через логические элементы И 23 и 24 на входы счетных декад 15 и .18, которые к

фиксируют вели1чину площади спада иипульсного напряжения (фиг. 3 м, н).

По окончании измерения импульса на управляющий ВХ01Д интегратора 1 с логическим управлением подается нулевой потенциал, и интегратор / с логическим управлением разряжается до нулевого уровня.

В результате цикла измерения в трех счетных декадах младш-его ,и старшего разрядов запишется информация о всей площади измеряемого импульсного напряжения (счетные декады 13 и 16), площади нарастания (счетные декады 14 и 17) и площади спада (счетные декады 15 и 18) импульсного .напряжения.

Параллельная работа счетных декад младшего и старщего разрядов обеспечивает повышение бЫ)Стродействия работы всего устройства в 3-4 раза.

Время одного измерения составляет 30-40 млсек при частоте следования импульсов с генератора опорной частоты 1 мГц.

Ожидаемый экономический эффект от внедрения устройства в народном хозяйстве составляет ориентировочно 300 тыс. руб. (

Формула изобретения

1.Цифровое устройство для измерения параметров ударного импульса, содержащее интегратор с логическим управлением, выход которого соединен с одним входом первого нуль-органа и через делитель напряжения - с одним входом второго нуль-органа, выходы нуль-органов соединены с формирователем сигнала, генератор опорной частоты, счетные декады младшего и старшего разрядов, выходы которых подключены к цифро-аналоговому преобразователю, и источник опорного напряжения, соединенный с делителем напряжения, о тличающееся тем, что, с целью повышения точности измерения, в него введены три логических элемента и инвертор, выходы формирователей сигнала подключены к одним входам первого и второго логических элементов И-НЕ, другие входы которых соединены с выходом генератора опорной частоты, выход первого логического элемента И-НЕ соединен с входом счетной декады младшего разряда, выход второго логического элемента И-НЕ подключен к одному входу третьего логического элемента И-НЕ, выход которого соединен с входом счетной декады старшего разряда, выход счетной декады младшего разряда через инвертор соединен с другим входом третьего логического элемента И-НЕ, а выход цифро-аналогового преобразователя подключен к другим входам нуль-органов.

2.Устройство по п. 1, отличающеес я тем, что в него дополнительно введены две счетные декады младшего разряда и две

счетные декады старшего разряда, четыре логических элемента И и триггер управления, первый выход которого подключен к одним входам первого и второго логических элементов И, второй выход триггера управления соединен с одними входами третьего и четвертого логических элементов И, другие входы первого и третьего логических элементов И подключены к выходу третьего логического элемента И-НЕ, другие входы второго и четвертого логических элементов И соединены с выходом первого логи1ческого элемента , выходы первого и третьего логических элементов И подключекы к входам соответствующих дополнительных счетных декад старшего разряда, а выходы второго и четвертого логических элементов И соединены с входами соответствующих дополнительных счетных декад младшего разряда.

Источники информации, принятые во внимание при экспертизе:

1.Цифровые электроизмерительные приборы. Под ред. В. М. Шляндина. М., «Энергия, 1972, с. 255.

2.Патент США № 3286253, .кл. 340-347, 1966.

а

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения ударных импульсов с защитой от помех | 1974 |

|

SU676932A1 |

| Устройство для измерения одиночных и многократных ударных импульсов | 1974 |

|

SU678434A1 |

| Цифровое устройство для измерения импульсных напряжений | 1975 |

|

SU676933A1 |

| Цифровое устройство для измерения параметров ударного импульса | 1980 |

|

SU947815A1 |

| Устройство для динамического зондирования грунта | 1986 |

|

SU1344861A1 |

| Устройство для испытания изделий на ударные нагрузки | 1981 |

|

SU968659A1 |

| Аналого-цифровое устройство для измерения амплитуды механических колебаний при резонансе | 1978 |

|

SU715939A1 |

| ИНТЕНСИМЕТР | 1995 |

|

RU2146061C1 |

| Цифровой измерительный неуравновешанный мост | 1978 |

|

SU789767A1 |

| Измеритель времени установления выходного напряжения цифроаналоговых преобразователей | 1984 |

|

SU1236612A1 |

е

yV

tpus г

fi

Авторы

Даты

1979-07-30—Публикация

1974-06-14—Подача