(54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПЕРЕХОДОВ И ЭКСТРЕМУМОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения экстремумов функций | 1980 |

|

SU903896A1 |

| Устройство для определения локальных экстремумов | 1989 |

|

SU1674107A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для определения локальных экстремумов | 1984 |

|

SU1254468A1 |

| Устройство для поиска экстремальных чисел | 1980 |

|

SU883895A1 |

| Параллельный статистический анализатор отклонений и колебаний напряжения | 1982 |

|

SU1076913A1 |

| Устройство линейного кодирования | 1990 |

|

SU1783544A1 |

| Анализатор функций распределения экстремумов | 1982 |

|

SU1091176A1 |

| Устройство для интегрированияпиКООбРАзНыХ фуНКций | 1978 |

|

SU813453A1 |

| Устройство для определения экстремума | 1988 |

|

SU1603341A1 |

Изобретение относится к области измерительной техники.

Известны устройства для определения экстремумов, используемые в радиотехнических устройствах и приборах для статистического учета и анализа, содержащие регистры, элементы И, ИЛИ 1.

Недостатком .известных устройств является низкая надежность.

Наиболее близким по технической сущности кданному, является устройство для определения переходов и экстремумов, содержащее первый п-разрядный запоминающий регистр, первую группу из п элементов И и первый элемент ИЛИ, причем единичные выходы первого п-разрядного запоминающего регистра соединены с первыми входами соответствующих элементов И первой группы, вторые входы которых подключены к первому входу устройства 2..

В случае изменения входной величины так. что ее значения попадают не в соседний разряд (поддиапазон), а через один или несколько разрядов, функционирование указанного выще устройства нарущается (происходят сбои). Данное устройство не позволяет определять переходы значений входной величины между разрядами ее значений. Целью настоящего изобретения является повыщенйе надежности устройства.

Поставленная цель достигается тем, что

в устройство введены п-разрядный запоминающий регистр, вторая группа из п(п- 1)

элементов И, второй элемент ИЛИ и триггер,

причем выходы элементов И первой группы

соединены с единичными входами Соответствующих разрядов второго п-разрядного запоминающего регистра, нулевые входы которых подключены ко второму входу устройЛва, единичные выходы второго ,п-разрядных запоминающих регистров соединены с первыми входами элементов И второй

группы, вторые входы которых подключены к единичным выходам соответствующих разрядов первого п-разрядного заПЬминающего регистра, выходы элементоЬ И второй группы соединены с соответствующими входами

первого и второго элементов ИЛИ, выход второго элемента ИЛИ подключен к единнчHoiky входу триггера, выход первого элемента ИЛИ соединен с нулевым входом триггера.

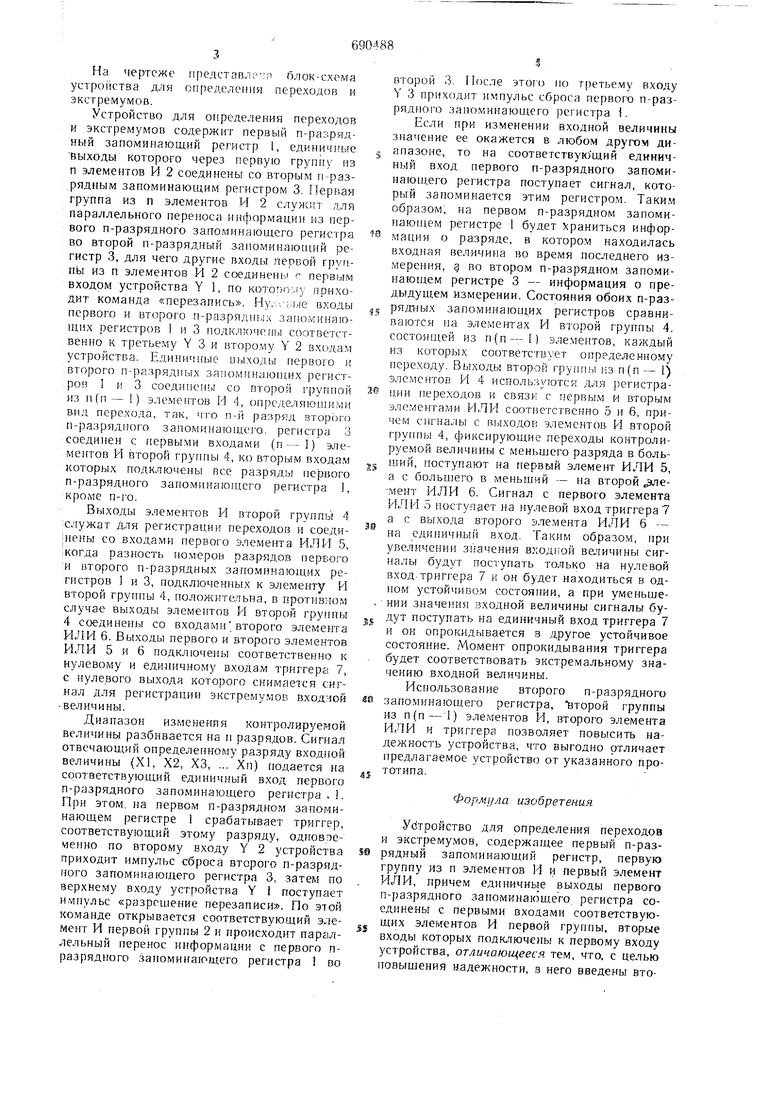

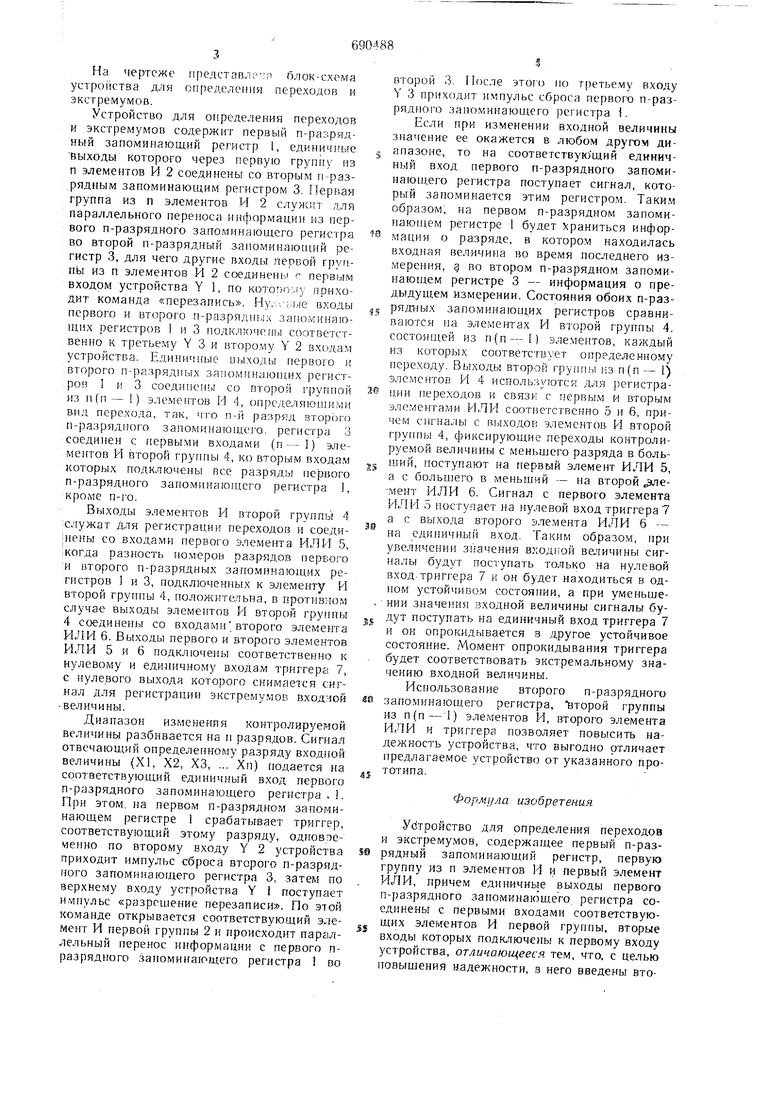

На чертеже представлена блок-схема устройства для определения переходов и экстремумов.

Устройство для определения переходов и экстремумов содержит первый п-разрядный запоминающий регистр 1, единичные ВЫХОДЫ которого через первую группу из п элементов И 2 соединены со вторым п-разрядным запоминающим регистром 3. Первая группа из п элементов И 2 служит для параллельного переноса информации из первого п-разрядного запоминающего регистра во второй п-разрядный запоминающий регистр 3, для чего другие входы первой группы из п элементов И 2 соединены с первым входом устройства Y 1, по которому приходит команда «перезапись. Нулевые входы первого и второго п-разрядных запоминающих регистров I и 3 подключены соответственно к третьему Y 3 и второму У 2 входам устройства. Единичные выходы первого и второго п-разрядпых запоминающих регистров 1 и 3 соединены со второй группой из п(п - 1) элементов И 4, определяющими вид перехода, так, что п-й разряд второго п-разрядного запоминающего, регистра 3 соединен с первьши входами (п-1) элементов И второй группы 4, ко вторым входам которых подключены все разряды первого п-разрядного запоминающего регистра 1, кроме п-го.

Выходы элементов И второй группь 4 служат Для регистрации переходов и соединены со входами первого элемента ИЛИ 5, когда разность номеров разрядов первого и второго п-разрядных запоминаюш,их регистров 1 и 3, подключенных к элементу И второй группы 4, положительна, в противном случае выходы элементов И второй группы 4 соединены со вход а мивторого элемента ИЛИ 6. Выходы первого и второго элементов ИЛИ 5 и 6 подключены соответственно к НулёвЬму и единичному входам триггера 7, с нулевого выхода которого, снимается сигнал для регистрации экстремумов входной -величины..

Диапазон изменения контролируемой величины разбивается на п разрядов. Сигнал отвечающий определенному разряду входной величины {XI, Х2, ХЗ, ... Хп) подается на соответствующий единичный вход первого п-разрядного запоминающего регистра,. При этом, на первом п-разрядном запоминающем регистре 1 срабатывает триггер, соответствующий этому разряду, одновременно по второму входу Y 2 устройства приходит импульс сброса второго п-разрядного запоминающего регистра 3, затем по верхнему входу устройства Y 1 поступает и.мпульс «разрешение перезаписи. По этой команде открывается соответствующий элемент И первой группы 2 и происходит параллельный перенос информации с первого празрядного запоминающего регистра I во

второй 3. После этого по третьему входу Y 3 приходит импульс сброса первого п-разрядного запоминающего регистра .

Если при изменении входной величины значение ее окажется в любом другом диапазоне, то на соответствующий единичный вход первого п-разрядного запоминающего регистра поступает сигнал, который запоминается этим регистром. Таким образом; на первом п-разрядном запоминающем регистре 1 будет Храниться информация о разряде, в котором находилась входная величина во время последнего измерения, 9 во втором п-разрядном запоминающем регистре 3 - информация о предыдущем измерении. Состояния обоих п-разрядных запоминающих регистров сравниваются на элементах И второй .группы 4. состоящей из п(п -1) элементов, каждый из которьтх соответствует определенному переходу. Выходы второй группы из п (п - 1) элементов И 4 используются для регистрации переходов и связи с первым и вторым элементами ИЛИ соответственно 5 и 6, причем сигналы с выходов элементов И второй группы 4, фиксирующие переходы контролируемой величины с меньщего разряда в больший, поступают на первый элемент ИЛИ 5, а с больщего в меньщий - на второй е-мент ИЛИ 6. Сигнал с первого элемента ИЛИ 5 поступает на нулевой вход триггера а с выхода второго элемента ИЛИ 6 -

на единичный вход. Таким образом, при увеличении значения входной величины сигналы будут поступать только на нулевой вход триггера 7 и он будет находиться в одном устойчивом состоянии, а при уменьшеНИИ значения входной величины сигналы будут поступать на единичный вход триггера 7 и он опрокидывается в другое устойчивое состояние. Момент опрокидывания триггера будет соответствовать экстремальному значению входной величины.

Использование второго п-разрядного

запоминающего регистра, второй группы из п(п - 1) элементов И, второго элемента ИЛИ и триггера позволяет повысить надежность устройства, что выгодно отличает предлагаемое устройство от указанного прототипа.

Формула изобретения

Уйтройство для определения переходов И экстремумов, содержащее первый п-разрядный запоминающий регистр, первую группу из п элементов И и первый элемент ИЛИ, причем единичное выходы первого п-разрядного запоминающего, регистра соединены с первыми входами соответствующих элементов И первой группы, вторые входы которых подключены к первому входу устройства, отличающееся тем, что, с целью повышения надежности, в него введены второй п-разрядный запоминающий регистр, вторая группа из п(п -I) элементов И, второй элемент ИЛИ и триггер, причем выходы элементов И первой группы соединены с единичными входами соответствующих разрядов второго п-разрядного запоминающего регистра, нулевые входы которых подключены ко BTOpoiviy входу устройства, единичные выходы второго п-разрядного запоминающего регистра соединены с первыми входами элементов И второй группы, вторые входы которых подключены к единичным выходам соответствующих разрядов первого

п-разрядного запоминающего регистра, вы ходы элементов И второй группы соединены с соответствующими входами первого и второго элементов ИЛИ, выход второго элемента ИЛИ подключен к единичному входу триггера , выход первого элемента ИЛИ соединен с нулевым входом триггера. Источники информации,

принятые во внимание при экспертизе I. Авторское свидетельство СССР № 416698, кл. G 06 F 15/36, 1973.

Авторы

Даты

1979-10-05—Публикация

1976-10-19—Подача