(54) МНОГОКАНАЛЬНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Адаптивный статистический анализатор | 1987 |

|

SU1434453A1 |

| Цифровой одноканальный инфранизкочастотный фазометр | 1987 |

|

SU1472831A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| Коррелометр | 1980 |

|

SU1062717A1 |

| Устройство для определения вероятностных характеристик фазы случайного сигнала | 1982 |

|

SU1112377A1 |

| Устройство для автоматизированного контроля параметров | 1988 |

|

SU1647520A1 |

| Анализатор плотности распределения амплитуд | 1980 |

|

SU903908A1 |

| Устройство для ввода информации | 1989 |

|

SU1667044A1 |

| Устройство отождествления | 1991 |

|

SU1803910A1 |

Изобретение относится к вычис.пи- тельной и измерительной технике и может быть использовано для анализа случайных процессов.

Известен статистический анализатор, содержащий два аналого-цифров ых преобразователя, синхронизатор, регистр сдвига, два дешифратора, пересчетную схему, умножитель, четыре коммутатора и две группы накопителейг .в котором вычисляются оценки корреляционных функций, одномерных и двумерных законов распределения

Однако большое количество оборудования и последовательное вычисление корреляционных функций случайных сигналов снижает быстродействие устройства..

Известен статистический анашизатор, содержащий два аналого-цифровых преобразователя, синхронизатор, запоминающие ячейки, регистр сдвига, дешифраторы соответствия, двоичные , счетчики, дешифрирующие матрицы, сумматоры, ограничители, схемы совпгаденйя, элементв И и три группы накопителей, имеющий большее быстродействие при вычислении корреляционных функций .

Недостатком анализатора является большое количество оборудования.

Наиболее близким техническим решением к данному изобретению является многоканальный статистический анализатор, содержащий первый и второй аналого-цифровые преобразователи, информационные входы которых являются входами устройства, генератор

10 псевдослучайных чисел, первый и второй цифровой дискриминаторы, первые входы которых подключены к выходам соответственно первого и второго аналого-цифровых преобразователей, а

15 вторые входы - к выходу генератора псевдослучайных чисел, счетчик, третий цифровой дискриминатор, входы которого подключены к выходам второго аналого-цифрового преобразователя

20 и счетчика, коммутатор, матричный дешифратор, входы которого соединены с выходом первого аналого-цифрового преобразователями с выходом коммутатора, первый регистр сдвига,по25 следовательвый вход которого соеди- , I нен с выходом первого цифрового дискриминатора, а параллельные входы разрядов подключены к Выходам матричного дешифратора, запоминающую ячейку,

30 вход которой соединен с выходом второго цифрового дискриминатора, де: шифраторы соответствия, первые входы которых объединены и подключены к выходу запоминающей ячейки, а вторые входы соединены с выходом соответствующего разряда первого регистра сдвига, накопители, входы которых со динены с выходом соответствующего дешифратора соответствия , второй регистр сдвига, вход которого подключен к выходу третьего цифрового диск риминатора, а выход - к входу коммутатора , синхронизатор, выходы которо ,го подключены к управляющим входам (налого-цифровых преобразователей, регистров сдвига, запоминающей ячейки, коммутатора и. счетчика 3. Недостатком данного анализатора является большое количество оборудования, обусловленное наличием И накопителей (п - число ординат корреляционной функции). Цель изобретения - упрощение устройства . Для достижения этой цели в многоканальный статистический анализатор, содержащий первый и второй аналого цифровые преобразователи, информационные входы которых являются соответ ственно первым и вторым входами анализатора, а управляющие.входы первого и второго аналого-цифровых преобразователей объединены и подключены к первому выходу блока управления, второй выход которого соединен со счетным входом счетчика, а третий выход блока управления подключен к управляющему входу первого коммутато ра, информационный вход которого соединен с выходом регистра сдвига, управляющий вход которого подключен к четвертому вы-ходу блока управления а информационнЕлй вход - к выходу пер вого дискриминатора, первый вход которого соединен с выходом первого аналого-цифрового преобразователя,ге нератор псевдослучайных чисел, выход .которого подключен к первому входу второго дискриминатора, второй вход которого объединен со входом матричного дешифратора и подключен к выход BTOjioro ансшого-цифрового преобразователя, введен второй комму -атор, делитель частоты, ключ начала записи и К вычислительных блоков, Каждый и: которых состоит из входного комMjfvraTopa, регистра задержки, счетчик умножителя и запоминающего устройства, причем выход второго коммутатора анализатора соединен со вторым , входом первого дискриминатора, а пер вый и второй входы - с выходами соот ветственно генератора псевдослучайных чисел и счетчика, выход второго дис риминатора соединен с первым информа .ционным входом входного коммутатора первого вычислительного блока, второ информационный вход входного коммута тора i-го (i 1, 2,..., к) вычислительного блока соединен с выходом старшего разряда регистра задержки, с первым входом умножителя своего вычислительного блока и с первым информационным входом входного коммутатора (i + 1)-го вьгчислительного блока, выход входного коммутатора каждого i-ro вычислительного блока подключен к входу первого разряда регистра задержки своего блока, разрядные входы регистра задержки i-ro вычислительного блока подключены к i-и группе выходов матричного дешифратора, выход первого коммутатора анализатора соединен с вторым вь1ходом умножителя каждого вычислительного блока, выход умножителя 1-го вычислительного блока соединен со счетным входом счетчика своего блока, разрядные входы и выходы этого счетчика соединены соответственно с выходами и входами запоминающего устройства своего блока, управляющие входы входных коммутаторов всех к вычислительных блоков объединены с управляющими входами ключа начала записи и делителя частоты и подключены к четвертому выходу блока управления, выход делителя частоты соединен со входом блока управления, пятый выход которого соединен с управляющими входами регистров задержки всех X. вычислительных блоков, а шестой выход - с управляющими входа ли запоминающих устройств всех k вычислительных блоков, выход ключа начала записи подключен к информационному входу делитеЯя частоты и к входам сброса счетчиков всех « вычислительных блоков. Блок управления состоит из элемент тов И,триггера циклов, прямой выход которого соединен с первыми входами первого, второго, третьего и четвертого элементов И, вторые входы первого, второго и первый вход пятого элементов.И объединены и подключены к первому выходу формирователя импульсов, вход которого соединен с выходом генератора импульсов, а второй выход подключен к счетному входу счетчика адреса, входу делителя частоты и ко вторым входам третьего и четвертого элементов И, выходы первого, второго и третьего элементов И являются соответственно пятым, четвертым и первым выходами блока , инверсный выход триггера циклов соединен со входом сброса счетчика адреса, разрядные выходы которого подключены к первым входам соответствующих элементов ИСКЛЮЧАЮЩИЕ ИЛИ и входам элемента ИЛИ-НЕ, при этом выход старшего разряда счетчика адреса соединен с нулевым входом триггера циклов, с единичным входом триггера сброса памяти и счетным входом счетчика вывода, вход сброса которого

объединен с третьим входом четвертого элемента И, вторыми входами элементов ИСКЛЮЧАЮЩИЕ ИЛИ и соединен с инверсным выходом триггера вывода, единичный вход которого является входом блока, а нулевой вход объединен с нулевым входом триггера сброса памяти, счетным входом счетчика за--. держки, подключен к выходу старшего разряда счетчика вывода и является вторым выходом блока, второй вход пятого элемента И соединен с пряойым выходом триггера сброса памяти, выход счетчика задержки является третьим выходом блока, а выходы элементов ИСКЛЮЧАЮЩИЕ ИЛИ, четвертого и Пятого элементов И является шестым выходом блока, при этом выход элемента ИЛИ-НЕ соединен с третьими выходами второго и третьего элементов И, а единичный вход триггера циклов соединен с выходом делителя частоты.

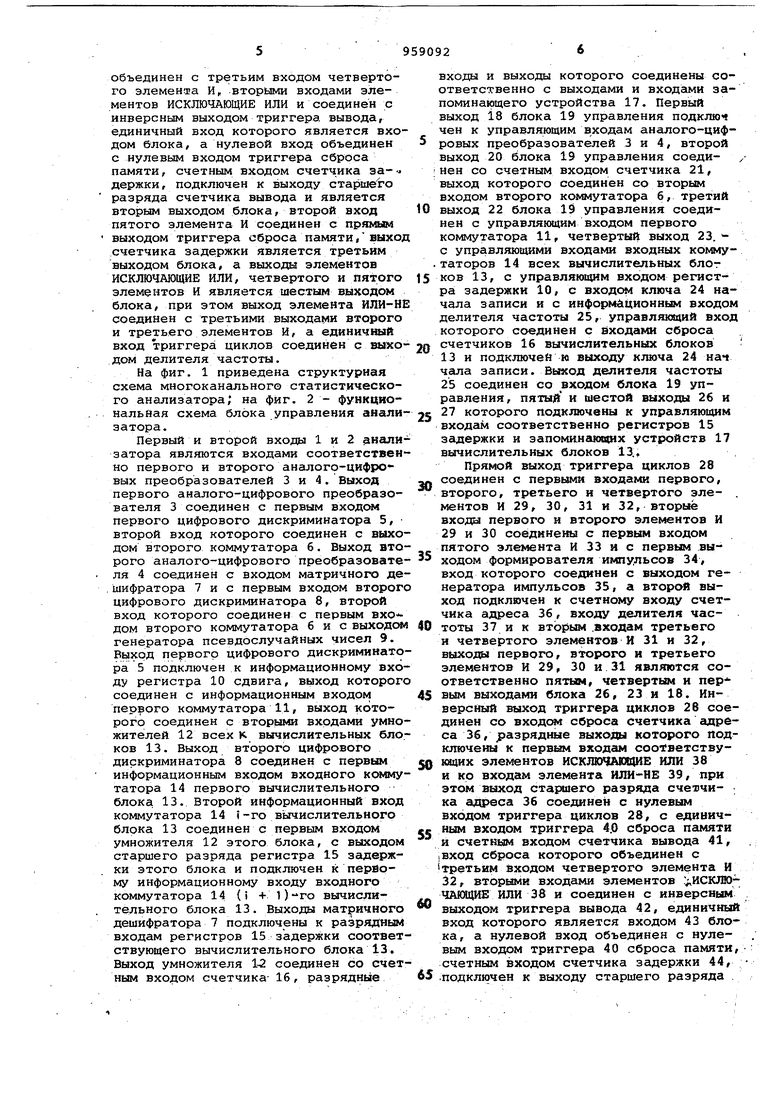

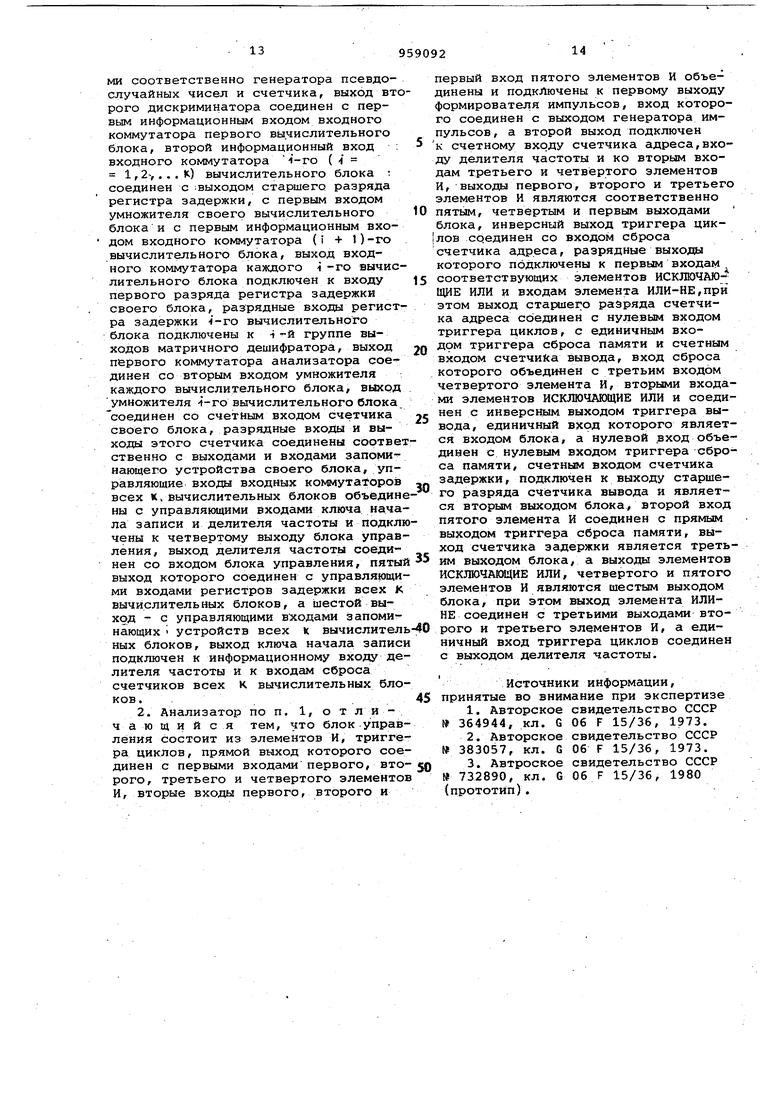

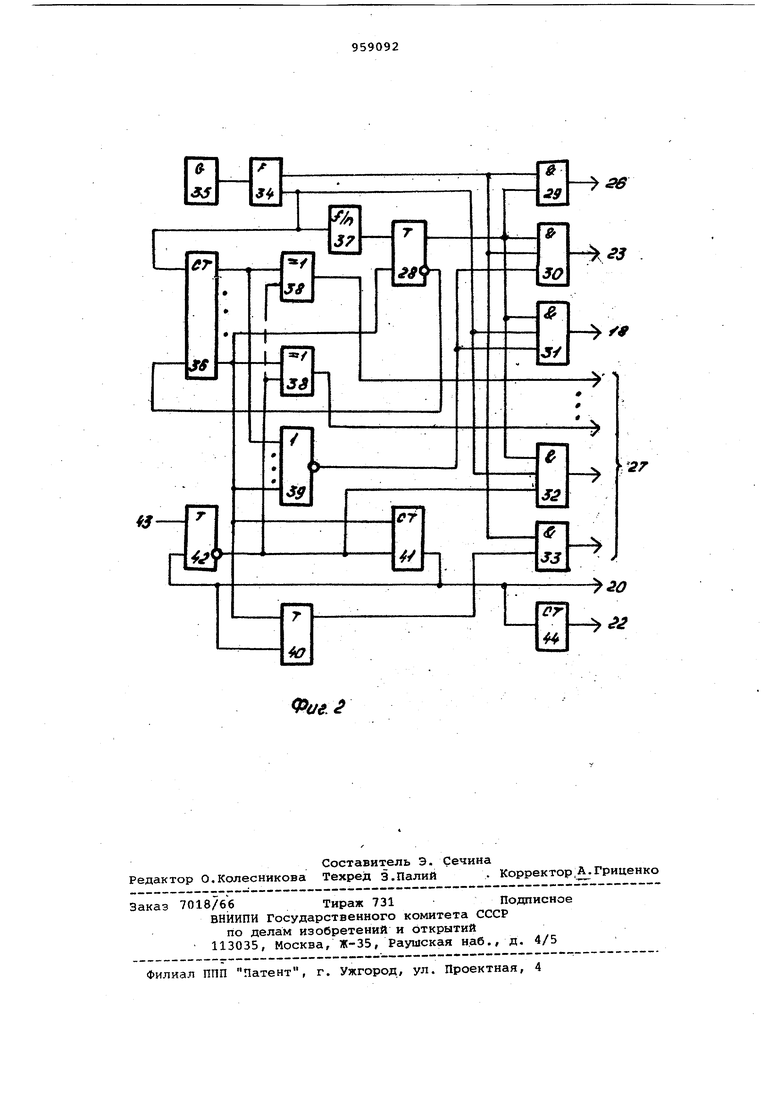

На фиг. 1 приведена структурная схема многоканального статистического анализатора; на фиг. 2 - функциональная схема блока управления анализатора.

Первый и второй входы 1 и 2 анализатора являются входами соответственно первого и второго аналого-цифровых преобразователей 3 и 4. Выход первого аналого-цифрового преобразователя 3 соединен с первым входом первого цифрового дискриминатора 5, второй вход которого соединен с выходом второго коммутатора 6. Выход второго аналого-цифрового преобразователя 4 соединен с входом матрично1хэ де.шифратора 7 и с первым входом второго цифрового дискриминатора 8, второй вход которого соединен с первым входом второго коммутатора бис выходом генератора псевдослучайных чисел 9. Выход первого цифрового дискриминатора 5 подключен к информационному входу регистра 10 сдвига, выход которого соединен с информационным входом первого коммутатора 11, выход которого соединен с вторыми входами умножителей 12 всех К вычислительных блоков 13. Выход второго цифрового дискриминатора 8 соединен с первым информационным входом входного коммутатора 14 первого вычислительного блока. 13. Второй информационный вход коммутатора 14 I-го вычислительного блока 13 соединен с первым входом умножителя 12 этого блока, с выходом старшего разряда регистра 15 задержки этого блока и подключен к первому информационному входу входного коммутатора 14 (i + 1)го вычислительного блока 13. Выходы матричного дешифратора 7 подключены к разрядным входам регистров 15 задержки соответствующего вычислительного блока 13. Выход умножителя 1-2 соединен со счетным входом счетчика- 16, разрядные

входы и выходы которого соединены соответственно с выходами и входами запоминающего устройства 17, Первый выход 18 блока 19 управления подключ чен к управляющим входам аналого-цифровых преобразователей 3 и 4, второй выход 20 блока 19 управления соеди- / ;нен со счетным входом счетчика 21, выход которого соединен со вторым входом второго коммутатора б, третий

0 выход 22 блока 19 управления соединен с управляющим входом первого коммутатора 11, четвертый выход 23.с управляющими входами входных комму.таторов 14 всех вычислительных блог

5 ков 13, с управляющим входом регистра задержки 10, с входом ключа 24 начала записи и с информё1ционным входом делителя частоты 25, управляющий вход которого соединен с Входами сброса

0 счетчиков 16 вычислительных блоков 13 и подключен ю выходу ключа 24 нач чала записи. Выход делителя частоты 25 соединен со входом блока 19 управления, пятый и шестой выходы 26 и

е 27 которого подключены к управляющим входам соответственно регистров 15 задержки и запомкнакяцих устройств 17 вычислительных блоков 13.,

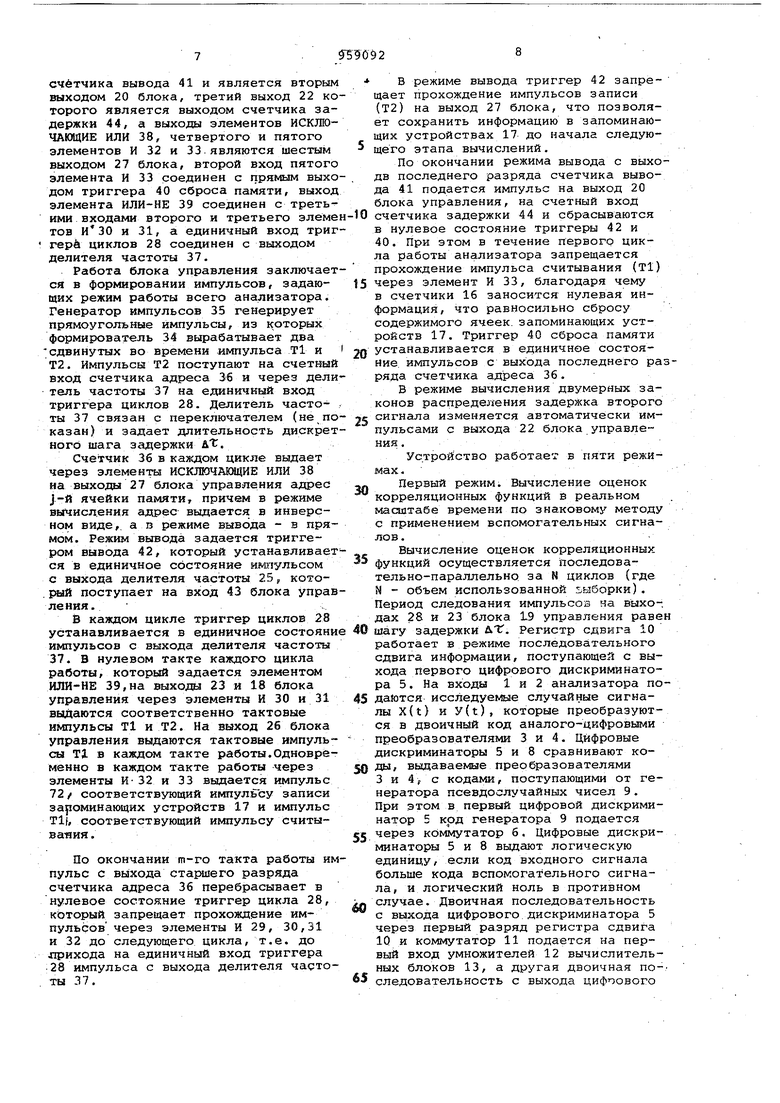

Прямой выход триггера циклов 28

соединен с первыми входами первого.

второго, третьего и четвертого эле- . ментов И 29, 30, 31 и 32, вторые входы первого и второго элементов И 29 и 30 соединены с первым входом пятого элемента и 33 и с первым выходом формирователя илшульсов 34, вход которого соединен с выходом генератора импульсов 35, а второй выход подключен к счетному входу счетчика адреса 36, входу делителя частоты 37 и к вторым .входам третьего и четверто1Ч элементов И 31 и 32, выходы первого, второго и третьего элементов И 29, 30 и 31 являются соответственно пятым, четверть и первым выходами блока 26, 23 и 18. ИнверсНый выход триггера циклов 28 соединен со ВХОДСЯУ1 сброса счетчика адреса 36, разрядные выходы которого подключены к первьо4 входам соофветствующих элементов ИСКЛЮЧЕАЮЩИЕ ИЛИ 38 и ко входам элемента ИЛИ-НЕ 39, при этом выход старшего разряда счетчи- ; ка адреса 36 соединен с нулевым входом триггера циклов 28, с единичным входом триггера 4.0 сброса памяти и счетным входом счетчика вывода 41, 1ВХОД сброса которого объединен с iтретьим Входом четвертого элемента И 32, вторыми входами элементов :;,ИСКЛЮЧАЩИЕ ИЛИ 38 и соединен с инверсным

выходом триггера вывода 42, единичный вход которого является входом 43 блока, а нулевой вход объединен с нулевым входом триггера 40 сброса памяти, счетным входом счетчика задержки 44,

.подключен к выходу старшего разряда счётчика вывода 41 и является вторы выходом 20 блока, третий выход 22 к торого является выходом счетчика за держки 44, а выходы элементов ИСКЛЮ ЧАЮЩИЕ ИЛИ 38, четвертого и пятого элементов И 32 и 33.являются шестым выходом 27 блока, второй вход пятог элемента И 33 соединен с прямым вых дом триггера 40 сброса памяти, выхо элемента ИЛИ-НЕ 39 соединен с треть ими входами второго и третьего элем тов и30 и 31, а единичный вход три герй циклов 28 соединен с выходом делителя частоты 37. Работа блока управления заключае ся в формировании импульсов, задающих режим работы всего анализатора. Генератор импульсов 35 генерирует прямоугольные импульсы, из I OTOPHX формирователь 34 вырабатывает два сдвинутых во времени импульса Т1 и Т2. Импульсы Т2 поступают на счетны вход счетчика адреса 36 и через дел тель частоты 37 на единичный вход триггера циклов 28. Делитель частоты 37 связан с переключателем (не по казан) и задает длительность дискре ного шага задержки At. Счетчик 36 в каждом цикле выдает через элементы ИСКЛЮЧАЩИЕ ИЛИ 38 на выходы 27 блока управления адрес j-й ячейки памяти, причем в режиме вычисл.ения адрес выдается в инверсном виде,, а в режиме вывода - в пря мом. Режим вывода задается триггером вывода 42, который устанавливает ся в единичное состояние импульсом с выхода делителя частоты 25, кото.рый поступает на вхол 43 блока управ ления. В каждом цикле триггер циклов 28 устанавливается в единичное состояни импульсов с выхода делителя частоты 37. В нулевом такте каждого цикла работы, который задается элементом ИЛИ-НЕ 39,на выходы 23 и 18 блока управления через элементы И 30 и 31 выдаются соответственно тактовые импульсы Т1 и Т2. На выход 26 блока управления выдаются тактовые импульсы Т1 в каждом такте работы.Одновременно в каждом такте работы через элементы И-32 и 33 выдается импульс 72/ соответствующий импульсу записи запоминающих устройств 17 и импульс Tlf, соответствующий импульсу считывания . По окончании т-го такта работы им пульс с выхода старшего разряда счетчика адреса 36 перебрасывает в нулевое состояние триггер цикла 28, который запрещает прохождение импульсов через элементы И 29, 30,31 и 32 до следующего цикла, т.е. до лрихода на единичный вход триггера 28 импульса с выхода делителя частоты 37. в режиме вывода триггер 42 запрещает прохождение импульсов записи {Т2) на выход 27 блока, что позволяет сохранить информацию в запоминающих устройствах 17 до начала следующего этапа вычислений. По окончании режима вывода с выходв последнего разряда счетчика вывода 41 подается импульс на выход 20 блока управления, на счетный вход счетчика задержки 44 и сбрасываются в нулевое состояние триггеры 42 и 40. При этом в течение первого цикла работы анализатора запрещается прохождение импульса считывания (т) через элемент И 33, благодаря чему в счетчики 16 заносится нулевая информация, что равносильно сбросу содержимого ячеек, запоминающих устройств 17. Триггер 40 сброса памяти устанавливается в единичное состояние импульсов с выхода последнего разряда счетчика адреса 36. В режиме вычисления двумерных законов распределения задержка второго сигнала изменяется автоматически импульсами с выхода 22 блока управления . Устройство работает в пяти режимах . Первый режим. Вычисление оценок корреляционных функций в реальном масштабе времени по знаковому методу с применением вспомогательных сигналов.. Вычисление оценок корреляционных функций осуществляется последовательно-параллельно за N циклов (где N - объем использованной эыборки). Период следования импульсов на выходах 28 и 23 блока 19 управления равен шагу задержки &f. Регистр сдвига 10 работает в режиме последовательного сдвига информации, поступающей с выхода первого цифрового дискриминатора 5 . На входы 1 и 2 анализатора подаются исследуелме случайные сигналы X(t} и y(t), которые преобразуются в ДВОИЧНЫЙ код аналого-цифровыми преобразователями 3 и 4. Цифровые дискриминаторы 5 и 8 сравнивают коды, выдаваемые преобразователями 3 и 4, с кодами, поступающими от генератора псевдослучайных чисел 9. При этом в первый цифровой дискриминатор 5 код генератора 9 подается через коммутатор 6. Цифровые дискриминаторы 5 и 8 выдают логическую единицу, если код входного сигнала больше кода вспомогательного сигнала, и логический ноль в противном случае. Двоичная последовательность с выхода цифрового дискриминатора 5 через первый разряд регистра сдвига 10 и коммутатор 11 подается на первый вход умножителей 12 вычислительных блоков 13, а другая двоичная по-/ следовательность с выхода цифпового дискриминатора 8 подается на первый информационный вход входного коммутатора 14 первого вычислительного . блока .13, , Каждый цикл вычисления состоит из m тактов (т - число разрядов регистр 15 задержки). В первом такте на управляющий вход входного коммутатора 14подается сигнал записи с выхода 23 блока 19 управления, который также подается на управляющий вход регистра 10 сдвига. Одновременно в регистры 15 задержки подается первый тактовый импульс с выхода 26 блока 19 управления. Через входной коммутатор 14 в первый разряд регистра 15 задержки первого вычислительного бло ка 13 заносится информация с выхода второго цифрового дискриминатора 8. В первый разряд регистра 15 задержки (i + 1)-го вычислительного блока 13 в-первом такте каждого цикла заносит ся информация с выхода старшего т-го разряда регистра 15 задержки 1-го вычислительно блока 13 через входной коммутатор 14. На управляющие входаа запоминающего устройства 17 с выхода 27 блока 19 управления в каждом такте работы подается код адреса т-й ячей- ки памяти, информация из которой заносится в счетчик 16. Умножитель 12 перемножает значение задержанной последовательности импульсов с выхода старяиего т-го разряда регистра 15задержки со значением другой последовательности импульсов, поступаю щей в умножитель 12 с выхода первого разряда регистра 10 сдвига через ком мутатор 11. Если значения обеих последовательностей совпадают то на счетный вход универсального счетчика 16подается единица, которая добавля ется к содержимому счетчика. Получен ное значение частичного результата i ординаты корреляционной функции заносится в т-ю ячейку запоминаняцего устройства 17. В J-OM (j О, 1, 2,...,т-1) такте работы в первый разряд регистр 15 задержки через коммутатор 14 заносится значение информации с 1знхода т-го старшего разряда этого регистра а в счетчик 16 - значение частичного результата (im-j)-oй ординаты корреляционной функции из (m-j)-й ячейки памяти запоминающего устройства 17. В запоминающих устройствах 17 в виде п точек, равноотстаящих вдоль аргумента с шагом Л/С , накапливаются значения оценки корреляционной функции Rxy(-cr). . В начале вычисления счетчики 16 сбрасываются потенциалом сброса,.который поступает с выхода ключа начала записи 24. Этим же потенциалом сбрасывается и деллтель частоты25. Для исключения ошибки вычисления в течение п циклов счетчики 16 и делитель частоты 25 находятся в нулевом состоянии, пока все разряды регистров 15 всех вычислительных блоков 13 не будут заполнены значениями последовательности импульсов, соответствующей исследуемой реализации X(t). По окончании п-го цикла снимается потенциал сброса и начинаются вычисления оценки корреляционной функции. На вход делителя частоты 25 поступают импульсы записи с выхода 23 блока 19 управления. Делитель частоты имеет коэффициент деления 24 (д - число разрядов уйивер-. сального счетчика 16) и при его переполнении на вход блока 19 управления подается сигнал окончания вычисления и начинается режим вывода оценки корреляционной функции. Второй режим. Вычисление оценок интегрального закона распределения F(X) случайного- процесса X(t). Вычисление оценок F(X) осуществляется параллельно за N циклов. Регистры 15 задержки работают в режиме параллельной записи, а регистр 10 сдвига установлен в единичное состояние, которое не меняется в течение процесса измерения F,(X) . Оценка Г(Х) накапливается в запоминающих устройствах 17 в виде 2 п (р - число разрядов аналого-цифрового преобразователя) точек, равноотстоящих вдоль оси аргумента с шагом UX равного уровню квантования преобразователя 4. Получение F{Xjt )обеспечивается за счет работы дешифратора 7 в«соответствии с соотношением и /. .-,(AX/2; , (o1Vчx.x(t)(/4 При этом на соответствующем выходе дешифратора 7 получается единичный сигнал, поступающий в соответствующий разряд регистра 15 сдвига и через соответствующий умножитель 12 на счетный вход счетчика 16. Таким образом, в ячейках памяти запоминающих устройств 17 после N циклов усреднения получена оценка п точек интегрального закона распределения F{X) . Третий режим. Вычисление оценок дифференциального закона распределеНИН W(X) случайного процесса X{t). Данный режим отличается от предыдущего работой матричного дешифратора 7, который в данном случае работает в соответствии с соотношением и (4 4-1 i ЬХ/лх.ха))(-(дХ/2; ил«X(t)X 4uX/i; в запоминающих устройствах 17 пос.ле N циклов усреднения получена оценка 2 n точек дифференциального распределения W(X). Четвертый режим. Вычисление оце-т нок интегрального двумерного закона распределения F (X; Y;tr) случайных процессов X(t) и y(t). Оценка F(X; Y;Т) получа§тся в ви де оценок 2 п точек сечения по X при ВиСк-. S-V,,, t comst, где i-. О, l, 2,...(2-1) - состгоя; ние счетчика 21; t О, 1, 2,..,,L - номер разряда регистра 10 сдвига. Период следования импульсов на выходе 22 блока 19 управления раT9f- Н utja NiTf©, где & - время вывода всех точек оцен ки из запоминающих устройств 17 и установка их в исходное состояние. Период следования импульсов с выхода 20 блока 19 управления равен Atuo Вычисление оценок F (Х; y;Tr) ос ществляется в ( в + 1) этапов / в каж дом из которых находится оценка F. (X; У;Т ) при всех значениях X и но при одном конкретном значении т ЕДТ, изменяющемся ступенчато с шагсж &т. Переход от одного этапа к другому, т.е. изменение аргумента Т i осуп(ествляется автотлатически, с помощью коммутатора 11, импульсами с выхода 20 блока 19 управления. Регистр 10 сдвига и кол94утатор 11 поз воляют изменять tr в пределах от О д .- с шагсЕМ dX. Каацщй этап состоит из п подэтап в из кото{шх находится оценк F {X; У; С) точек, отстоящих равномерно вдоль оси X через ДХ, при У УЙ copsi, t TM «const, где УИ значение кода входного сигнала У(() при п-ом состоянии счетчика 21, Переход от одного подэтапа к дфугому, т.е. изменение уровня анализа y(t) осуа ствляется импульсами с выхода 22 лока 19 управления. Каждый подзтап состоит иэ N циклов совпадавиоик по длительности с циклами вычисления корреляционных . В каждом цикле в дешифриру Щ5ЙО ..матрицу 7 с преобразователя 4 подается код сигнала X(t); Цифровой дискриминатор 5 работает в таком же режикю, что и дешифратор 7. Уровень срабатывания дискриминатора 5 задается счетчиком 21. Матричный дешифратор 7 и дискриминатор 5 работают В соответствии с соотнсндением, аналогичным второму, режиму. За.N циклов вычисляется оценка. F{X, yjt) интегрального двумерного закона распределения случайных сигналов X (t) и y(t) в виде п точек, равноотстоящих по аргументу X с шагом Л X при У 3 , -fc {п-1)АТ. Все же сечения оценки F (X; У;Т) получаются последовательно за время Т Atao L () L-л. Пятый режим. Вычисление оценок дифференциального двумерного закона распределения W (X; VjC) случайных процессов X{t) и y(t). Данный режим отличается от предыдущего тем, что дешифратор 7 и дискриминатор 5 работают в. соответствии с соотношением, аналогичным третьему режиму. образом, данный анализатор требует меньших аппаратурных затрат, так как измерения нескольких характеристик случайных процессов.проводятся на одном и том же оборудовании и в к раз сокращено число накопителей и дешифраторов соответствия. Анализатор позволяет измерять характеристики случайных процессов в реальном масштабе времени. Формула изобретения 1, Многоканальный статистический анализатор, содержащий первый и второй аналого-цифровые преобразователи, инфорр ционные входа которых яв-: ляются соответственно первым и вторьи входами анализатора, а управляющие входол первого и второго аналогоцифровых преобразователей объединены и подключены к первому выходу блока управления, второй выход которого соединен со счетным входом счетчика, а третий выход блока управления подключен к управляющему входу первого Коммутатора, информационный вход которого соединен с выходом регистра сдвига, управляющий вход которого подключен к четвертому выходу блока управления, а информационный вход к выходу первого дискриминатора, первый вход которого соединен с выходом первого аналого-цифрового преобразователя, генератор псевдослучайных чисел, выход которого подключен к первому входу второго дискриминатор ра,. второй вход которого объединен со входом матричного дешифратора и подключен к выходу второго аналого- f цифрового преобразователя, отличающийся тем, что, с целью упрощения, содержит второй коммутатор, делитель частоты, ключ начала записи и If вычислительных блоков, каждый из которых состоит из входного коммут,атора, регистра задержки,счетчика, умножителя и запоминающего устройства, причем выход второго коммутатора анализатора соединен со вторым входом первого дискриминатора, а первый и второй входы - с выходами соответственно генератора псевдослучайных чисел и счетчика, выход вто рого дискриминатора соединен с первым информационным входом входного коммутатора первого вычислительного блока, второй информационный вход : входного коммутатора 4-го ( 1, 2.. . К) вычислительного блока соединен с -выходом старшего разряда регистра задержки, с первым входом умножителя своего вычислительного блока и с первым информационным входом входного коммутатора (i + 1)-го вычислительного блока, выход входного коммутатора каждого -i -го вычислительного блока подключен к входу первого разряда регистра задержки своего блока, разрядные входы регистра задержки 4-го вычислительного блока подключены к i группе выходов матричного дешифратора, выход первого коммутатора анализатора сое- дивен со вторым входом умножителя каждого вычислительного блока, выход умножителя -f-ro вычислительного блока соединен со счетным входом счетчика своего блока, разрядные входы и выходы этого счетчика соединены соответ ственно с выходами и входами запоминаюадего устройства своего блока, управляющие входы входных коммутаторов всех к зычислительных блоков объедине ны с управляющими входами ключа начала записи и делителя частоты и подклю чены к четвертому выходу блока управления, выход делителя частоты соединен со входом блока управления, пятый выход которого соединен с управляющими входами регистров задержки всех К вычислительных блоков, а шестой выход - с управляющими входами запоминающих устройств всех к вычислитель ных блоков, выход ключа начала записи подключен к информационному входу делителя частоты и к входам сброса счетчиков всех К вычислительных блоков. .. . 2. Анализатор по п. 1, о т л и ч а ю щ и и с я тем, что блок управления состоит из элементов И, триггера циклов, прямой выход которого соединен с первыми входами первого, второго, третьего и четвертого элементов И, вторые входы первого, второго и первый вход пятого элементов И объединены и подключены к первому выходу формирователя импульсов, вход которого соединен с выходом генератора импульсов, а второй выход подключен к счетному входу счетчика адреса,входу делителя частоты и ко вторым входам третьего и четвёртого элементов И, выходы первого, второго и третьего элементов И являются соответственно пятым, четвертым и первым выходами блока, инверсный выход триггера циклов соединен со входом сброса счетчика адреса, разрядные выходы которого подключены к первым входам соответствующих элементов ИСКЛЮЧАЮЩИЕ ИЛИ и входам элемента ИЛИ-НЕ,при этом выход старшего разряда счетчика адреса соединен с нулевым входом триггера циклов, с единичным входрм триггера сброса памяти и счетным входом счетчика вывода, вход сброса которого объеди«ен с третьим входом четвертого элемента И, вторь 4И входами элементов ИСКЛЮЧМХЦИЕ ИЛИ и соединен с инверсным выходом триггера вывода, единичный вход которого является входом блока, а нулевой вход объединен с нулевым входом триггера сброса памяти счетным входом счетчика задержки, подключен к выходу старшего разряда счётчика вывода и является вторым выходом блока, второй вход пятого элемента И соединен с прямым выходом триггера сброса памяти, выход счетчика задержки является третьим выходом блока, а выходы элементов ИСКЛЮЧАОДИЕ ИЛИ, четвертого и пятого элементов И являются шестым выходом блока, при этом выход элемента ИЛИНЕ соединен с третьими выходами второго и третьего элементов И, а единичный вход триггера циклов соединен с выходом делителя частоты. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 364944, кл. G 06 F 15/36, 1973. 2.Авторское свидетельство СССР № 383057, кл. G 06 F 15/36, 1973. 3.Автроское свидетельство СССР №732890, кл. G 06 F 15/36, 1980 (прототип).

г. /

ue

Авторы

Даты

1982-09-15—Публикация

1980-09-19—Подача