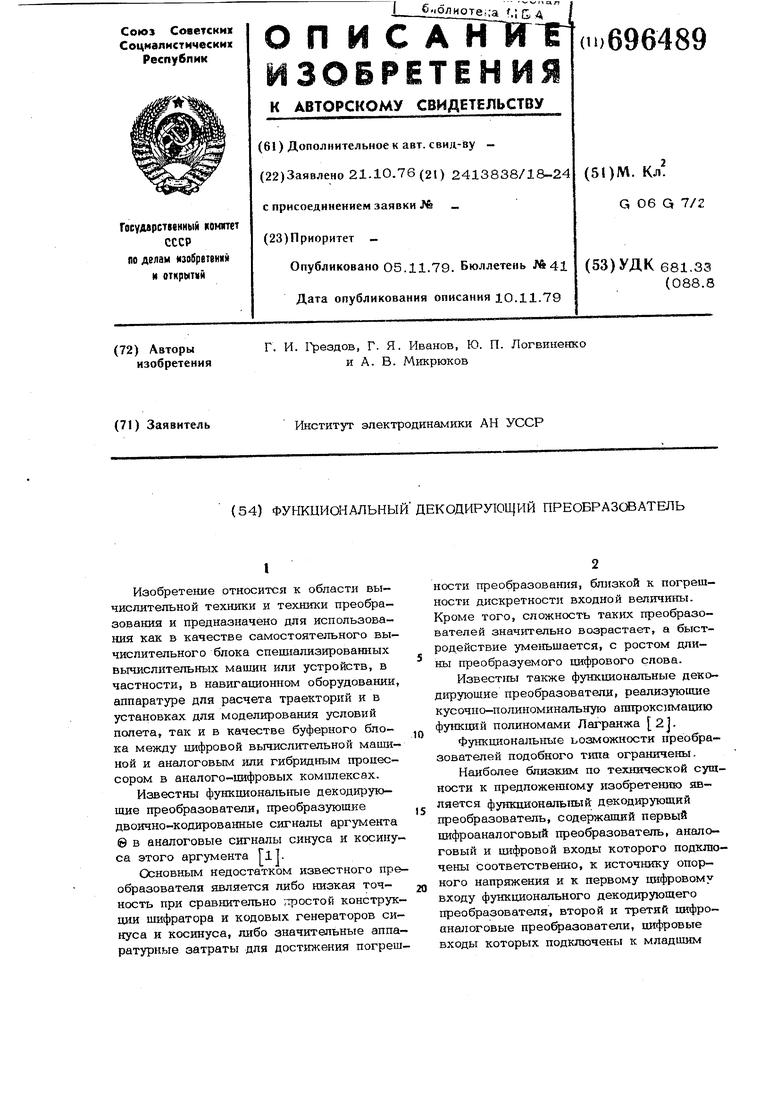

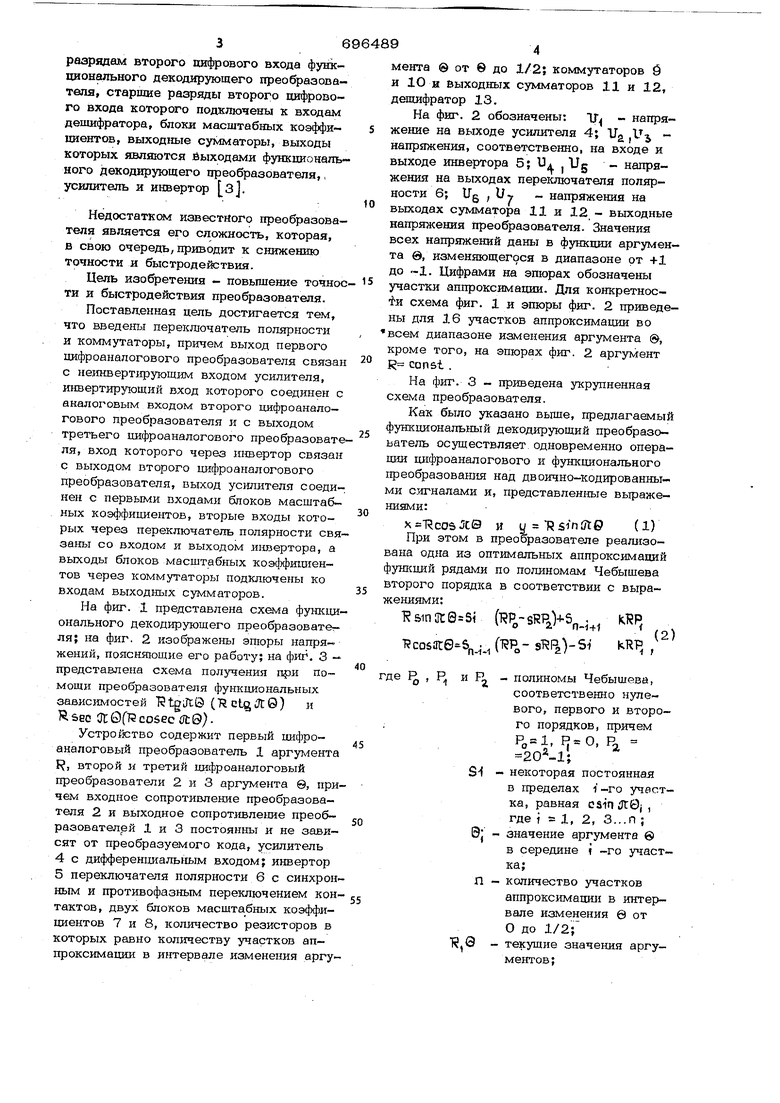

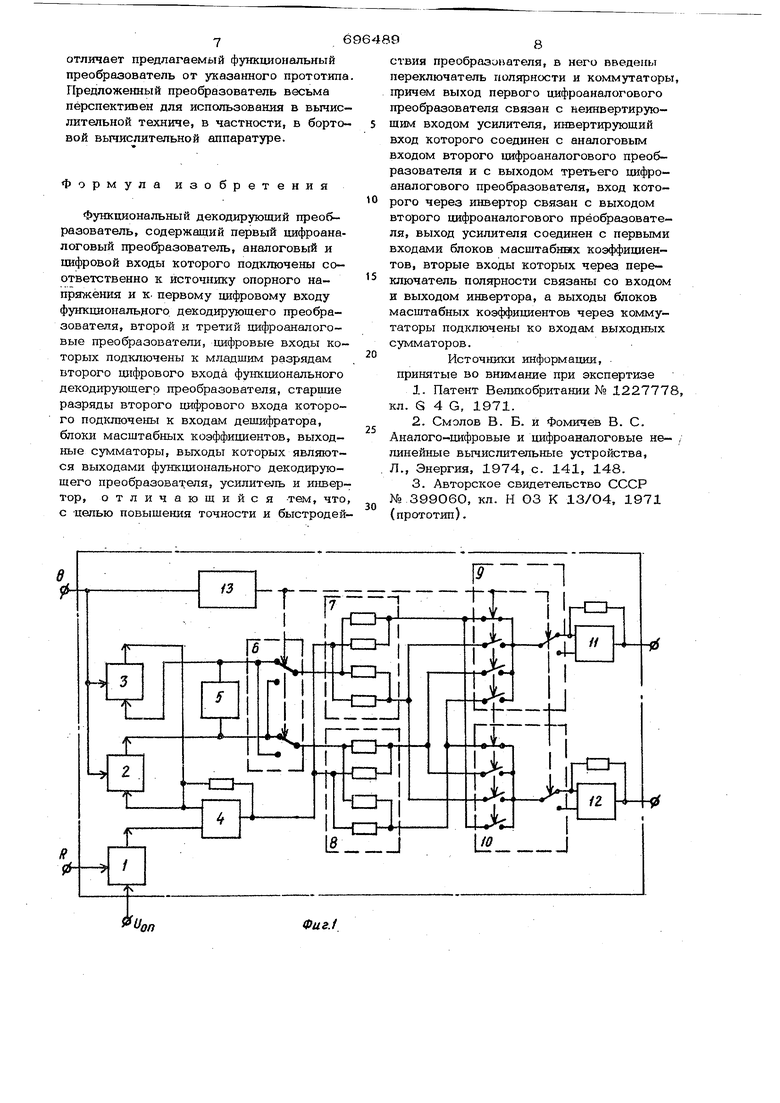

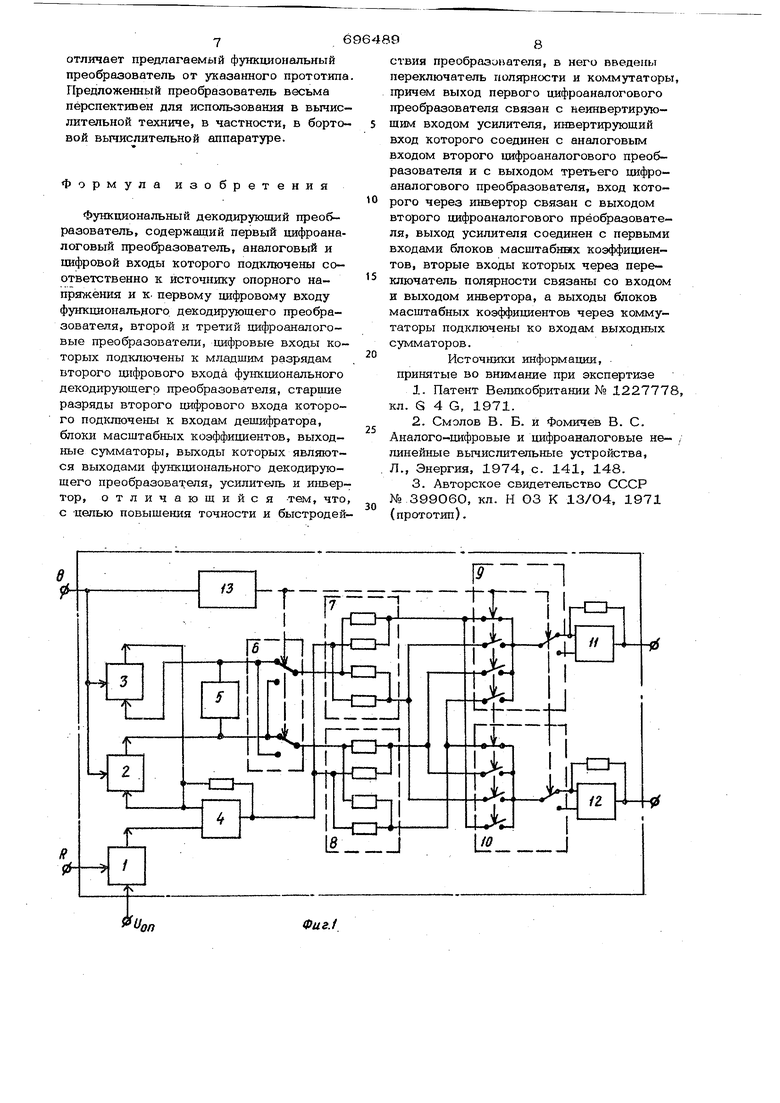

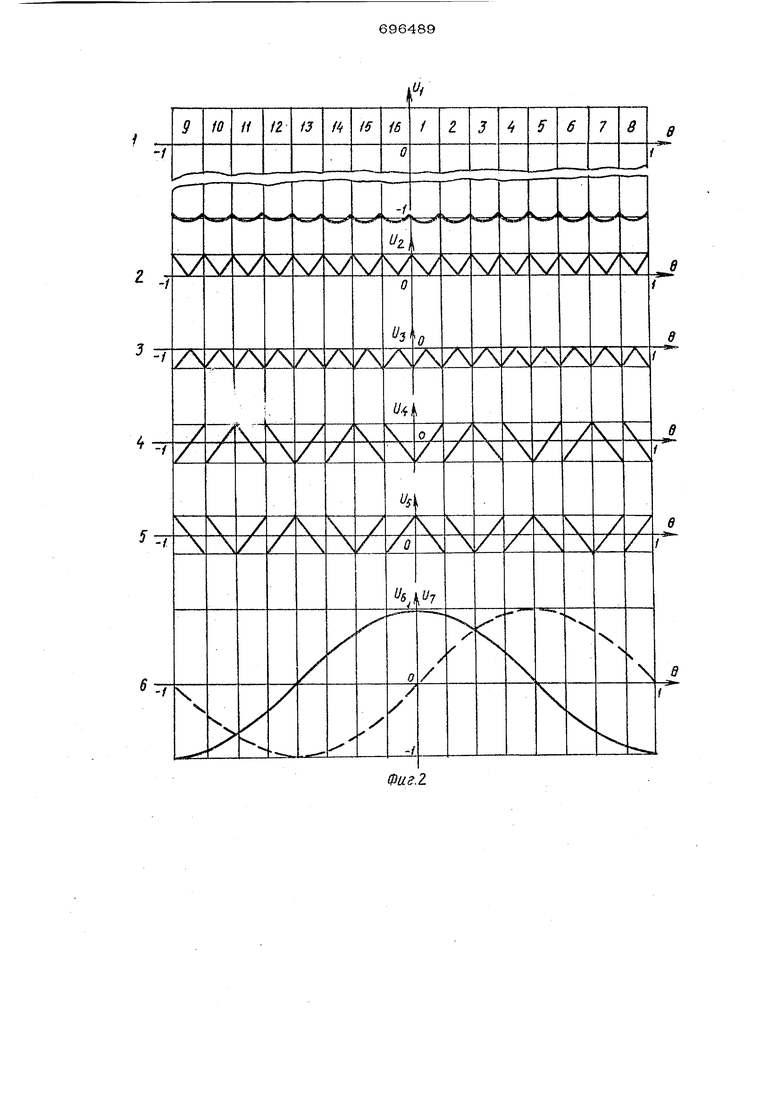

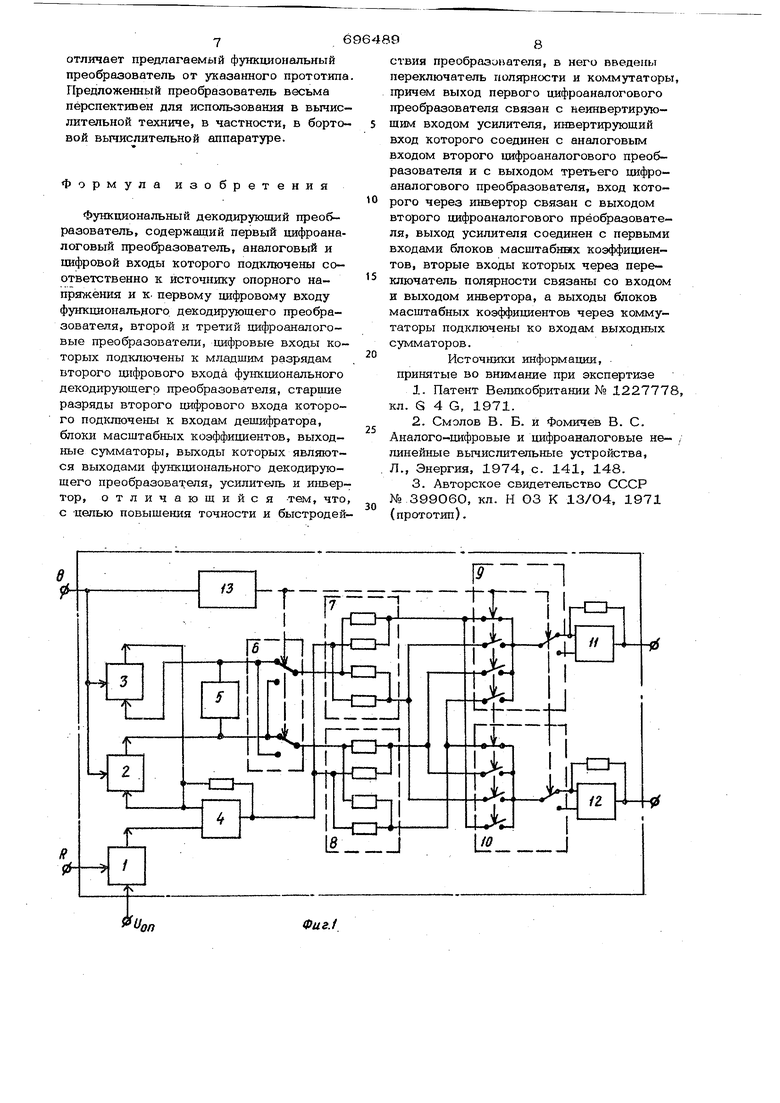

Изобретение относится к области вычислительной техники и техники преобразования и предназначено для кспользования как в качестве самостоятельного вычислительного блока спешшлизированных вычислительных машин или устройств, в частности, в навигационном оборудовании, аппаратуре для расчета траекторий и в установках для моделирования условий полета, так и в качестве буферного блока между цифровой вычислительной машиной и аналоговым или гибридным процессором в аналого-цифровых комплексах. Известны функциональные декодирующие преобразователи, преобразующие двоично-кодированные сигналы аргумента © в аналоговые сигналы синуса и косинуса этого аргумента 1 Основным недостатком известного пре образователя является либо низкая точность при сравнительно ;тростой конструкции шифратора и кодовых генераторов синуса и косинуса, либо значительные аппаратурные затраты для достижения погреш ности преобразования, близкой к погрешности дискретности входной величины. Кроме того, сложность таких преобразователей значительно возрастает, а быстродействие уменьшается, с ростом длины преобразуемого цифрового спова. Известны также функциональные декоД1фующие преобразователи, реализующие кусочно-полиноминальную агафоксимацию функций полиномами Лагранжа 2. Функциональные ьозможности преобразователей подобного Т1ша ограничены. Наиболее близким по технической сущности к предложешсому изобретению является функциональный декодирующий преобразователь, содержащий первый цифроаналоговый преобразователь, аналоговый и цифровой входы которого подключены соответственно, к источнику опорного напряжения и к первому цифровому входу функционального декодирующего преобразователя, второй и третий цифроаналоговые преобразователи, цифровые входы которых подключены к младщим разрядам второго цифрового входа функционального декодирующего преобразователя, старшие разряды второго цифрового входа которого подключены к входам дешифратора, блоки масштабных коэффициентов, выходные сумматоры, выходы которых являются 6ыходами функциональ ного декодирующего преобразователя,, усилитель и инвертор з. Недостатком известного преобразователя является его сложность, которая, в свою очередь, приводит к снижению точности и быстродействия. Цель изобретения - повышение точное ти и быстродействия преобразователя. Поставленная цель достигается тем, что введены переключатель полярности и коммутаторы, причем выход первого цифроаналогового преобразователя связан с неинвертирующим входом усилителя, инвертирующий вход которого соединен с аналоговым входом второго цифроанало- гового преобразователя и с выходом третьего иифроаналогового преобразовате ля, вход которого через шшертор связан с выходом второго иифроаналогового преобразователя, выход усилителя соединей с первыми входами блоков масштабных коэффициентов, вторые входы которых через переключатель полярности свя заны со входом и выходом HiisepTopa, а выходы блоков масштабных коэ)фиш1ентов через коммутаторы подключены ко входам выходных сумматоров. На фиг. 1 представлена схема функци онального декодирующего преобразоватегля; на фиг. 2 изображены эшоры напряжений, поясняющие его работу; на фиг. 3 - представлена схема получения щ)и помощи преобразователя функциональных зависилгостей T3tgJt0 (7 ctg Jt0) и Я sec УС Q(T собес atQ). ycTpoifcTBO содержит первый цифроаналоговый преобразователь 1 аргул енТа R, второй и третий цифроаналоговый преобразователи 2 и 3 аргумента 0, при чем входное сопротивление преобразователя 2 и выходное сопротивле1ше преобразователей 1 и 3 постоянны и не зависят от преобразуемого кода, усилитель 4с дифферен1шальным входом; инвертор 5переключателя полярности б с синхрон ным и противофазным переключением кон тактов, двух блоков масштабных коэффициентов 7 и 8, количество резисторов в которых равно количеству участков аппроксимации в интервале изменения аргу мента ® от в до 1/2; коммутаторов S и 10 и выходных сумматоров 11 и 12, дешифратор 13. На фиг. 2 обозначены: TJ - напряжение на выходе усилителя 4; 17 ХТ напряжения, соответственно, на входе и выходе инвертора 5; UA. | TJg напряжения на выходах переключателя полярности 6; Q - напряжения на выходах сумматора 11 и 12 - выходные напряжения преобразователя. Значения всех напряжений даны в функции аргумента @, иамен5пощегося в диапазоне от +1 до 1. Цифрами на эпюрах обозначены участки аппроксимации. Для конкретносte схема фиг. 1 и эпюры фиг. 2 приведены для 16 участков аппроксимации во всем диапазоне изменения аргумента @, кроме того, на эпюрах фиг. 2 аргумент R const . На фиг. 3 - приведена укрупненная схема преобразователя. Как было указано выше, предлагаемый функциональный декодирующий преобразователь осуществляет одновременно операции Ш1фроаналогового и фушсционального преобразования над двоично-кодированными сигналами и, представленные выражениями:x -RcOsJCQ Я u KsinfftQ (1) При этом в преобразователе реашгзована одна из оптимальных аппроксимаций рядами по полиномам Чебышева второго порядка в соответствии с выражениями:T 5in3te Si (1 P -SRP2 +V l co6are-Sn.., ( sRli)-Si P И R - полиномы Чебышева, соответственно нулевого, первого и второго порядков, причем . , S - некоторая постоянная в гфеделах i-го участка, равная osinJtQj, где i 1, 2, З...П ; 0J - значение аргумента в в середине j -го участка;П - количество участков аппроксимации в интервале изменения б от О до 1/2; - текущие значения аргументов;

C,S|k. - некоторые постоянные, зависящие от количества участков аппрокси- маш1И.

Благодаря быстрой сходимости рядов по полиномам Чебышева, удается, уже при небольшом количестве участков и невысоком порядке аппроксимирующего ряда достичь незначительной методической погрешности. Так при кусочно-квадратхгчной аппроксимации выражений (1) рядом по полиномам Чебышева, при количестве участков rt А 4, даже при условии равномерного разбиения на участки интервал изменения @ (что особенно важно для существенного упрощения дешифратора 13 и блоков масштабных коэффициентов 7 и 8) методическая погрешность не превышает 0,03%. Из вьфажений (2) вид-но, что коэффициент при линейной составляюшей разложения. SinSC© CR cos ,Jt0) и при разности постоянной и квадратичной составляющих разложения Т cos JC© (R sin ОС©) равны с точностью до постоянного множителя К. Кроме того, все эти коэффициенты принадлежат одному набору коэффициентов Sl . Это позволило использовать два идентичных по конструкции и номиналам блоков 7 и 8, а также сократить количество резисторов в них.

Предлагаемый функциональный декодирующий преобразователь работает следующим образом. Цифровой код аргумента I, после преобразова1шя в цифроаналоговом преобразователе 1, поступает на неинвертирующкй вход усилителя 4, при этом напряжение на неинвертирующем входе изменяется пропорционально значению аргумента R. В силу особенности работы усилителя с дифференциальным входом, напря5ке1ше на его инвертирующем входе следит за напряжением на неинвертирующем входе. Значение напряжения на инвертирующем входе усилителя 4 умножается преобразователем 2 на код аргумента © с образованием на выходе преобразователя 2 произведешь К R® в аналоговой форме (эпюра 1/2 фиг. 2). Далее через инвертор 5 сигнал поступает на вход цифроаналогового преобразователя 3 для повторного умножения на код аргумента © с образованием на выходе преобразователя 3 произведения 2SR0. Таким образом, на выходе усилителя 4 образуется напряжение, соответствующее выражению в скобках разложений (2). На входе и выходе

инвертора 5 образуются два равных к противоположшз1х по знаку напряжения треугольной формы (эпюры Ifgi и Uj , фиг.. 2), из которых при помощи переключателя полярности 6, образуются напряжеьшя, соответствующие линейной составляющей ± KRe разложений (2), представленных на эпюрах U. и XJg фиг. 2. Блоками 7 и 8 через коммутаторы 9 и 10 и выходные сумматоры 11 к 12 осуществляется сумм1фова1{ие по участкам составляющих разложений (2) с соответствующими коэффициентами i Изменение знака выходных величин осущ.эствляется коммутаторами 9 и 10 переключением входных цепей выходных сумматоров 11 и 12 с инвертирующего входа на неи1терт1фующий или обратно. Младшие разряды кода аргумента О поступают на цифроаналоговые преобразо атели 2 и 3, а его старшие разряды преобразуются дешифратором 13 в сигналы управления коммутаторами 9 к 1О и переключателем 6.

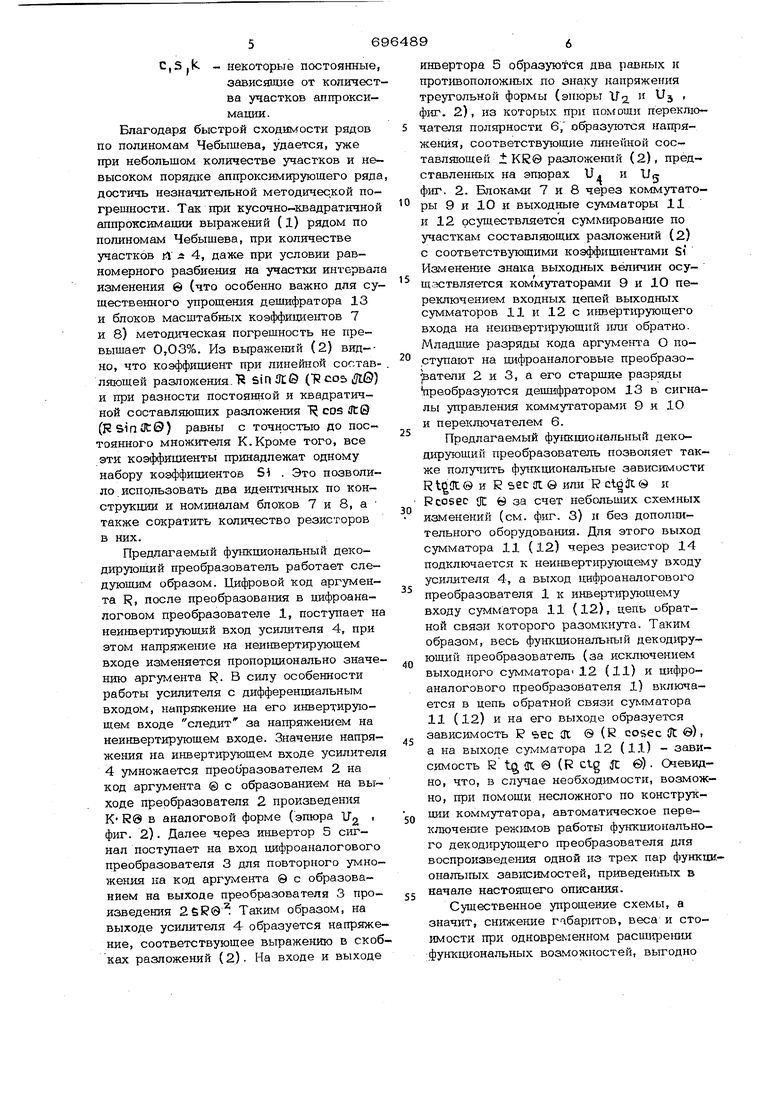

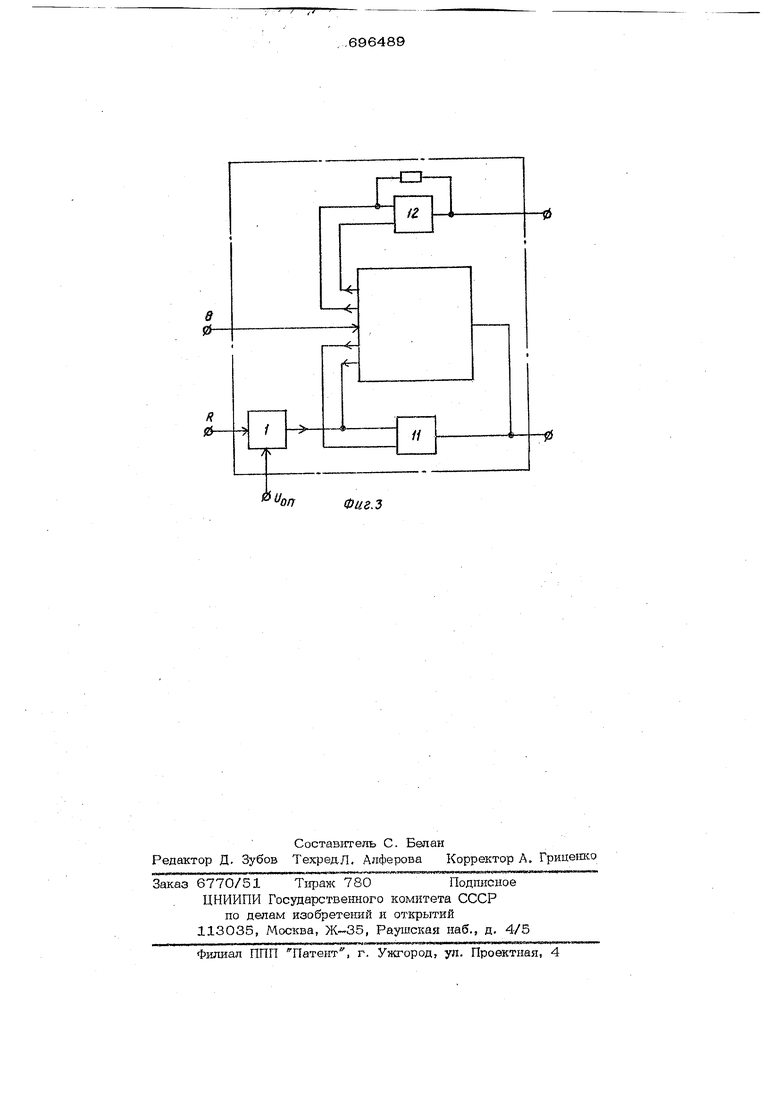

Предлагаемый фушсциональный декоД1ФУЮЩИЙ преобразователь позволяет также получить фушсциональные зависимости R ® и R sec ilt О или R ct jt 0 и Rcosec on 8 за счет небольших схемных изменений (см. фиг. 3) и без допол1штельного оборудования. Для этого выход сумматора 11 (12) через резистор 14 подключается к неинБерт1фу1ощему входу усилителя 4, а выход цифроаналогового преобразователя 1 к инверт.1фующему входу сумматора 11 (12), цепь обратной связи которого разомкнута. Таким образом, весь функциональ1ПзШ декод1фующий преобразователь (за исключением выходного сумматора- 12 (11) и цифроаналогового преобразователя 1) включается в цепь обратной связи cy гмaтopa 11 (12) и на его выходе образуется зависимость R еес 31 © (R cosec dt ©). а на выходе сумматора 12 (11) - зави- сшчЮсть R Ц (ГС 6 (R ctg JC в). Счевидно, что, в случае необходимости, возможно, при помощи несложного по конструкции коммутатора, автоматическое переключение режимов работы футгкнионального декод1фующего преобразователя для воспроизведения одной из трех пар функционалыштх зависимостей, приведенных в начале настоящего описания.

Существенное упрощение схемы, а значит, снижение пбариггов, веса и стоимости при одновременном функциональных возможностей, выгодно 76 отличает предлагаемый функциональный преобразователь от указанного прототипа Предложенный преобразователь весьма перспективен для использования в вычис лительной техниче, в частности, в борто вой вычислительной аппаратуре. Формула изобретения Функциональный декодирующий преобразователь, содержащий первый цифроаналоговый преобразователь, аналоговый и цифровой входы которого подключены соответственно к источнику опорного напряжения и к. первому цифровому входу функциональрого декодирующего преобразователя, второй и третий цифроаналоговые преобразователи, цифровые входы которых подключены к младшим разрядам второго цифрового входа функционального декоддфующегр преобразователя, старшие разряды второго цифрового входа которого подюпочены к входам дешифратора, блоки масштабных коэффициентов, выходные сумматоры, выходы которых являются выходами функционального декодирующего преобразователя, усилитель и тор, отличающийся -тем, что с -целью повышения точности и быстродей 9 сгвия преобразователя, в него введены переключатель полярности и коммутаторы, гфичем выход первого цифроаналогового преобразователя связан с неинвертирующим входом усилителя, инвертирующий вход которого соединен с аналоговым входом второго цифроаналогового преобразователя и с выходом третьего цифроаналогового преобразователя, вход которого через инвертор связан с выходом второго цифроаналогового преобразователя, выход усилителя соединен с первыми входами блоков масштабннх коэффициентов, вторые входы которых через переключатель полярности связаны со входом и выходом инвертора, а выходы блоков масштабных коэффициентов через коммутаторы подключены ко входам выходных сумматоров. Источники информации, принятые во внимание при экспертизе 1.Патент Великобритании № 1227778, кл. G 4 G, 1971. 2.Смолов В. Б. и Фомичев В. С. Аналого-цифровые и цифроаналоговые не- / линейные вычислительные устройства, Л., Энергия, 1974, с. 141, 148. 3.Авторское свидетельство СССР №399060, кл. Н ОЗ К 13/О4, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Гибридный синусно-косинусный функциональный преобразователь | 1978 |

|

SU752394A1 |

| Гибридный функциональный преобразователь | 1982 |

|

SU1076918A1 |

| Синусно-косинусный цифро-аналоговый преобразователь | 1979 |

|

SU781835A1 |

| Гибридный функциональный цифроаналоговый преобразователь со сплайновой аппроксимацией n-го порядка | 2016 |

|

RU2628918C1 |

| Функциональный преобразователь | 1979 |

|

SU830430A1 |

| Цифро-аналоговый функциональный преобразователь | 1977 |

|

SU734748A1 |

| Цифро-аналоговый функциональный преобразователь | 1976 |

|

SU572815A1 |

| Функциональный преобразователь | 1982 |

|

SU1049929A1 |

| Дробно-рациональный цифроаналоговый преобразователь | 1980 |

|

SU896646A1 |

| Цифро-аналоговый многофункциональный преобразователь | 1982 |

|

SU1062732A2 |

Фиг.1

оп

Фиг.з

Авторы

Даты

1979-11-05—Публикация

1976-10-21—Подача