(54) ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1980 |

|

SU894748A1 |

| Функциональный преобразователь двух переменных | 1978 |

|

SU698010A1 |

| Гибридный функциональный преобразователь | 1982 |

|

SU1076918A1 |

| Гибридный функциональный преобра-зОВАТЕль | 1979 |

|

SU834726A1 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

| Функциональный преобразователь | 1983 |

|

SU1166147A1 |

| Устройство для воспроизведения переменных во времени коэффициентов | 1980 |

|

SU894737A1 |

| Вычислительное устройство | 1981 |

|

SU1001114A1 |

| Цифро-аналоговый функциональный преобразователь | 1980 |

|

SU895973A1 |

| Функциональный преобразователь | 1981 |

|

SU1018127A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано, в частности .в гибридных вычислительных системах и устройствах. Известен функциональный преобразователь, содержащий блок управления, многостабильный элемент, коммутаторы и блоки задания абсцисс и ординат, широтно-импульсный модулятор, блок буферных усилителей и выходной нелинейный интерполятор 1. Известен также функциональный преобразователь, содержащий регистр аргумента, цифроаналоговые преобразователи, управляемые делители напряжения, дещифратор, функциональную проводимость и операционный усилитель 2. Недостаток этих устройств - конструктивная сложность. Наиболее близким по технической сущности и достигаемому результату к предлагаемому является функциональный преобразователь, содержащий аналого-цифровой преобразователь, подключенный входом к шине ввода аргумента и к сигнальному входу управляемого инвертора, а выходами - к входам блока памяти, выходы которого соединены со входами первого и второго регистров, подключенных выходами разрядов к цифровым входам соответственно первого и второго цифроаналоговых преобразователей, соединенных выходами с входами выходного сумматора, причем аналоговый вход первого цифроаналогового преобразователя подключен к выходу управляемого инвертора, соединенного управляющим входом с выходом знакового разряда первого регистра, а аналоговые входы второго цифроаналогового преобразователя подключены к щинам опорных напряжений 3. Недостатком этого преобразователя при фиксированном объеме блока памяти является пониженная точность функционального преобразователя, что обусловлено использованием только кусочно-линейного характера аппроксимации функций. Цель изобретения - повыщение точности функционального преобразования. Поставленная цель достигается тем, что в функциональный преобразователь, содержащий аналого-цифровой преобразователь, подключенный входом к шине ввода аргумента, а выходами - к йходам блока памяти, выходы которого соединены со входами первого и второго регистров, подключенных выходами разрядов к цифровым входам соответственно первого и второго цифроаналоговых преобразователей, соединенных выходами с входами выходного сумматора, причем аналоговый вход первого цифроаналогового преобразователя подключен к выходу управляемого инвертора, соединенного управляющим входом с выходом знакового разряда первого регистра, а аналоговые входы второго цифроаналогового преобразователя подключены к шинам опорных напряжений, дополнительно введены множительный блок, триггер и управляемый переключатель, соединенный первым сигнальным входом с выходом множительного блока, вторым сигнальным входом - с шиной ввода аргумента и с входами множительного блока, выходом - с сигнальным входом управляемого инвертора, а управляющим входом - с выходом триггера, вход которого подключен к выходу признака функции блока памяти.

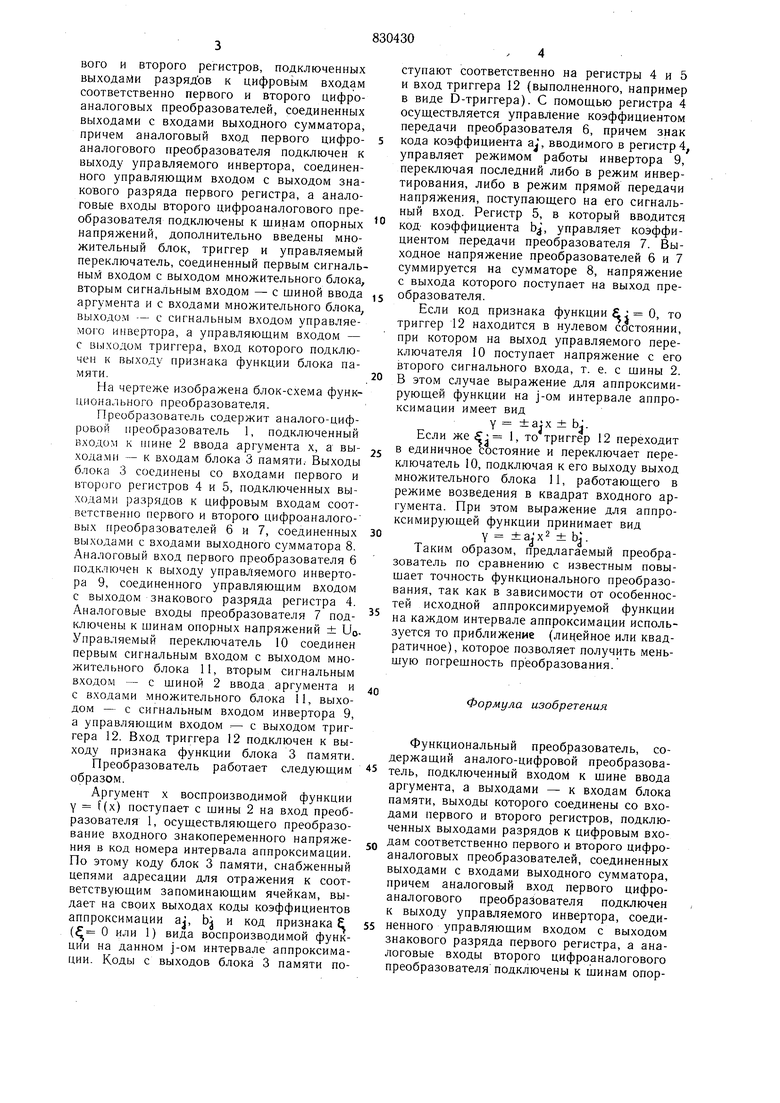

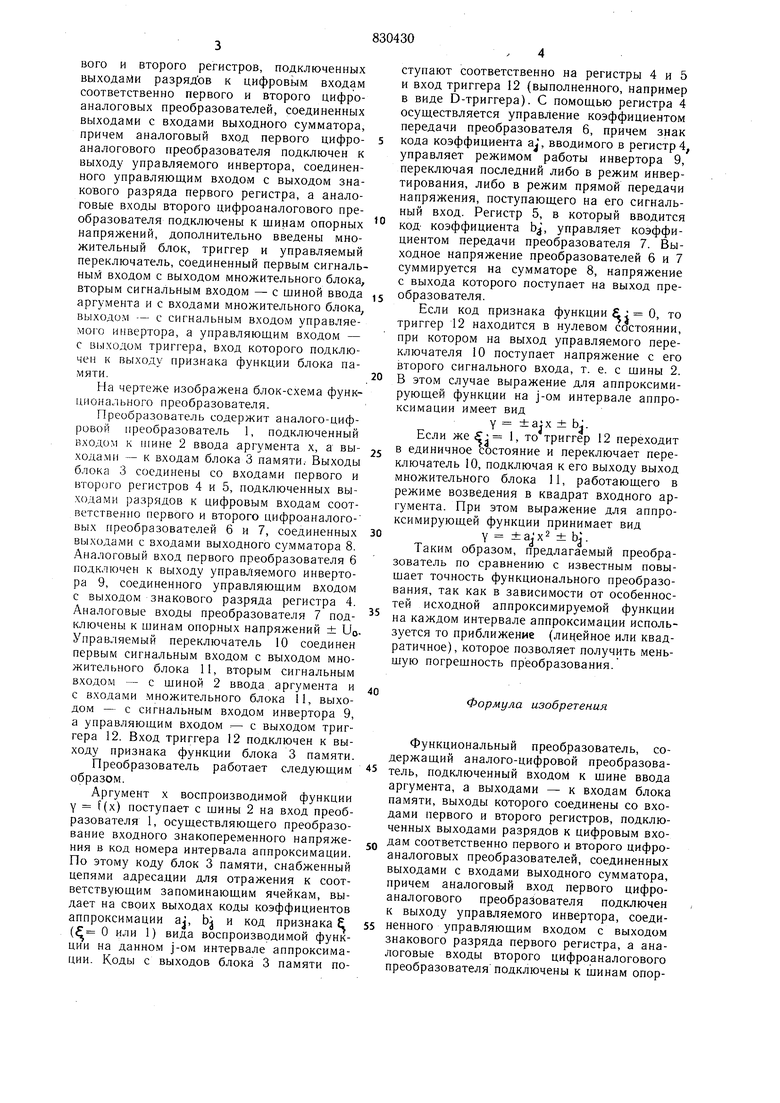

На чертеже изображена блок-схема функционального преобразователя.

Преобразователь содержит аналого-цифровой преобразователь 1, подключенный входом к шине 2 ввода аргумента х, а выходами - к входам блока 3 памяти.- Выходы блока 3 соединены со входа.ми первого и второго регистров 4 и 5, подключенных выходами разрядов к цифровым входам соответственно первого и второго цифроаналоговых преобразователей 6 и 7, соединенных выходами с входами выходного сумматора 8. Аналоговый вход первого преобразователя 6 подключен к выходу управляемого инвертора 9, соединенного управляющим входом с выходом знакового разряда регистра 4. Аналоговые входы преобразователя 7 подключены к шинам опорных напряжений ± Uo Управляемый переключатель 10 соединен первым сигнальным входом с выходом множительного блока 11, вторым сигнальным входом - с шиной 2 ввода аргумента и с входами множительного блока 11, выходом - с сигнальным входом инвертора 9, а управляющим входом - с выходом триггера 12. Вход триггера 12 подключен к выходу признака функции блока 3 памяти. Преобразователь работает следующим образом.

Аргумент X воспроизводимой функции у f(x) поступает с шины 2 на вход преобразователя 1, осуществляющего преобразование входного знакопеременного напряжения в код номера интервала аппроксимации. По этому коду блок 3 памяти, снабженный цепями адресадии для отражения к соответствующим запоминающим ячейкам, выдает на своих выходах коды коэффициентов аппроксимации aj, bj и код признака ( О или 1) вида воспроизводимой функции на данном j-OM интервале аппроксимации. Коды с выходов блока 3 памяти поступают соответственно на регистры 4 и 5 и вход триггера 12 (выполненного, например в виде D-триггера). С помощью регистра 4 осуществляется управление коэффициентом передачи преобразователя 6, причем знак

5 кода коэффициента , вводимого в регистр 4, управляет режимом работы инвертора 9, переключая последний либо в режим инвертирования, либо в режим прямой передачи напряжения, поступающего на его сигнальный вход. Регистр 5, в который вводится

° код коэффициента , управляет коэффициентом передачи преобразователя 7. Выходное напряжение преобразователей б и 7 суммируется на сумматоре 8, напряжение с выхода которого поступает на выход пре5 образователя.

Если код признака функции j О, то триггер 12 находится в нулевом состоянии, при котором на выход управляемого переключателя 10 поступает напряжение с его второго сигнального входа, т. е. с щины 2. 0 в этом случае выражение для аппроксимирующей функции на j-OM интервале аппроксимации имеет вид

Y ±ajx ± bj. Если же 1, то триггер 12 переходит

5 в единичное состояние и переключает переключатель 10, подключая к его выходу выход множительного блока 11, работающего в режиме возведения в квадрат входного аргумента. При этом выражение для аппроксимирующей функции принимает вид

30у ± aj X 2 ± bj

Таким образом, предлагаемый преобразователь по сравнению с известным повыщает точность функционального преобразования, так как в зависимости от особенностей исходной аппроксимируемой функции на каждом интервале аппроксимации используется то приближение (лицейное или квадратичное), которое позволяет получить меньшую погрешность преобразования.

Формула изобретения

Функциональный преобразователь, содержащий аналого-цифровой преобразователь, подключенный входом к щине ввода аргумента, а выходами - к входам блока памяти, выходы которого соединены со входами первого и второго регистров, подключенных выходами разрядов к цифровым входам соответственно первого и второго цифроаналоговых преобразователей, соединенных выходами с входами выходного сумматора, причем аналоговый вход первого цифроаналогового преобразователя подключен к выходу управляемого инвертора, соединенного управляющим входом с выходом знакового разряда первого регистра, а аналоговые входы второго цифроаналогового преобразователя подключены к Ц1инам опорных напряжений, отличающийся тем, что, с целью повышения точности функционального преобразования, в него дополнительно введены множительный блок, триггер и управляемый переключатель, соединенный первым сигнальным входом с выходом множи тельного блока, вторым сигнальйым входом - с шиной ввода аргумента и с входами множительного блока, выходом - с сигнальным входом управляемого инвертора, а управляющим входом - с выходом триггера.

вход которого подключен к выходу признака функции блока памяти.

Источники информации, принятые во внимание при экспертизе

№ 698010, кл. G 06 G 7/26, 1978 (прототип).

Авторы

Даты

1981-05-15—Публикация

1979-08-29—Подача