1

Изобретение относится к радиотехнике и может использоваться для автоматического выбора скорости приемного факсимильного аппарата при работе по цифровому каншгу.

Известно устройство для автоматического выбора скорости приемного факсимильного аппарата, содержащее триггер, п генераторов эталонных импульсов, первое и второе реле времни, сумматор, ключ начала счета и блок управления, причем выход триггера подключен к первым входам п генераторов эталонных импульсов и к первому входу первого реле времени, второй вход которого подключен к выходу второго реле времени и к второму входу ключа начала счета, а выход первого реле времени подключен к вторым входам п генераторов эталонных импульсов и к второь у входу триггера, выход сумматора подключен к входу второго реле времени и к первому входу ключа начала счета, выход которого подключен к соответствующему входу блока управления 1.

Одаако известное устройство обладает низким быстродействием и помехоустойчивостью.

Цель изобретения - повышение быстродействия и помехоустойчивости.

Для этого в устройство для автоматического выбора скорости приемного факсимильноп агтарата, содержащее триггер, п генераторов эталонных импульсов, первое и второе реле времени, сумматор, ключ начала счета и блок управления, причем выход триггера подключен к первым входам п генераторов эталонных импульсов и к первому входу первого реле времени, второй вход которого подключен к выходу второго реле времени и к второму входу ключа начала счета, а выход первого реле времени подключен к вторым входам п генераторов эталонных импульсов и к второму входу триггера, выход сумматора подключен к входу второго реле времени, и к первому входу ключа начала счета, выход которого подключен к соответствуюи1ему входу блока управления, введены последорательно соединенные дискриминатор фазовых импульсов и преобразователь серии импульсов Б одиночный, п времет1ых селекторов, п триггеров памяти, блок неравнозначности и э.г еменг ИЛИ. Вьгхоц иреобразователя серии импульсов в одиночный подключен к первому входу триггера и к первым входам.п временных селекторов, к вторым входам которых подключены п генераторов эталонных импульсов соответственно. Выходы п временных селекторов подключены к соответствующим входам сумматора и к первым входам п трштеров памяти, к вторым входам которых через элемент ИЛИ подключей выход первого реле времени. Вькоды п триггеров памяти подключены к соответствующим входам блока управления и блока неравнозначности, выход которого соединен с соответствующим входом элемент ИЛИ.

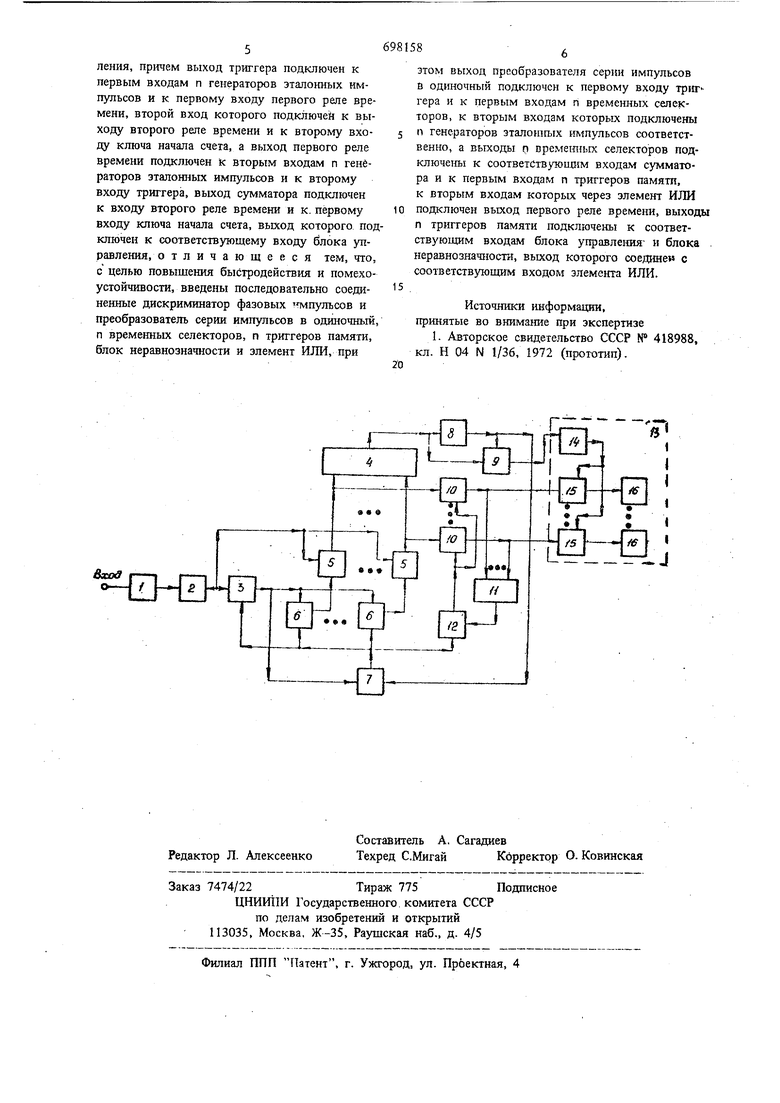

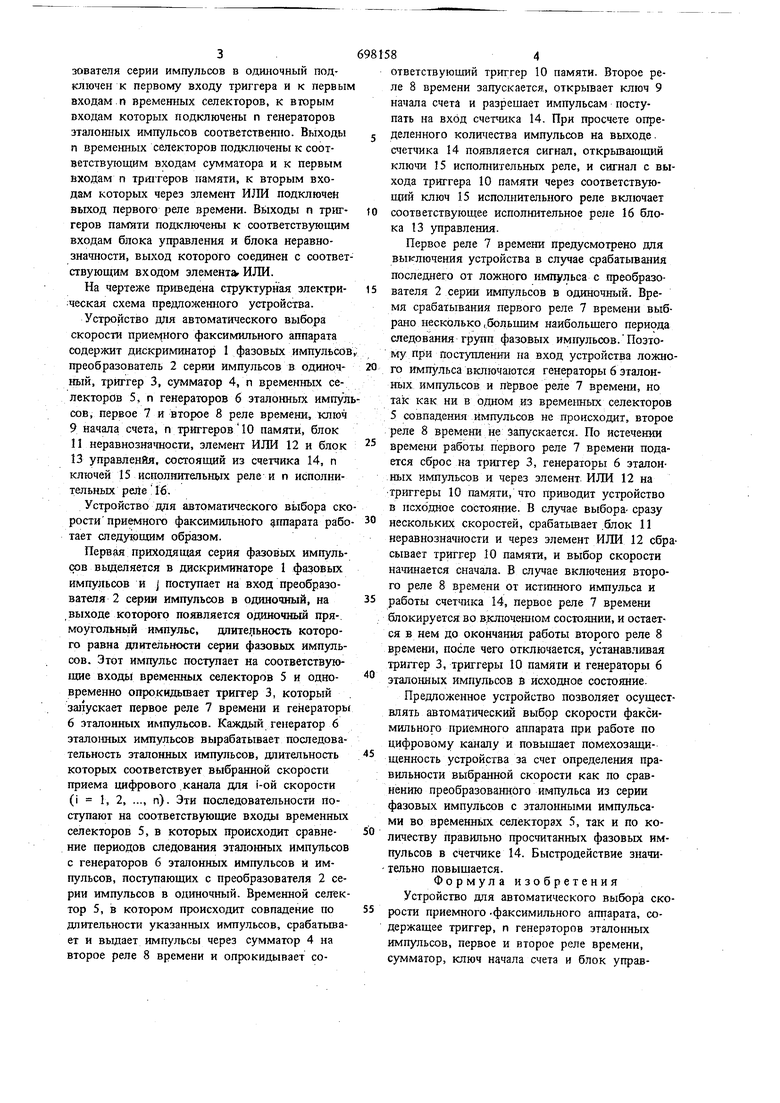

На чертеже приведена структурная электри ческая схема предлох енного устройства.

Устройство для автоматического выбора скорости приемного факсимильного аппарата содержит дискриминатор 1 фазовьгх импульсов преобразователь 2 серии импульсов в одиночный, триггер 3, сумматор 4, п временных селекторов 5, п генераторов б эталонньгх импулсов, первое 7 и второе 8 реле времени, ключ 9 начала счета, п триггеров10 памяти, блок 11 неравнознашости, элемент ИЛИ 12 и блок 13 управления, состоящий из счетчика 14, п ключей IS исполнительньге реле и п исполнительных реле . 16.

Устройство для автоматического выбора скорости приемного факсимильного аппарата рабо тает следующим образом.

Первая приходящая серия фазовых импульсов вьщеляется в дискриминаторе 1 фазовых импульсов и J поступает на вход преобразователя 2 серии импульсов в одиночный, на выходе которого появляется одиночный прямоугольный импульс, длительность которого равна длительности серии фазовых импульсов. Этот поступает на соответствующие входь временных селекторов 5 и одновременно опрокидьшает триггер 3, который зшзускает первое реле 7 времени и генераторы 6 эталонных импульсов. Каждый генератор 6 эталонных импульсов вырабатывает последовательность эталонных импульсов, длительность которых соответствует выбранной скорости приема Щ1ФРОВОГО .канала для i-ой скорости (i I, 2, ..., п). Эти последовательности поступают на соответствующие входы временных селекторов 5, в которых происходит сравнение периодов следования эталонных импульсов с генераторов б эталонных импульсов и импульсов, поступающих с преобразователя 2 серии импульсов в одиночный. Временной селектор 5, в котором происходит совпадение по длительности указанных импульсов, срабатьшает и вьщает импульсы через сумматор 4 на второе реле 8 времени и опрокидывает соответствующий триггер 10 памяти. Второе реле 8 времени запускается, открывает ключ 9 начала счета и разрещает импульсам поступать на вход счегшка 14. При просчете определенного количества импульсов на выходе. счетчика 14 появляется сигнал, открьшающий ключи 15 исполнительных реле, и сигнал с выхода триггера 10 памяти через соответствующий ключ 15 исполнительного реле включает соответствующее исполнетельное реле 16 блока 13 управления.

Первое реле 7 времени предусмотрено для выключения устройства в случае срабатывания последнего от ложного импульса с преобразователя 2 серии импульсов в одиночный. Время срабатывания первого реле 7 времени выбрано несколько ,больщим наибольщего периода следования групп фазовых импульсов.Поэтому при поступлении на вход устройства ложного импульса включаются генераторы 6 эталонных импульсов и первое реле 7 времени, но так как ни в одном из време шых селекторов 5 совпадения импульсов не происходит, второе реле 8 времени не Запускается. По истечении времени работы первого реле 7 времени подается сброс на триггер 3, генераторы 6 эталонных импульсов и через элемент- ИЛИ 12 на триггеры 10 памяти, что приводит устройство в исходное состояние. В случае выбора- сразу нескольких скоростей, срабатьшает .блок 11 неравнозначности и через элемент ИЛИ 12 сбрсывает триггер 10 памяти, и выбор скорости начинается сначала. В случае включения второго реле 8 времени от ист1шного импульса и работы счетчика 14, первое реле 7 времени блокируется во выключенном состоянии, и остается в нем до окончания работы второго реле 8 времени, после чего отключается, устанавливая триггер 3, триггеры 10 памяти и генераторы б эталонных импульсов в исходное состояние.

Предложенное устройство позволяет осуществлять автоматический выбор скорости факсимильного приемного аппарата при работе по цифровому каналу и повыщает помехозащищенность устройства за счет определения правильности выбранной скорости как по сравнению преобразованцого импульса из серии фазовых импульсов с эталонными импульсами во временнь1х селекторах 5, так и по количеству правильно просчитанных фазовых импульсов в счетчике 14. Быстродействие значительно повыщается.

Формула изобретения

Устройство для автоматического выбор;а скорости приемного -факсимильного аппарата, содержащее триггер, п генераторов эталонных импульсов, первое и второе реле времени, сумматор, ключ начала счета и блок управления, причем выход триггера подключен к первым входам п генераторов эталонных импульсов и к первому входу первого реле времени, второй вход которого подключей к выходу второго реле времени и к второму входу ключа начала счета, а выход первого реле времени подключен к вторым входам п генераторов эталонных импульсов и к второму входу триггера, выход сумматора подключен к входу второго реле времени и к. первому входу ключа начала счета, выход которого подключен к соответствующему входу блока управления, о тличающееся тем, что, с целью повышения быстродействия и помехоустойчивости, введены последовательно соединенные дискриминатор фазовых мпульсов и преобразователь серии импульсов в одиночный, п време1шых селекторов, п триггеров памяти, блок неравнозначности и элемент ИЛИ, при

ЭТОМ выход преобразователя серии импульсов в одиночный подключен к первому входу триггера и к первым входам п временных селекторов, к вторым входам которых подключены п генераторов эталошшгх импульсов соответственно, а выходы о премеш1ых селекторов подключень к соответСтвуюцщм входам сумматора и к первым входам п триггеров памяти, к вторым входам которьгх через элемент ИЛИ подключен выход первого реле времени, выходы п триггеров памяти подключены к соответствующим входам блока управления- и блока неравнозначности, выход которого соединен с соответствующим входом элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР P 418988, кл. Н 04 N 1/36, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического выбора скорости приемного факсимильного аппарата | 1980 |

|

SU896790A1 |

| Устройство для автоматического выбора скорости приемного факсимильного аппарата | 1981 |

|

SU995370A1 |

| Устройство для автоматического выбора скорости приемного приемного факсимильного аппарата | 1976 |

|

SU590866A2 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО ВЫБОРА СКОРОСТИ ПРИЕМНОГО ФАКСИМИЛЬНОГО АППАРАТА | 1972 |

|

SU418988A1 |

| Устройство для автоматического выбора скорости приемного факсимильного аппарата | 1981 |

|

SU1008925A2 |

| Устройство кодирования видеосигнала | 1986 |

|

SU1420657A1 |

| Селектор импульсов по длительности | 1978 |

|

SU879761A2 |

| Селектор импульсов по длительности | 1986 |

|

SU1352629A1 |

| Факсимильный передатчик | 1981 |

|

SU1019664A1 |

| Устройство сжатия факсимильных сигналов | 1980 |

|

SU1107339A1 |

Авторы

Даты

1979-11-15—Публикация

1978-01-25—Подача