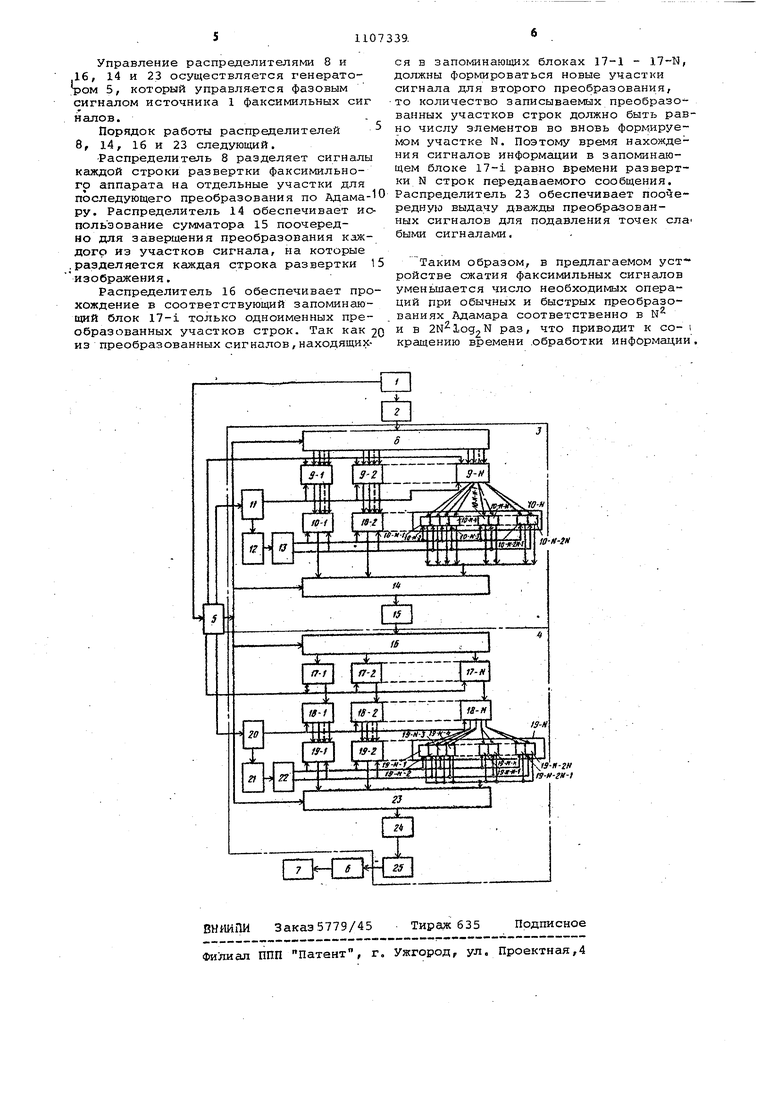

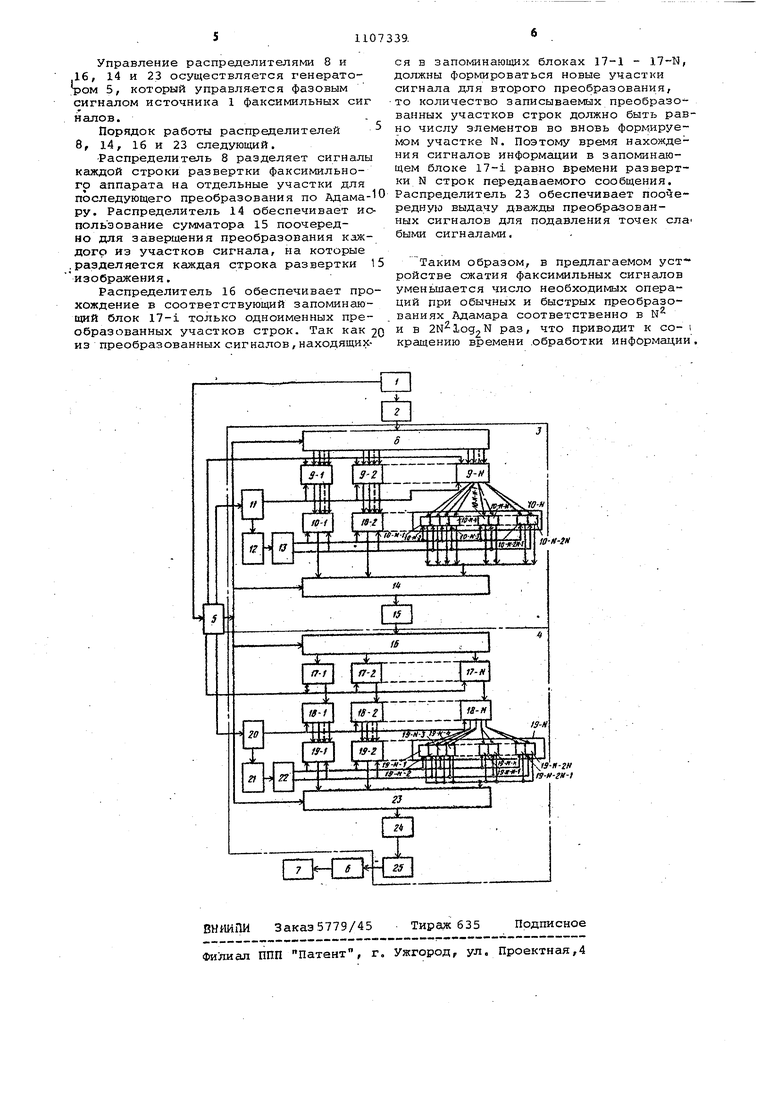

i1 Изобретение относится к технике обработки, формирования и передачи сигналов изображения. Известно устройство сжатия факсимильных сигналов, основанное на двух ступенчатом преобразовании сигналов, содержащее блоки сокращения избыточности по строкам и по столбцам, в первом из которых используется ортогональное преобразование, требующее N операций и 2N log2N, где N - число элементовв строке (столбце)матри цы Адамара, при быстром преобразовании .Адамара, а во втором используютс преобразования на основе апертурных алгоритмов CiJЭто устройство обладает большой сложностью, обусловленной значитель ным числом операций в первой ступени преобразования, и ограниченными возможностями по качествуобработки передаваемых сигналов. Наиболее близким к изобретению по технической сущности является устрой ство сжатия факсимильных сигналов, содержащее дискретизатор, вход которого соединен с выходом источника факсимильных сигналов, а выгод - с входом аналого-цифрового преобразова теля, блоки сокращения избыточности по строкам и по столбцам, входы кото рых объединены с входом элемента запрета и подключены к выходу аналогоцифрового преобразователя, выход блока сокращения избыточности по стр кам через генератор адресной информации подключен к первому входу сумматора, выход блока сокращения избыточности по столбцам через управляющий элемент - к второму элементу запрета, выход которого подключен чере сумматор к входу блока памяти, выход которого соединен с входом кодера 2 Недостатком известного устройства является значительное время, затрачиваемое на обработку информации, при реализации а.лгоритма ортогональн го преобразования с матрицами, произ водящими N вычислительных операций на Каждый фрагмент из NxN элементов сообщения. Кроме того, при использовании быстрых преобразований Адамара в составе устройства необходимо иметь запоминающие блоки большой емкости на весь объем передаваемого сообщения. Целью изобретения является сокращение времени обработкг информации. Эта цель достигается тем, что в устройство сжатия факсимильных сигна лов, содержащее дискретизатор, вход которого соединен с выходом источника факсимильных сигналов, блок сокра щения избыточности по строкам, блок сокращения избыточности по столбцам, последовательно соединенные блок памяти и кодер, информационные вход бл ка сокращения избыточности по строкам подключен к выходу дискретизато9ра, а выход - к информационному входу блока сокращения избыточности по столбцам, выход которого соединен с входом блока памяти. Кроме того, блок сокращения избыточности по строкам содержит N буферных регистров, входы каждого из которых соединены -с соответствующими выходами распределителя импульсов входных сигналов, вход которого является информационным входом блока сокращения избыточности по строкам, N коммутаторов, кажщт1й из которых состоит из 2N ключей, информационные входы каждого из которых соединены с выходами соответствующих буферных регистров, управляющие входы нечетных ключей каждого коммутатора объединены и подключены к неинвертированному выходу преобразователя сигналов, управляющие входы четных ключей объединены и подключены к инвертированному выходу преобразователя сигналов, вход которого соединен с выходом генератора функций Уолша, а выходы коммутаторов подключены через распределитель импульсов выходных сигналов к входу сумматора, выход которого является выходом блока сокращения избыточности по строкам. При,этом блок сокращения избыточности по столбцам содержит распределитель импульсов входных сигналов, вход которого является информационным входом блока сокращения избыточности по столбцам, N буферных регистров, вход каждого из которых через соответствующий запоминающий блок подключен к соответствующему выходу распределителя импульсов входных сигналов, N коммутаторов, каждый из которых состоит из 2N ключей, информационные входы каждого из которых соединены с выходами соответствующих буферных регистров, управляющие вхо- ды нечетных ключей каждого ко ммутатора объединены и подключены к неинвертированному выходу преобразователя сигналов, управляющие входы четных ключей объединены и подключены к инвертированному выходу преобразователя сигналов, вход которого соединен с выходом генератора функций Уолша, а выходы коммутаторов подключенЕ- к входам распределителя импульсов ззыходных сигналов, выход которого через сумматор соединен с входом амплитудtioro селектора, выход которого является выходом блока сокращения избы- точности по столбцам. На чертеже представлена структурная электрическая схема устройства сжатие: факсимильных сигналов. Устройство сжатия факсимильных сиг налов содержит источник 1 факсимильных сигналов, дискретизатор 2, блок 3 сокращения избыточности по строка блок 4 сокращения избыточности по

столбцам, генератор 5 тактовых импульсов, блок 6 памяти и кодер 7.

Блок 3 сокращения избыточности по строкам состоит из распределителя 8 мпульсов входных сигналов, буферных егистров 9-1 9-N, коммутаторов 5 10-1 - , каждый из которых содерит ключи 10-1-1 - 10-1-2Ы, 10-2-110-2-2N,..., 10-N-1 - 10-N-2N ,а таке из блока 11 управления, генератора 12 функций Уолша, преобразователя 13 Q сигнала, распределителя 14 импульсов ыходных сигналов и сумматор 15;

Блок 4 сокращения избыточности по столбцам состоит из распределителя 16 импульсов входных сигналов, запо- мг минающих блоков 17-1-17-N, буферных регистров 18-1 - 18-N, коммутаторов 19-1 - 19-N, каждый из которых соержит ключи 19-1-1 - 19-1-2N, 19-2-119-2-2N,..., 19-N-rl - 19-N-2N, а таке из блока 20 управления, генератора 20 21 функций Уолша, преобразователя 22 сигнала, раслределителя 23 импульсов выходных сигналов, сумматора 24 амплитудного селектора 25.

Устройство работает следующим об- 25 разом.

Факсимйльньзй сигнал с выхода источника 1 подается на вход дискретиэатора 2, с выхода которого в виде дискретной последовательности, им- 30 пульсы поступают на вход распределителя 8, формирующего участки строк, каждый из которых в дальнейшем подвергается преобразованию по Адамару. К каждому из выходов распределителя 35 8 подключен буферный регистр 9-i(i 1,...,N), рассчитанный на запись одного участка строки в N элементов.

По сигналам, поступающим с выхода блока 11 управления, производится новременное считывание с буферных регистров 9-i всех посылок преобразуемого участка строки на коммутатор 10-1, подключенный к буферным регистрам 9-i. При этом к каждой ячейке буферного регистра 9-i подключаются . по два ключа, например 10-N - N-1 и 10-N-N, которые управляются от генератора 12 функций УолШа. Сигналы с генератора 12 поступают через преобразователь 13 сигналов, на выходе ко-50 торого они получаются в виде неинвертированной и инвертированной двоичных последовательностей. Сигналы нёинвертированной последовательности управляют нечетными ключами 10-N-1, 55 10-N-3 и т.д., на выходе которых должны получаться сигналы типа , а сигналы инвертированной последовательности - четными ключами 10-N-2, 10-N-4 и т.д., на выходах которых . д должны быть сигналы типа , выходы ключей 10-N-i через распределитель Г4 подключаются к сумматору 15, выполненному,например I в виде реверсивного счетчика. Результат jyM 5

мирования в зависимости от соотноше +

на входе сумматония

и

ра 15 будет выдаваться на вход распр делителя 16. При этом с генератора 12 на обработку одного участка строки, находящего::я в буферном регистре 9-i, выдается N отрезков сигналов функций Уолша. Для обеспечения обработки одного, участка строки его сигналы за время одного цикла считываются с буферного регистра 9-i на ключи 10-N-i в N раз.

За счет парашлельной обработки л ментов необходимое количество операций равно N.

Выходы распределителя 16 подключены к входам запоминающих блоков 17-i (i 1,...,N) емкостью на N сигналов преобразованных участков строк передаваемого сообщения. Запись сигналов участка строки в запоминающий блок 17-i осуществляется последовательно. Поэтому после заполнения всех вертикальных дорожек по сигналу.с блока 20 управления производится считывание в буферные регистры l8-i параллельно J всех одноименных- элементов разных участков строк. Тем самым осуществляется формирование новых участков для сокраицения избыточности сообщения в направлении, перпендикулярном его с1-рочной развертке. К выходу каждого буферного регистра l8-i подключены оммутаторы l9-i аналогично тому, как в блоке 3, управление ключами . 19-1-1 - 19-1-2N,..., 19-N-1 - 19-N2N осуществляется от генератора 21 функций Уолша через преобраоователь 22 сигнала неинвертированным и инвертированным сигналами.

В запоминающем блоке 17-i, подключенном к i-му выходу распределителя 16, может находиться N преобразованных .сигналов участков из N элементов, а для преобразования вновь формируемых участков, каждый из которых также состоит из N одноименных элементов разных строк, генератор 21 должен выдать N двоичных последовательностей функций Уолша.

Сигналы с выходов ключей 19-1-1 19-1-2N,..., 19-N-1 - 19-N-2N поступают через распределитель 23 в сумматор 24, аналогичный по выполнению суг/1матору 15. Результат суммирования в зависимости от соотношения пог ложительных и отрицательных значений входных чисел выдается на амплитудный селектор 25 с цепью устранения избыточности и осуществления сжатия его.

К выходу амплитудного селектора 25 подключен вход блока 6 памяти, обеспечивающий выдачу информации в канал связи через кодер 7 с постоянной скоростью.

Управление распределителями 8 и .16, 14 и 23 осуществляется генератором 5, который управляется фазовым сигналом источника 1 факсимильных сиг налов.

Порядок работы распределителей

8, 14, 16 и 23 следующий.

Распределитель 8 разделяет сигналы каждой строки развертки факсимильного аппарата на отдельные участки для последующего преобразования по Адама-Ю ру. Распределитель 14 обеспечивает использование сумматора 15 поочередно для завершения преобразования каждого из участков сигнала, на которые .разделяется каждая строка развертки 15 изображения.

Распределитель 16 обеспечивает прохождение в соответствующий запоминающий блок 17-i только одноименных преобразованных участков строк. Так как 20 из преобразованных сигналов, находящихся Б запоминающих блоках 17-1 - 17-N, должны формироваться новые участки сигнала для второго преобразования, то количество записываемых преобразованных участков строк должно быть равно числу элементов во вновь формируемом участке N. Поэтому время нахождения сигналов информации в запоминающем блоке 17-i равно времени развертки N строк передаваемого сообщения. Распределитель 23 обеспечивает поочередную выдачу дважды преобразованных сигналов для подавления точек ела быми сигналами.

Таким образом, в предлагаемом уст ройстве сжатия факсимильных сигналов уменьшается число необходимых операций при обычных и быстрых преобразованиях ЗДамара соответственно в N и в 2N 1-092 N приводит к со- i кращению времени .обработки информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для разложения цифровых сигналов по Уолшо-подобным базисам | 1983 |

|

SU1108461A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| АДАПТИВНОЕ УСТРОЙСТВО ПОИСКА ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 1983 |

|

SU1840275A1 |

| Телеизмерительная система | 1982 |

|

SU1099322A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КОЭФФИЦИЕНТОВ БУЛЕВЫХ ПРЕОБРАЗОВАНИЙ НАД ПОЛЕМ ГАЛУА GF(2) | 2011 |

|

RU2475810C2 |

| Матричный параллельный процессор | 1984 |

|

SU1233169A1 |

| Устройство для приема дискретных сигналов | 1987 |

|

SU1501120A1 |

| УСТРОЙСТВО БЫСТРОГО ПРЕОБРАЗОВАНИЯ УОЛША-АДАМАРА | 1991 |

|

RU2023299C1 |

| Устройство для передачи телеметрической информации | 1983 |

|

SU1126993A1 |

| Устройство для редактирования | 1982 |

|

SU1117669A1 |

1. УСТРОЙСТВО СЖАТИЯ ФАК-СИМИЛЬНЫХ СИГНАЛОВ, содержащее дискретизатор, вход которого соединен с выходом источника фасимильных сигналов, блок сокращения избыточности по строкам, блок сокращения избыточности по столбцам, последовательно соединенные блок памяти и кодер, отличающееся тем, что, с целью сокращения времени обработки информации, информационный вход блока сокращения избыточности по строкам подключен к выходу дискретизатора, а выход - к информационному входу блока сокращения избыточности по столбцам, выход которого соединен.с входом блока памяти. 2. Устройство поп, 1, отличающееся тем, что блок сокращения избыточности по строкам содержит N буферных регистров, входы каждого из которых соединены с соответствующими выходами распределителя импульсов входных сигналов, вход которого является информационным входом блока сокращения избыточности по строкам, N коммутаторов, каждый из которых состоит из 2N ключей, информационные входы каждого из которых соединены с выходами соответствующих буферных регистров, управляющие вхо.ды нечетных ключей каждого коммутатора объединены и подключены к неинвертированному выходу преобразователя сигналов, управляющие входы четных ключей объединены и подключены к инвертированному выходу преобразователя сигналов, вход которого соединен с выходом генератора функций Уолша, а выходы коммутаторов подключены через распределитель импульсов выходных сигналов к входу сумматора, выход которого является выходом б;гока сокращения избыточности по строкам. 3. Устройство по п. 1, отличающееся тем, что блок сокращения избыточности по столбцам содержит распределитель импульсов входных сигналов, ВХОД которого являет- tg ся информационным входом блока сокрасл с: щения избыточности по столбцам, N буферных регистров, вход каждого из которых через соответствующий запоминающий блок подключен к соответствующему выходу распределителя импульсов входных сигнашов, N коммутаторов, каждый из которых состоит из 2 Л/ ключей,информационные входы каждого из которых соединены с выходами соответствующих буферных регистров, управляющие входы нечетных ключей каж дого коммутатора объединены и подклюсо чены к неинвертированному выходу преОО СО образователя сигналов, управляющие входы четных ключей объединены и подключены к инвертированному выходу преобразователя сигналов, вход которого соединен с выходом генератора функций Уолша, а выходы коммутаторов подключены к входам распределителя импульсов выходных сигналов, выход которого через сумматор соединен с входом амплитудного селектора,выход которого является выходом блока сокращения избыточности по столбцам.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Сйириденко В.Л | |||

| Анализ систем со сжатием данных М., Связь, 1977, с | |||

| Кровля из глиняных обожженных плит с арматурой из проволочной сетки | 1921 |

|

SU120A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сжатия двумерной информации | 1974 |

|

SU485489A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1984-08-07—Публикация

1980-01-14—Подача