(54) УСТРОЙСТВО ПОДАВЛЕНИЯ ДРЕБЕЗГА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подавления дребезга контактов @ выключателей | 1985 |

|

SU1305840A1 |

| Устройство для подавления дребезга контактов @ выключателей | 1988 |

|

SU1621155A1 |

| Устройство подавления дребезга | 1983 |

|

SU1120487A1 |

| Устройство подавления дребезга | 1984 |

|

SU1226628A1 |

| Формирователь дискретных сигналов | 1979 |

|

SU809523A1 |

| Устройство подавления дребезга | 1985 |

|

SU1305841A2 |

| Устройство подавления дребезга | 1978 |

|

SU743197A1 |

| Устройство подавления дребезга | 1986 |

|

SU1309284A2 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИМПУЛЬСОВ | 2003 |

|

RU2248089C1 |

| Цифроаналоговая следящая система | 1989 |

|

SU1700536A1 |

Изобретение относится к автоматике и вычислительной технике.

Известны устройства подавления дребезга, содержащие блок приема информации, генератор тактовых импульсов, резисторы, конденсаторы и замыкающие контакты 1.

К недостаткам известного устройства относится низкая Надежность функционирования.

Наиболее близким техническим решением к изобретению является устройство подавления дребезга, содержащее блок приема информации и генератор тактовых импульсов, а также в каждом канале два резистора, конденсатор, Dt-триггер и замыкающий контакт, подвижный контакт которого соединен с общей шиной, причем информационный вход D.t Триггера через первый резистор подключен к щине источника питания, а выходы - к соответствующим входам блока приема информации 2.

Недостаток такого устройства состоит в низкой надежности функционирования.

Цель изобретения - повыщение надежности устройства подавления дребезга.

Указанная цель достигается за счет того, что в устройстве подавления дребезга, содержащем блок приема информации и генератор тактовых импульсов, а также в каждом канале два резистора, конденсатор, D.триггер и замыкающий контакт, подвижный контакт которого соединен с общей щиной, причем информационный вход Dt-триггера через первый резистор подключен к щине источника питания, а выходы - к соответствующим входам блока приема информации, синхронизирующие входы D.t.-триггеров объединены и подключены к выходу генератора тактовых импульсов. При этом в каждом канале неподвижный контакт замыкающего контакта через второй резистор соединен с информационным входом D триггера и одной из обкладок конденсатора, вторя обкладка которого подключена к общей щине.

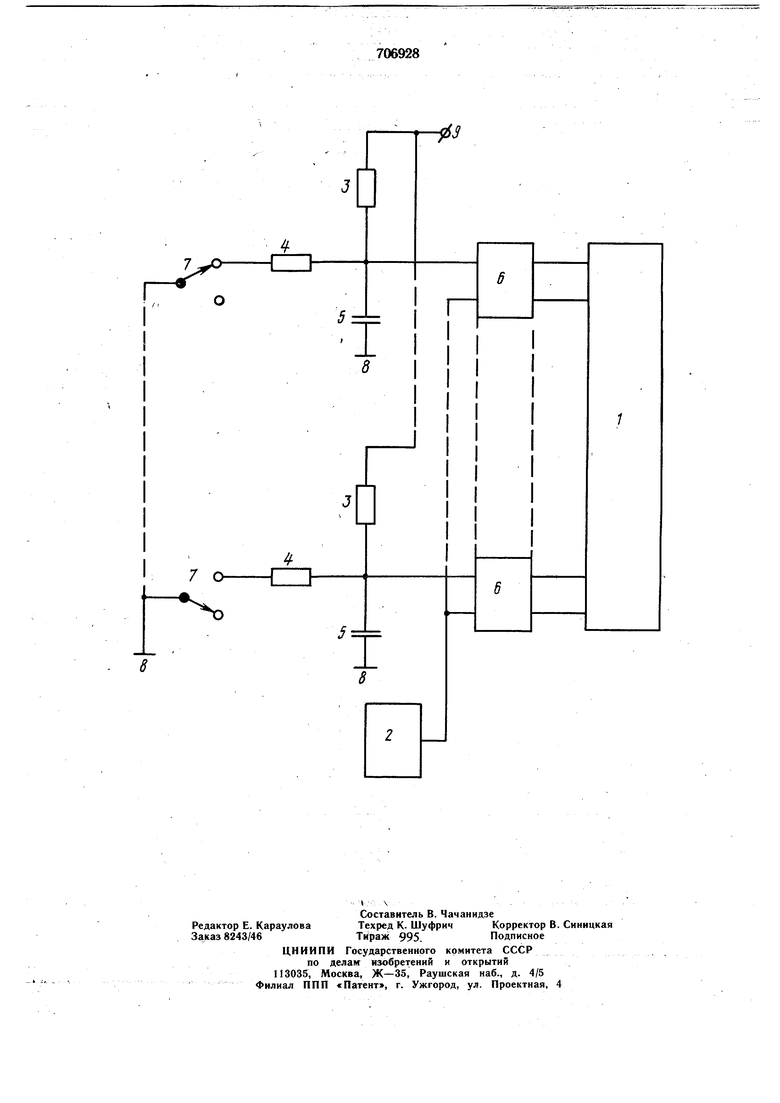

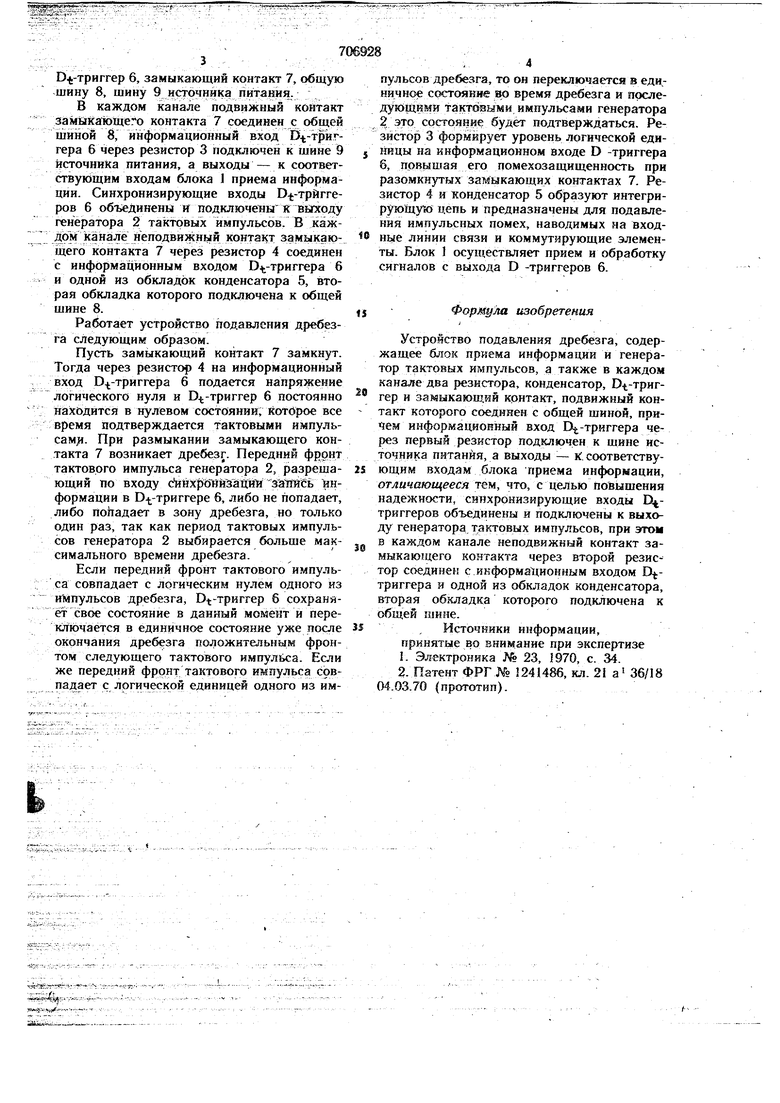

Схема устройства подавления дребезга представлена на чертеже.

Она содержит блок 1 приема информации, генератор 2 тактовых импульсов, первый 3 и второй 4 резисторы, конденсатор 5,

D -триггер б, замыкающий контакт 7, общую шину 8, щину 9 источника питания.

В каждом канале подвижный контакт замййатощего контакта 7 соединен с общей UJHHOH 8, информационный вход 0 -триггера 6 через резистор 3 подключен к щине 9 источника питания, а выходы - к соответствующим входам блока 1 приема информации. Синхронизирующие входы О -трйггеров 6 объединены и подключе 1Ы к выходу генератора 2 тактовых импульсов. В каждом канале неподвижный контакт замыкающего контакта 7 через резистор 4 соединен с ииформационным входом Dt-триггера 6 и одной из обкладок конденсатора 5, вторая обкладка которого подключена к общей шине 8.

Работает устройство подавления дребезга следующим образом.

Пусть замыкающий контакт 7 замкнут. Тогда через резистор 4 на информационный вход D -триггера 6 подается напряжение логического нуля и D.(.-триггер 6 постоянно находится в нулевом состоянии; Которое все время подтверждается тактовыми импульcaм. При размыкании замыкающего контакта 7 возникает дребезг. Передний фронт тактового импульса генератора 2, разрешающий по входу с йхрбййзаЩи ЗаТТйеь информации в D -триггере б, либо не попадает, либо Попадает в зону дребезга, но только один раз, так как период тактовых импульсов генератора 2 выбирается больше максимального времени дребезга.

Если передний фронт тактового импульса совпадает с логическим нулем одного из ийпульсов дребезга, Dt-триггер 6 сохранйёт свое состояние в данный момент и переклточается в единичное состояние уже после окончания дребезга положительным фронтом следующего тактового импулЬса. Если же передний фронт тактового импульса совпадает с логической единицей одного из им-ч- Г - .

..-..vX „.„.„

пульсов Дребезга, то он переключается в единичное состояние во время дребезга и последующими тактовыми импульсами генератора 2 это состояние будет подтверждаться. Резистор 3 формирует уровень логической единицы на информационном входе D -триггера 6, повышая его помехозащищенность при разомкнутых замыкающих контактах 7. Резистор 4 и конденсатор 5 образуют интегрнрующую цепь и предназначены для подавления импульсных помех, наводимых на входные линии связи и коммутирующие элементы. Блок 1 осуществляет прием и обработку сигналов с выхода D -триггеров б.

Формула изобретения

Устройство подавления дребезга, содержащее блок приема информации и генератор тактовых импульсов, а также в каждом канале два резистора, конденсатор, О -триг гер и замыкающий контакт, подвижный контакт которого соединен с общей шиной, причем информационный вход 1 -триггера через первый резистор подключен к щине источника питания, а выходы - К соответствующим входам блока приема информации, отличающееся 7&Ы, что, с целью Повышения надежности, синхронизирующие входы Е триггеров объединены и подключены к выходу генератора тактовых импульсов, при этой в каждом канале неподвижный контакт замыкающего контакта через второй резис тор соединен с икформаТ щонным входом 1 триггера и одной из обкладок конденсатора, вторая обкладка которого подключена к общей ишне.

Источники информации,

принятые во внимание при экспертизе

2- Патент ФРГ № 1241486, кл. 21 а 36/18 04.03.70 (прототип).

спь

7 о

S

11

Авторы

Даты

1979-12-30—Публикация

1978-06-26—Подача