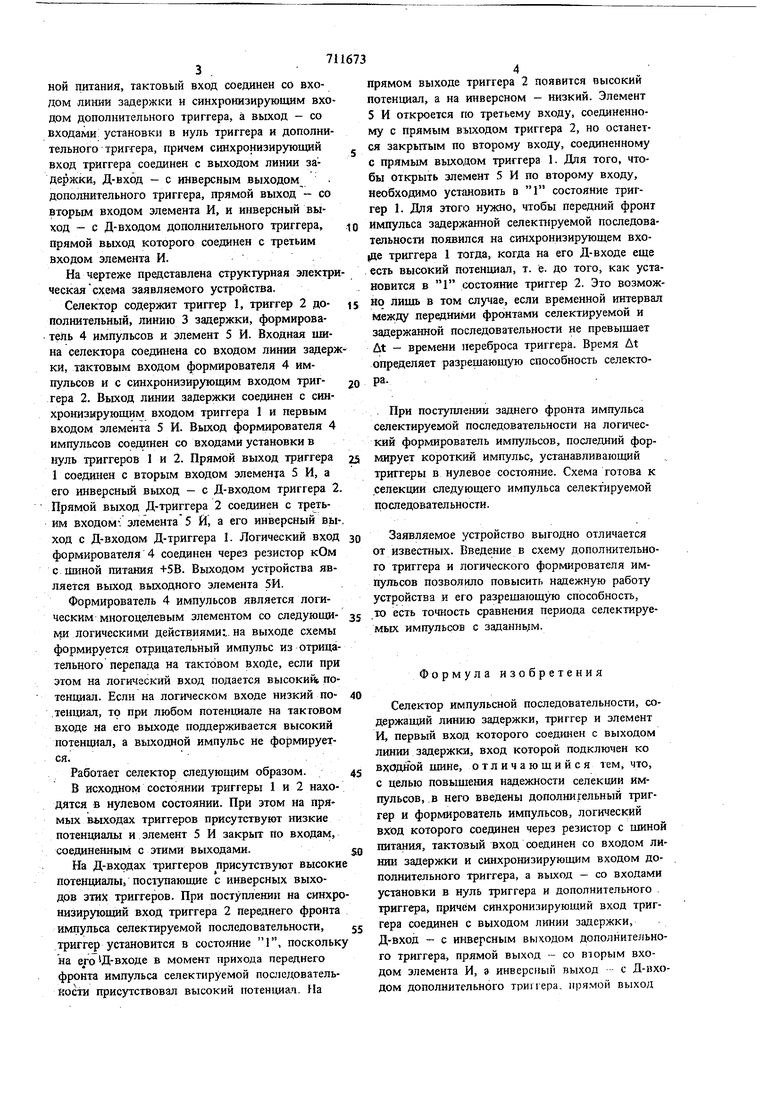

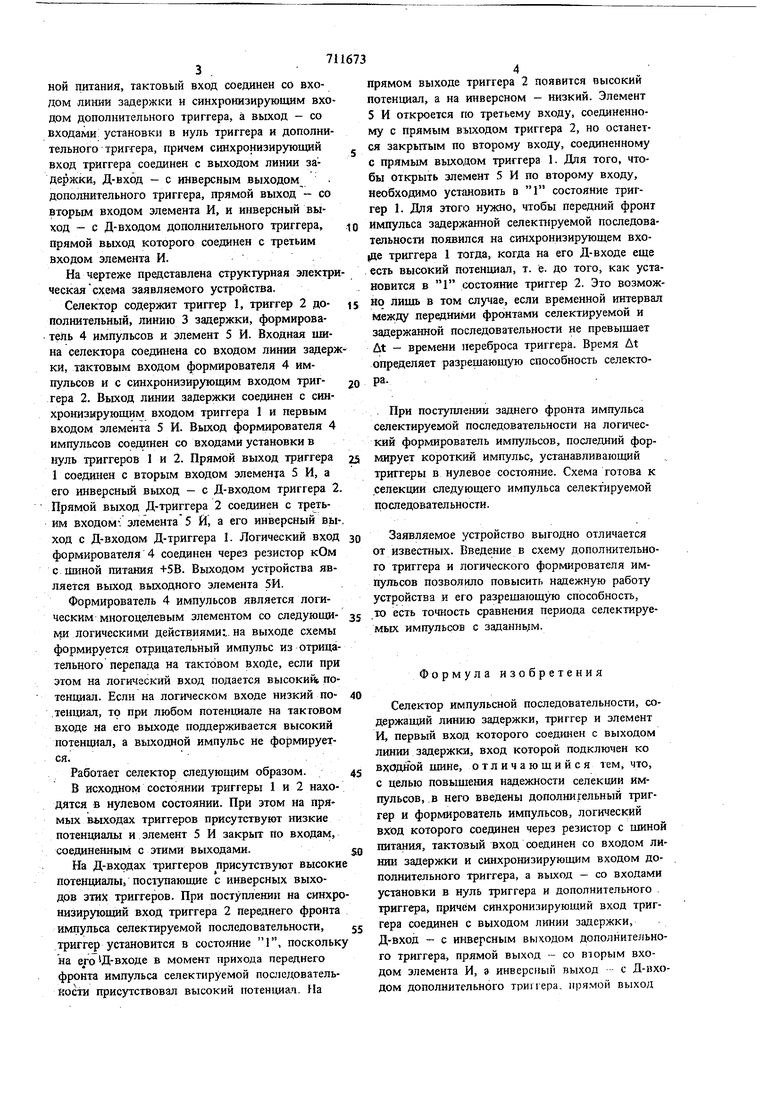

Изобретение, относится к импульсной технике и может быть использовано в цифровых системах связи. Известнь селекторы импульсной поотедоватепьности, выделяющие импульсы с определенной частотой следования. Известно устройство для, селекции . импульсов, представляющее собой детектор длительнос ти сигналов, где селекция импульсов с периодом, равным заданному, осуществляется с помощью квантованных сигналов 1. Наличие генератора квантованного сигнала усложняет сх му и, кроме того, устройство обладает определенной схелюой задержкой, которую в принципе устранить невозможно при данном построении схемы. Из известных устройств данного типа наиболее близким по техшиеской сущности является селектор импульсной последовательности, содержащий линию задержки, триггер и элемент И, один из входов которого подсоединен к вы ходу лгаош задержки, а селектируемая последовательность импульсов подается на вход линии задержки 2. Недостатком селектора является то, что при появлении импульсов на R-входе триггера, на выходе последнего устанавливается потенциал логического нуля, который закрывает схему совпадения и запрещает прохождение задержанных импульсов на выход устройства. Это обстоятельство сильно снижает надежность работы устройства. Кроме того, в устройстве отсутствует элемент, который бы устанавливал точность сравнения периодов селектируемых импульсов с заданным, т. е. элемент, который определяет разрешающую способность такого селектора импульсной последовательности. Целью настоящего изобретения является повышение надежности селекции импульсов. Поставленная цель достигается тем, что в селектор импульсной последовательности, содержащий линию задержки, триггер,и элемент И, первый вход которого соединен с выходом линии задержки, вход которой подключен ко входной шине, введены дополнительный триггер и формирователь импульсов, логический вход которого соединен через резистор с ши НОИ питания, тактовый вход соединен со входом линии задержки и синхронизирующим входом дополнительного триггера, а выход - со входа йи установки в нуль триггера и дополнительного триггера, причем синхронизирующий вход триггера соединен с выходом линии задержки, Д-вход - с инверсным выходом . дополнительного триггера, прямой выход - со Вторым входом элемента И, и инверсный выход - с Д-входом дополнительного триггера, прямой выход которого соединен с третьим входом элемента И. На чертеже представлена структурная элехтрк ческая сх;ема заявляемого устройства. Селектор содержит триггер 1, триггер 2 дополнительный, линию 3 задержки, формирователь 4 импульсов и элемент 5 И. Входная шина селектора соединена со входом линии задерж ки, тактовым входом формирователя 4 импульсов и с синхронизирующем входом триггера 2. Выход линии задержки соединен с синхронизирующим входом триггера 1 и первым входом элемента 5 И. Выход формирователя 4 импульсов со входами установки в нуль триггеров 1 и 2. Прямой выход триггера 1 соединен с вторым входом элемента 5 И, а его инверсный выход - с Д-входом триггера 2 Прямой выход Д-триггера 2 соединен с третьим входом- элемента 5 И, а его инверсный вь1 ход с Д-входом Д-триггера 1. Логический вход формирователя 4 соединен через резистор кОм с шиной питания +58. Выходом устройства является выход выходного элемента 5И. Формирователь 4 импульсов является логическим многоцелевым элементом со следующими логическими действиями:,, на выходе схемы формируется отрицательный импульс из отрицательного перепада на тактовом входе, если при этом на логический вход подается высоки потенциал. Если на логическом входе низкий по.тенциал, то при любом потенциале на тактовом входе на его выходе поддерживается высокий потенциал, а выходной импульс не формируется. Работает селектор следующим образом. В исходном состоянии триггеры 1 и 2 находятся в нулевом состоянии. При этом на прямых выходах триггеров присутствуют низкие потенадалы и элемент 5 И закрьгг lio входам, соединенным с этими выходами. На Д-вхрдах триггеров присутствуют высоки потенциалы, поступающие с инверсных выходов этих триггеров. При поступлении на синхро низирующий вход триггера 2 переднего фронта импульса селектируемой последовательности, триггер установится в состояние 1, поскольку на егО Д-входе в момент прихода переднего фронта импульса селектируемой поачедователькости присз ствовал высокий потенциат. На прямом выходе триггера 2 появится высокий потенциал, а на инверсном - низкий. Элемент 5 И откроется по третьему входу, соединенному с прямым выходом триггера 2, но останется закрытым по второму входу, соединенному с прямым выходом триггера 1. Для того, чтобы открыть элемент 5 И по второму входу, необходимо устгшовить в 1 состояние триггер 1. Для этого нужно, чтобы передний фронт импульса задержанной селект1 руемой последовательности появился на синхронизирующем вхо|Де триггера 1 тогда, когда на его Д-входе еще есть высокий потенциал, т. is. до того, как установится в 1 (Х)стояние триггер 2. Это возможно лишь в том случае, если временной интервал между передними фронтами селектируемой и задержанной последовательности не превышает ut - времени переброса триггера. Время At определяет разрешающую способность селектора. . При поступлении заднего фронта импульса селектируемой последовательности на логический формирователь импульсов, последний формирует коротюж импульс, устанавливающий триггеры в нулевое состояние. Схема готова к селекции следующего импульса селектируемой последовательности. Заявляемое устройство выгодно отличается от известных. Введение в схему дополнительного триггера и логического формирователя импульсов позволило повысить надежную работу устройства и его разрешающую способность, то есть точность сравнения периода селектируемых импульсов с зaдaннь м. Формула изобретения Селектор импульсной последовательности, содержащий линию задержки, триггер и элемент И, первый вход которого соединен с выходом линии задержки, вход которой подключен ко входной шине, отличающийся тем, что, с целью повышения надежности селекции импульсов, .в него введены дополнительный триггер и формирователь импульсов, логический вход которого соединен через резистор с шиной питания, тактовый вход соединен со входом линии задержки и синхронизирующим входом дополнительного триггера, а выход - со входами установки в нуль триггера и дополнительного . триггера, причем синхронизирующий вход триггера соединен с выходом линии задержки, Д-вход - с инверсным выходом дополнительного триггера, прямой выход - со вторым входом элемента И, э инверснып выход с Д-входом дополнительного тринера. прямой выход

которого соединен с третьим входом элемента И.

Источники информащ1и, принятые во внимание при экспертизе

1.Патент Франции N 2222798, кл. Н 03 К 5/153, 1974.

2.Авторское свидетельство СССР N 491207, кл. Н 03 К 5/20, 22.06.73 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Селектор серий импульсов | 1988 |

|

SU1615875A1 |

| Селектор импульсов | 1981 |

|

SU993465A1 |

| Селектор импульсов по длительности | 1981 |

|

SU1001458A2 |

| Селектор импульсов по длительности | 1979 |

|

SU813744A1 |

| Селектор импульсов по длительности и фазе | 1978 |

|

SU725218A2 |

| Селектор импульсов по длительности | 1981 |

|

SU970670A1 |

| Селектор импульсов по длительности | 1979 |

|

SU805485A1 |

| Селектор импульсов по длительности | 1981 |

|

SU978335A1 |

| Селектор импульсной последовательности | 1990 |

|

SU1748238A1 |

| Селектор импульсных сигналов | 1980 |

|

SU875610A1 |

Авторы

Даты

1980-01-25—Публикация

1977-09-27—Подача