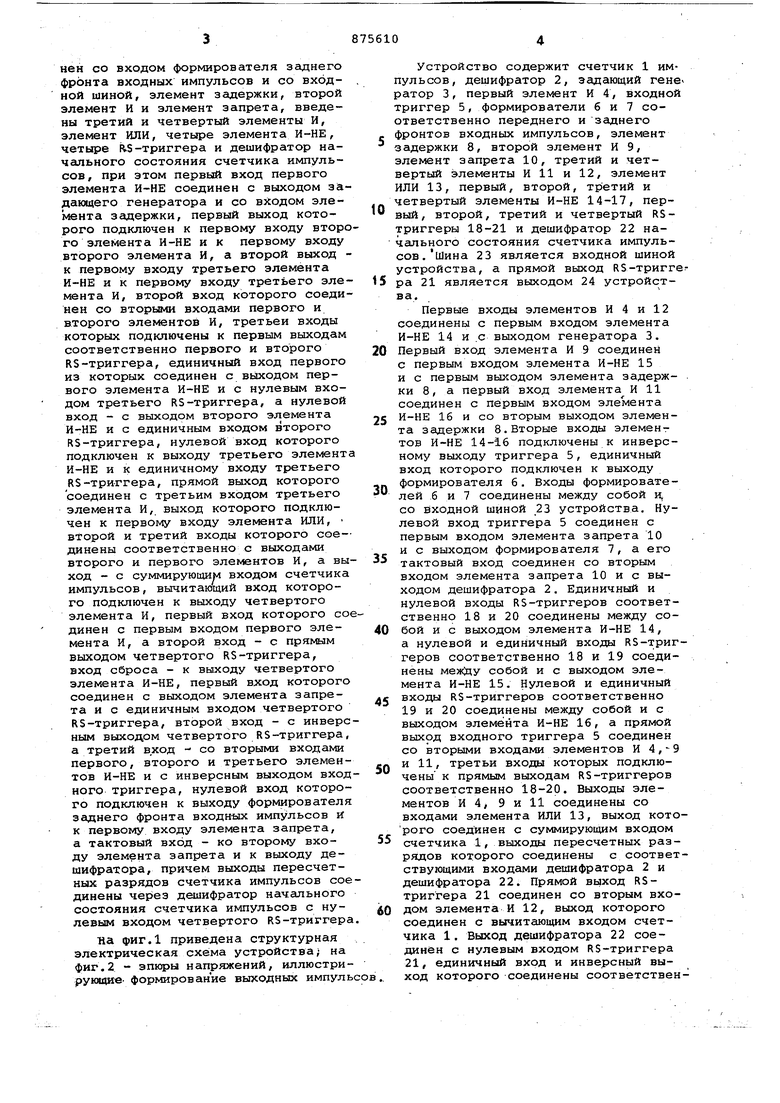

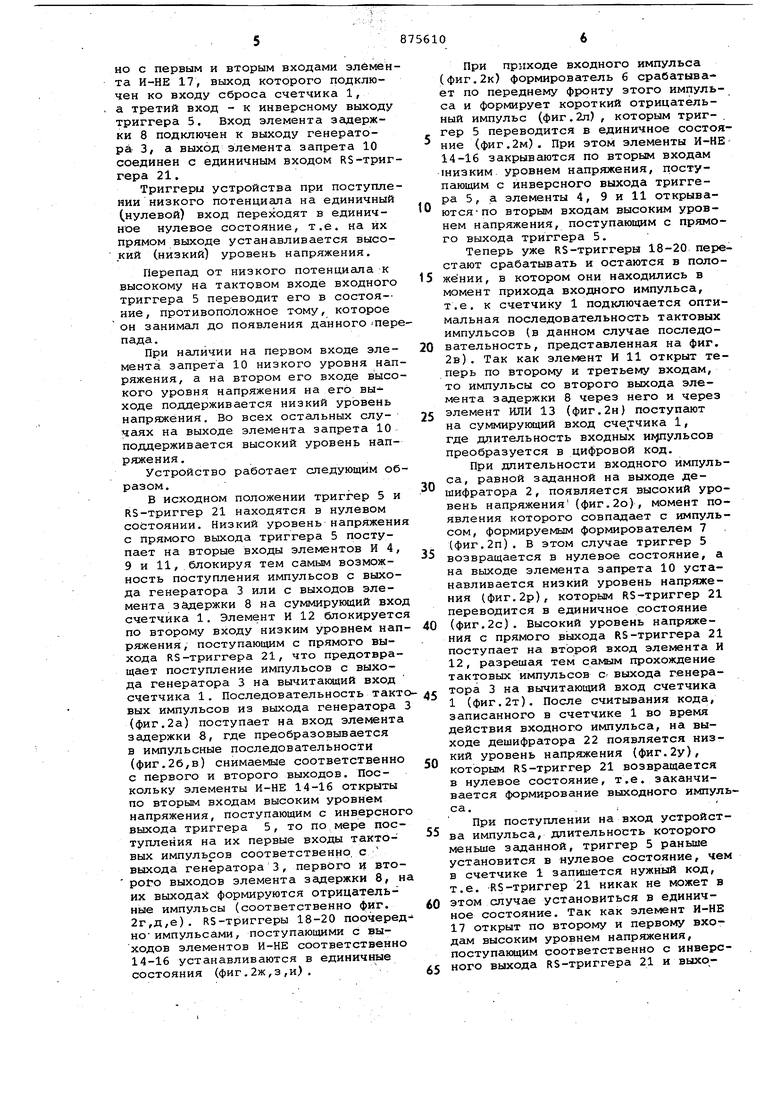

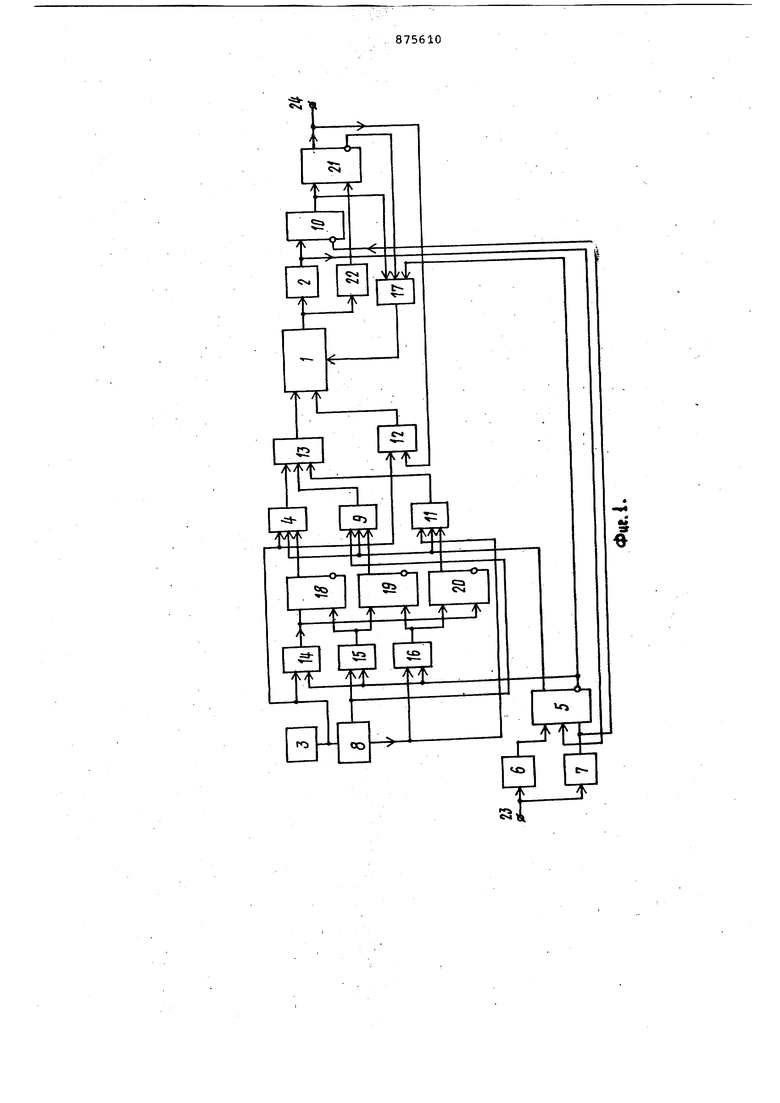

(54) СЕЛЕКТОР ИМГОЛЬСНЫХ СИГНАЛОВ Изобретение относится к импульсной технике, в частности к селекторам импульсов и может быть использо вано для вьщеления импульсов заданной длительности из последовательности импульсов с различной их длительностью. Известно устройство, содержащее ждущий мультивибратор, формирователи заднего фронта эталонного и вход ного импульсов и выходной элемент И Недостаток известного устройства низкая точность селекции. Наиболее близким по технической сущности к изобретеник является селектор импульсных сигналов, содержа щий счетчик импульсов, выходы пересчетных разрядов которого соединены с соответствующими входами дешиф ратора , задающий генератор, выход которого соединен с первым входом первого элемента И, второй вход цоторого подключён к прямому выходу входного триггера, единичный вход которого соединен с выходом формиро вателя переднего фронта входных импульсов, вход которого подключен ко входу формирователя зещнего фрон .та входных импульсов и ко входной шине, элемент задержки,второй элемент И и элемент запрета t23 . Недостаток данного устройства наличие временной ошибки, обусловленной несинхронностью входныхимпульсов с импульсами задающего генератора, что снижает точность се- лекции. Кроме того, в данном устройстве длительность выходных импульсов определяется. суммарным временем задержки сигнала в счетчике импульсов и в дешифраторе, а этого недостаточно для надежной работы последующих устройств. , Цель изобретения - повыдение точности селекции и восстановление длительности селектируемых импульсов. Цель достигается тем, что в селектор импульсных сигнсшов, содержащий счетчик импульсов, выходы пересчетных разрядов которого соединены с соответствующими входами дешифратора, задающий генератор, выход которого подключен к первому входу первого элемента И, второй вход которого соединен с прямым выходом входного триггера, единичный вход которого подключен к выходу формирователя переднего фронта вход.ных импульсов, вход которого соединен со входом формирователя заднего фронта входных импульсов и со входной шиной, элемент задержки, второй элемент И и элемент запрета, введены третий и четвертый элементы И, элемент ИЛИ, четыре элемента И-НЕ, четыре kS-триггера и дешифратор начального состояния счетчика импульсов, при этом первый вход первого элемента И-НЕ соединен с выходом за дающего генератора и со входом элемента задержки, первый выход которого подключен к первому входу втор го элемента И-НЕ и к первому входу второго элемента И, а второй выход к первому входу третьего элемента И-НЕ и к первому входу третьего эле мента И, второй вход которого соеди нен со вторыми входами первого и второго элементов И, третьей входы которых подключены к первым выходам соответственно первого и второго RS-триггера, единичный вход первого из которых соединен с викодом первого элемента И-НЕ и с нулевым входом третьего RS-триггера, а нулевой вход - с выходом второго элемента И-НЕ и с единичным входом второго RS-триггера, нулевой вход которого подключен к выходу третьего элемент И-НЕ и к единичному входу третьего RS-триггера, прямой выход которого соединен с третьим входом третьего элемента И, выход которого подключен к первому входу элемента ИЛИ, второй и третий входы которого соединены соответственно с выходами второго и первого элементов И, а вы ход - с суммирующим входом счетчика импул.ьсов, вычитающий вход которого подключен к выходу четвертого элемента И, первый вход которого со динен с первым входом первого элемента И, а второй вход - с прямым выходом четвертого RS-триггера, вход сброса - к выходу четвертого элемента И-НЕ, первый вход которого соединен с выходом элемента запрета и с единичным входом четвертого RS-триггера, второй вход - с инверс ным выходом четвертого RS-триггера а третий вход - со вторыми входами первого, второго и третьего элемен тов И-НЕ и с инверсным выходом вход ного триггера, нулевой вход которо го подключен к выходу формирователя заднего фронта входных импульсов и к первому входу элемента запрета, а тактовый вход - ко второму входу элемента запрета и к выходу дешифратора, причем выходы пересчетных разрядов счетчика импульсов сое динены через дешифратор начального состояния счетчика импульсов с нулевым входом четвертого RS-триггер На фиг.1 приведена структурная электрическая схема устройства; на фиг.2 - эпюры напряжений, иллюстри рующие- формирование выходных импул Устройство содержит счетчик 1 импульсов, дешифратор 2, задающий гене ратор 3, первый элемент И 4, входной триггер 5, формирователи б и 7 соответственно переднего и заднего фронтов входных импульсов, элемент задержки 8, второй элемент И 9, элемент запрета 10, третий и четвертый элементы И 11 и 12, элемент ИЛИ 13, первый, второй, третий и четвертый элементы И-НЕ 14-17, первый, второй, третий и четвертый RSтриггеры 18-21 и дешифратор 22 начального состояния счетчика импульсов, шина 23 является входной шиной устройства, а прямой выход RS-триггег ра 21 является выходом 24 устройства. Первые входы элементов И 4 и 12 соединены с первым входом элемента И-НЕ 14 и .с выходом генератора 3. Первый вход элемента и 9 соединен с первым входом элемента И-НЕ 15 и с первым выходом элемента задержки 8, а первый вход элемента И 11 соединен с первым входом элемента И-НЕ 16 и со вторым выходом элемента задержки 8.Вторые входы элемент тов И-НЕ 14-16 подключены к инверсному выходу триггера 5, единичный вход которого подключен к выходу формирователя 6. Входы формирователей 6 и 7 соединены между собой и со Входной шиной 23 устройства. Нулевой вход триггера 5 соединен с первым входом элемента запрета 10 и с выходом формирователя 7, а его тактовый вход соединен со вторым входом элемента запрета 10 и с выходом дешифратора 2. Единичный и нулевой входы RS-триггеров соответственно 18 и 20 соединены между собой и с выходом элемента И-НЕ 14, а нулевой и единичный входы RS-триггеров соответственно 18 и 19 соединены собой и с выходом элемента И-НЕ 15. Нулевой и единичный входы RS-триггеров соответственно 19 и 20 соединены между собой и с выходом элемента И-НЕ 16, а прямой выход входного триггера 5 соединен со вторыми входами элементов И 4, 9 и 11, третьи входы которых подключены к прямым выходам RS-триггеров соответственно 18-20. Выходы элементов И 4, 9 и 11 соединены со входами элемента ИЛИ 13, выход которого соединен с суммирующим входом счетчика 1, выходы пересчетных разрядов которого соединены с соответствующими входами дешифратора 2 и дешифратора 22. Прямой выход RSтриггера 21 соединен со вторым входом элемента И 12, выход которого соединен с вычитающим входом счетчика 1. Выход дешифратора 22 соединен с нулевым входом RS-триггера 21, единичный вход и инверсный выход которого соединены соответственно с первым и вторым входами элемента И-НЕ 17, выход которого подключен ко входу сброса счетчика 1, а третий вход - к инверсному выходу триггера 5. Вход элемента задержки 8 подключен к выходу генератора- 3, а выход элемента запрета 10 соединен с единичным входом RS-триггера 21.

Триггеры устройства при поступлении низкого потенциала на единичный (нулевой) вход переходят в единичное нулевое состояние, т.е. на их прямом выходе устанавливается высокий (низкий) уровень напряжения.

Перепад от низкого потенциала к высокому на тактовом входе входного триггера 5 переводит его в состоя-ние, противоположное тому, которое он занимсш до появления данного -перепада.

При наличии на первом входе элемента запрета 10 низкого уровня напряжения, а на втором его входе высокого уровня напряжения на его выходе поддерживается низкий уровень напряжения. Во всех остальных случаях на выходе элемента запрета 10 поддерживается высокий уровень напряжения.

Устройство работает следующим образом.

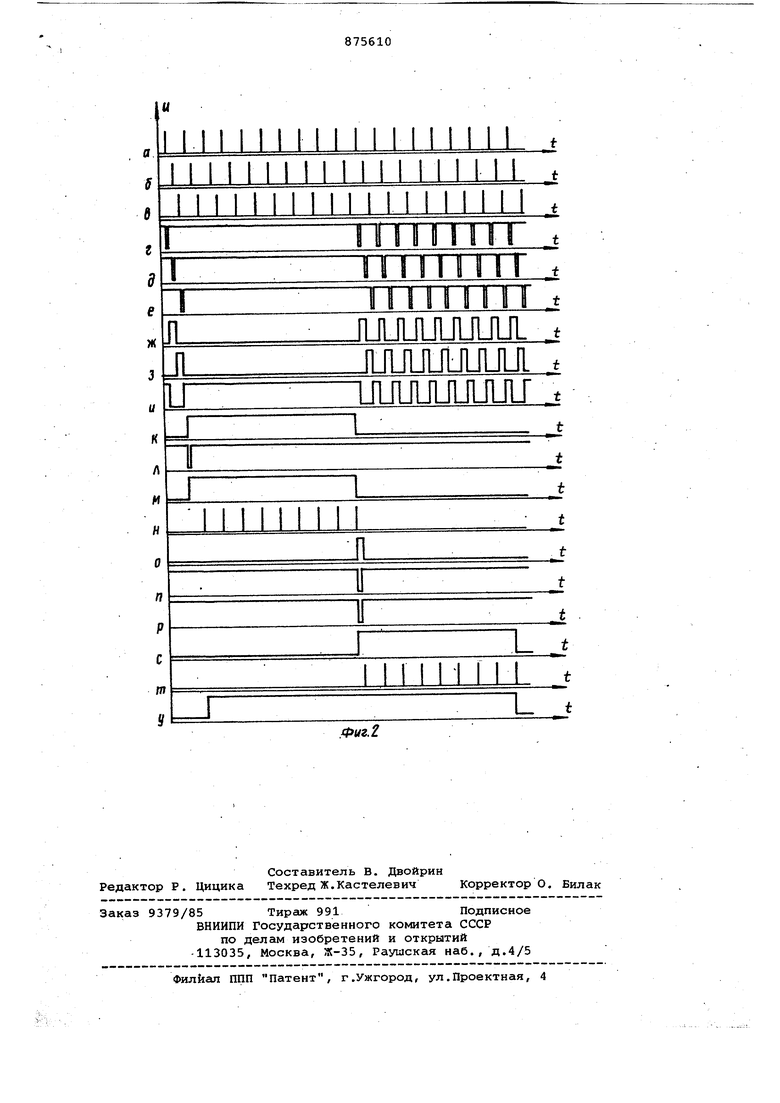

В исходном положении триггер 5 и RS-триггер 21 находятся в нулевом состоянии. Низкий уровень напряжения с прямого выхода триггера 5 поступает на вторые входы элементов И 4, 9 и 11, блокируя тем самым возможность поступления импульсов с выхода генератора 3 или с выходов элемента задержки 8 на суммирующий вход счетчика 1. Элемент И 12 блокируется по второму входу низким уровнем напряжения, поступающим с прямого выхода RS-триггера 21, что предотвращает поступление импульсов с выхода генератора 3 на вычитакадий вход счетчика 1. Последовательность тактовых импульсов из выхода генератора 3 (фиг.2а) поступает на вход элемента задержки 8, где преобразовывается в импульсные последовательности (фиг.26,в) снимаемые соответственно с первого и второго выходов. Поскольку элементы И-НЕ 14-16 открыты по вторым входам высоким уровнем напряжения, поступающим с инверсного выхода триггера 5, то по мере поступления на их первые входы тактовых импульсов соответственно, с выхода генератора3, первого и второго выходов элемента задержки 8, на их выходаз4 формируются отрицательные импульсы (соответственно фиг. 2г,д,е). RS-триггеры 18-20 поочередно импульсами, поступающими с выходов элементов И-НЕ соответственно 14-16 устанавливаются в единичные состояния (фиг.2ж,з,и).

При пряходе входного импульса (фиг.2к) формирователь 6 срабатывает по переднему фронту этого импульса и формирует короткий отрицательный импульс (фиг.2л), которым триггер 5 переводится в единичное состояние (фиг.2м). При этом элементы И-НЕ 14-16 закрываются по вторым входам 1НИЗКИМ. уровнем напряжения, поступающим с инверсного выхода триггера 5 , а элементы 4, 9 и 11 открываoются- по вторым входам высоким уровнем напряжения, поступающим с прямого выхода триггера 5.

Теперь уже RS-триггеры 18-20 перестают срабатывать и остаются в поло5жении , в котором они находились в момент прихода входного импульса, т.е. к счетчику 1 подключается оптимальная последовательность тактовых импульсов (в данном случае последовательность, представленная на фиг. 2в). Так как элемент И 11 открыт теперь по второму и третьему входам, то импульсы со второго выхода элемента задержки 8 через него и через элемент ИЛИ 13 (фиг.2н) поступгиот

5 на суммирующий вход счетчика 1, где длительность входных иг ульсов преобразуется в цифровой код.

При длительности входного импульса, равной заданной на выходе де0шифраторд 2, появляется высокий уровень напряжения (фиг.2о), момент появления которого совпадает с импульсом, формируемым формирователем 7 (фиг.2п). в этом случае триггер 5

5 возвращается в нулевое состояние, а на выходе элемента запрета 10 устанавливается низкий уровень напряжения (фиг.2р), которым RS-триггер 21 переводится в единичное состояние (фиг.2с). Высокий уровень напряже0ния с прямого выхода RS-триггера 21 поступает на второй вход элемента И 12, разрешая тем самым прохождение тактовых импульсов с. выхода генератора 3 на вычитающий вход счетчика

5 1 (фиг.2т). После считывания кода, записанного в счетчике 1 во время действия входного импульса, на выходе дешифратора 22 появляется низкий уровень напряжения (фиг.2у),

0 которым RS-триггер 21 возвращается в нулевое состояние, т.е. заканчивается формирование выходного импульса., :

При поступлении на вход устройст5ва импульса, длительность которого меньше заданной, триггер 5 раньше установится в нулевое состояние, чем в счетчике 1 запишется нужный код, т.е. RS-триггер 21 никак не может в этом случае установиться в единич0ное состояние, так как элемент И-НЕ 17 открыт по второму и первому входам высоким уровнем напряжения, поступающим соответственно с инверсного выхода RS-триггера 21 и выхода элемента запрета 10, то после возвращения триггера 5 в исходное состояние по заднему фронту входного импульса он откроется и по третьему входу. Это вызовет появление на его выходе низкого уровня напряжения, jcoTopHM счетчик 1 возвратится .в начальное состояние.

При поступлении на вход устройст ва импульса, длительность которого больше заданной, RS-триггер 21 не может установиться в единичное состояние, так как момент появления импульса на выходе дешифратора 2 не совпеодает во времени с выходным импульсом формирователя 7. В этом случае импульс с выхода дешифратора 2 поступает на тактовый вход триггера 5, и последний переводится в нулевое состояние, блокируя тем самым (сшьнейшее прохождение тактовых импульсов на суммирующий вход счетчика 1. После возвращения триггера в нулевое состояние счетчик 1, как в предыдущем случае, возвращается в начёшьное состояние.

Введение элементов И-НЕ 14-16, RS-триггеров 18-20, элемента И 11 и элемента ИЛИ 13 позволяет скомпенсировать временную ошибку, обусловленную несинхронностью входных импульсов с импульсами генератора 3.

Введение RS-триггера 21, элемента И 12, элемента И-НЕ 17 и дешифратора 22 позволяет восстанавливать длительность селектируемых импульсов .

Формула изобретения

Селектор импульсных сигналов, содержащий счетчик импульсов, выходы пересчетных разрядов которого соединены с соответствующими входами дешифратора, задающий генератор, выход которого подключен к первому входу первого элемента И, второй вход которого соединен с прямым выходом входного триггера, единичный вход которого подключен к выходу формирователя переднего фронта входных импульсов, вход которого соединен со входом формирователя заднего фронта входных импульсов и со входной шиной, элемент задержки, втрой элемент И и элелюнт запрета, отличающий ся тем, что с :цельюI повьшения точности селекции и восстановления длительности селектируемых импульсов, в него введены третий и четвертый элементы И, элемент ИЛИ, четыре элемента И-НЕ, чеяыре RS-триггера и дешифратор начального состояния счетчика импульсов, при этом первый вход первого элемента И-НЕ соединен с выходом задающего генератора и со входом элемента задержки, первый выход которого подключен к первому входу второго элемента И-НЕ и к первому входу второго элемента И, а второй выход - к первому входу третьего элемента И-НЕ и к первому входу третьего элемента И, второй вход которого соединен со вторыми входами первого и второго элементов И, третьи входы которых подключены к первым выхода л соответственно первого и второго RS-триггера, единичный вход первого из которых соединен с выходом первого элемента И-НЕ и с нулевым входом третьего RS-триггера, а нулевой вход - с выходом второго элемента И-НЕ и с единич-. ным входом второго RS-триггера, нулевой вход которого подключен к выходу третьего элемента И-НЕ и к единичному входу третьего RS-триггера, пpяfv oй выход которого соединён с третьим входом третьего элемента И, выход которого подключен к первому входу элемента ИЛИ, второй и третий входы которого соединены соответственно с выходами второго и первого элементов И, а выход - с суммирующим входом счетчика импульсов , вычитающий вход которого подключен к выходу четвертого элемента И , первый вход которого соединен с первым входом первого элемента И, а второй вход - с прямым вы ходом четвертого RS-триггера, вход сброса - к выходу четвертого элемента И-НЕ, первый вход которого соединен с выходом элемента запрета и с единичным входом четвертого RSтриггера, второй вход - с инверсным выходом четвертого RS-триггера, а третий вход - со вторыми входами первого, второго и третьего элементов И-НЕ и с инверсным выходом входного триггера, нулевой вход которого подключен к выходу формирователя заднего фронта входных имг ульсов и к первому входу элемента запрета, а тактовый вход - ко второму входу элемента запрета и к выходу дешифратора, причем выходы пересчетных разрядов счетчика импульсов соединены через дешифратор начального состояния счетчика импульсов с нулевым входом четвертого RS-триггера.

Источники информации, принятые во внимание при экспертиз

1.Ицхоки Я.с. Импульсные устройства. М., Советское радио, 1959,

с. 648.

2.Авторское свидетельство СССР 540365, кл. Н 03 К 5/18, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Селектор импульсных сигналов | 1979 |

|

SU822336A1 |

| Преобразователь последовательности временных интервалов в цифровой код | 1982 |

|

SU1070503A1 |

| Формирователь задержанных импульсов | 1984 |

|

SU1175019A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для программного управления | 1987 |

|

SU1596307A1 |

| Измеритель длительностей пачек импульсов | 1987 |

|

SU1432452A1 |

| Устройство для контроля срабатывания клавиш наборного поля | 1986 |

|

SU1432524A1 |

| Устройство фиксации переходов через нуль периодического сигнала | 1984 |

|

SU1187145A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1999 |

|

RU2173938C2 |

| Формирователь сигналов со сдвигом фазы | 1986 |

|

SU1396239A1 |

Авторы

Даты

1981-10-23—Публикация

1980-02-27—Подача