(54) СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизатор постоянного напряжения (его варианты) | 1984 |

|

SU1249498A1 |

| Стабилизатор постоянного напряжения | 1983 |

|

SU1145327A1 |

| Стабилизатор постоянного напряжения | 1980 |

|

SU922691A1 |

| Стабилизатор двухполярного напряжения | 1984 |

|

SU1201820A1 |

| Стабилизатор постоянного напряжения | 1977 |

|

SU658539A1 |

| Стабилизированный источник питания | 1979 |

|

SU851381A1 |

| Стабилизированный источник питания | 1981 |

|

SU1029167A1 |

| Стабилизатор постоянного напряжения | 1985 |

|

SU1325436A2 |

| Стабилизатор постоянного напряжения | 1976 |

|

SU653606A1 |

| Импульсный стабилизатор постоянного напряжения | 1976 |

|

SU636594A1 |

1

Изобретение относится к электрорадиотехнике, а именно источникам питания и может быть использовано в системах питания устройств автоматики и вычислительной техники.

Известны стабилизаторы постоянного напряжения, содержащие регулирующий транзистор, резисторный делитель, усилитель сиг нала рассогласования, источник опорного напряженияС1.

Наиболее близким по технической сущности к изобретению является стабилизатор постоянного напряжения , содержащий включенный последовательно в выходную щину регулирующий транзистор, эмиттером подсоединенный к выходному выводу, параллельно выходным выводам подсоединен резисторный делитель, усилитель сигнала рассогласования, к одному из входных выводов которого подсоединен источник опорного напряжения 2.

Недостатком этсго стабилизатора являет ся то, что он имеет больщое время установления переходного гфоцесса при измерении опорного напряжения.

Целью изобретения является улучшение динамических характеристик.

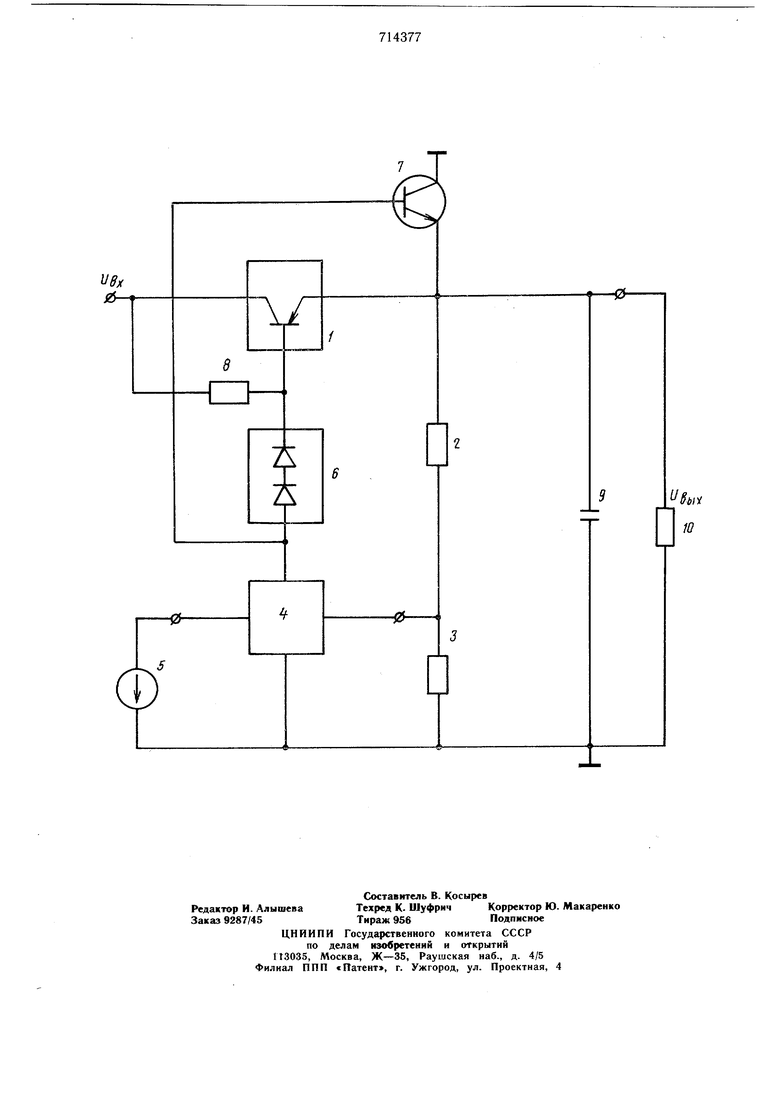

Это достигается тем, что в стабилизаторе постоянного напряжения, содержанием включенные последовательно в выходную шину регулирующий транзистор, эмиттером подсоединенный к выходному выводу, параллельно выходным выводам пОлТ,соединен резисторный делитель, усилитель сигнала рассогласования, к одному из выходных выводов которого подсоединен источник опорного напряжения, причем база регулирующего транзистора подсоединена к обшей щине через последовательно соедине шые введенный двухполюсник и упомянутый усилитель сигнала рассогласования, к точке соединения которых базой подсоединен дополнительно введенный транзистор, эмиттером соединенный с эмиттером регулирующего транзистора, а коллектором с общей шиной.

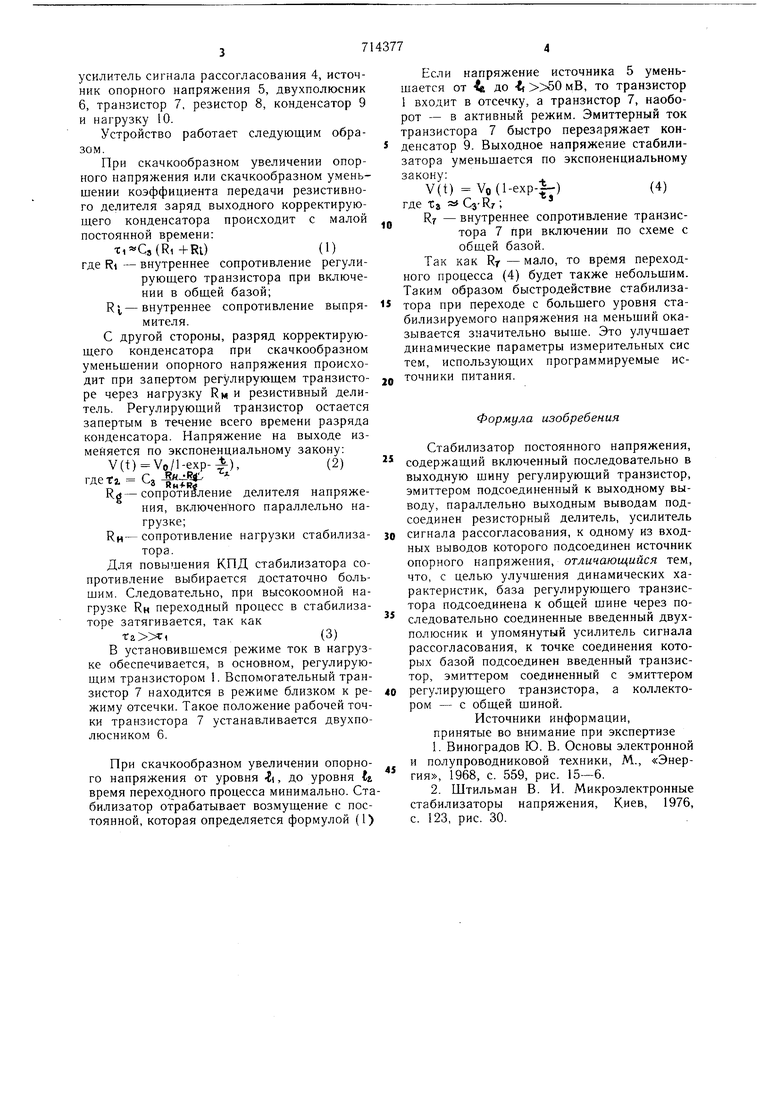

На чертеже представлена электрическая схема стабилизатора постоянного напряжения.

Стабилизатор содержит регулирующий транзистор 1, резисторный делитель 2 и 3,

усилитель сигнала рассогласования 4, источник опорного напряжения 5, двухполюсник 6, транзистор 7, резистор 8, конденсатор 9 и нагрузку 10.

Устройство работает следующим образом.

При скачкообразном увеличении опорного напряжения или скачкообразном уменьшении коэффициента передачи резистивного делителя заряд выходного корректирующего конденсатора происходит с малой постоянной времени:

T,«Cj(R,-fRi)(1)

где Ri - внутреннее сопротивление регулирующего транзистора при включении в общей базой;

RI-внутреннее сопротивление выпрямителя.

С другой стороны, разряд корректирующего конденсатора при скачкообразном уменьшении опорного напряжения происходит при запертом регулирующем транзисторе через нагрузку RM и резистивный делитель. Регулирующий транзистор остается запертым в течение всего времени разряда конденсатора. Напряжение на выходе изменяется по экспоненциальному закону:

V(t)Vo/l-exp--A),(2)

глеГо С, -5«-il l. |детг z

Kg-сопротивление делителя напряжения, включенного параллельно нагрузке;

RH- сопротивление нагрузки стабилизатора.

Для повышения КПД стабилизатора сопротивление выбирается достаточно большим. Следовательно, при высокоомной нагрузке RH переходный процесс в стабилизаторе затягивается, так как

(3)

В установившемся режиме ток в нагрузке обеспечивается, в основном, регулирующим транзистором 1. Вспомогательный транзистор 7 находится в режиме близком к режиму отсечки. Такое положение рабочей точки транзистора 7 устанавливается двухполюсником 6.

При скачкообразном увеличении опорного напряжения от уровня -Ei, до уровня ti время переходного процесса минимально. Стабилизатор отрабатывает возмущение с постоянной, которая определяется формулой (1)

Если напряжение источника 5 уменьшается от - до -If 50 мВ, то транзистор 1 входит в отсечку, а транзистор 7, наоборот - в активный режим. Эмиттерный ток транзистора 7 быстро перезаряжает конденсатор 9. Выходное напряжение стабилизатора уменьщается по экспоненциальному закону:

V(t) Vo(l-exp-|-)(4)

где ta C3-R7;

Ry - внутреннее сопротивление транзистора 7 при включении по схеме с общей базой.

Так как Rr - мало, то время переходного процесса (4) будет также небольшим. Таким образом быстродействие стабилизатора при переходе с больщего уровня стабилизируемого напряжения на меньший оказывается значительно выше. Это улучщает динамические параметры измерительных сие тем, использующих программируемые источники питания.

Формула изобребения

Стабилизатор постоянного напряжения, содержащий включенный последовательно в выходную шину регулирующий транзистор, эмиттером подсоединенный к выходному выводу, параллельно выходным выводам подсоединен резисторный делитель, усилитель 0 сигнала рассогласования, к одному из входных выводов которого подсоединен источник опорного напряжения, отличающийся тем, что, с целью улучшения динамических характеристик, база регулирующего транзистора подсоединена к общей шине через последовательно соединенные введенный двухполюсник и упомянутый усилитель сигнала рассогласования, к точке соединения которых базой подсоединен введенный транзистор, эмиттером соединенный с эмиттером 0 регулирующего транзистора, а коллектором - с общей шиной.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1980-02-05—Публикация

1978-04-24—Подача