(54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения чисел | 1981 |

|

SU960768A1 |

| Устройство для сравнения чисел | 1979 |

|

SU798817A1 |

| Устройство для сравнения двоичных чисел | 1978 |

|

SU748408A1 |

| Устройство для сравнения чисел | 1978 |

|

SU771664A1 |

| Устройство для сравнения двоичных чисел | 1979 |

|

SU877522A1 |

| Устройство для сравнения чисел | 1980 |

|

SU1003071A1 |

| Устройство для сравнения чисел | 1979 |

|

SU920701A1 |

| Устройство для сравнения чисел | 1979 |

|

SU822176A1 |

| Устройство для сравнения чисел | 1977 |

|

SU734673A1 |

| Устройство для сравнения чисел | 1977 |

|

SU620977A1 |

1

Изобретение относится к области автоматики и вычислительной техники и может бьпъ использовано в инфор1 1ационно-измерительнь1х. системах сбора и обработки информации.

Известно устройство для сравнения icdfloie чисел с некоторой допустимой погрешностыб, содержащее логические элементы ИЛИ, НЕ, входные элементы И первого и второго числа, соединенные с поразрядными элементами И-дешифратора несоответствия и с элемёнтайя И анализирующей схемы 1.

Это устройство предназначено для уменьшения избыточности информации при ее сжатии и рассчитано для работы с числами, представленными в параллельном коде. Недостатком устройства является его сложность.

Наиболее близким техническим решением к предложенному является устройство для qpa нения чисел, содержащее элементы И/И-НЕ,. И-ИЛИ/И-ИЛИ-НЕ, триггеры, причем первая входная шина соединена с первым входим первого элемента И/ИЛИ-НЕ и с первым входом первого элемента И-ИЛИ/И-ИЛИ-НЕ, вторая вх6дна1я шийа мдклйчёна кй вт-брЬму

входу первого элемента И/И-НЕ и ко второ входу первого элемента И-ИЛИ/И-ИЛИ-НЕ, третья входная шина соединена с первым входом второго элемента И/И-НЕ и. с третьим входом первого элемента И-ИЛИ/И-ИЛИНЕ, четвертая входная шшса подключена ко второму входу второго зяемента И-ИЛИ/ИИЛИ-НЕ и к четвертому входу первого элемента И-ИЛИ/И-ИЛИ-НЕ прямой выход первого элемента И/И-НЕ соединен со входом установки в единичное состояние первого триггера и с первым информациогашм входом второго триггера, инверсный выход первого элемента И/И-НЕ подключен ко входу установки в нулевое состояние третьего триггера, шшерсный выход второго элемента И/И-НЕ соединен со входом установки в нулевое состояние пёрвопз триггера , прямой выход второго элемента И/И-НЕ подключен ко входу установки в ед1пшч1гбе сястоялие третьего триггера и ко второк у информационному входу второго триггера 2,

Недостатком этого устройства является ТО; при СжатйиЛшформацик В выходном

потоке flaifflbix появляется их большая избыточность. Зто приводит к значительному уменьшению пропускной способности. системы и скорости обработки данных.

Целью изобретения является расширение функциош.г7ьньрс возмодаюстей в части обеспе чения сжатия информащщ. Это достигается тем, что устройстве прямой выход первого

элемента И-ИЛИ/И-ИЛИ-НЕ соединен .с третьим, инфсрмацйогагым входом второго триггера и с первым и вторым информадионныйй входами чётвёртого триггера, инверсный выход первого элемента И-ИЛИ подключен к третьему 1Шформациошюму входу четвертого триггера/прямой выход первого триггера соединен с первым входом второго элемента

И-ИЛИ/И-ИЛИ-НЕ, с четвертым информационным входом втърого триггера и с четвертым информационпьш входом четвертого триггера, прямой выход третьего триггера подключен Кб второму входу второго элемента И- ИЛИ/И-И ЛИ-НЕ и к Пятьм информациойным входам второго и четвертого триггеров, прямой выход второго триггера соединен; с шестым шформацибнным входом четвертого триггера, инверсный выход второго триггера подключен к третьему ичетвертому входам второго элемента И-ИЛИ/И-ИЛИ-НЕ. и к седьмому и Восьмому информацио шым входам четвертого Триггера, входы синхронизации триггеров соединены с пятой входной шиной, шестая вход-, ная шина пЬдключена к шестому, седьмому,

. и восьмому информационным входам второго триггера, седьмая входная шина сбединёна с

девятым и десятым информацйонньгми; 1вХодами четвертого триггера, прямой выход которог о подключен к вхОду iBtoporo элементй И-ИЛИ/И-ИЛИ-НЕ, шестой и седьмой входы которого подключены к восьмой 1аходной шине, а девятая Входная ЦшИа сседшёЯй )мым, девятым и десятым входами эле иента И-ИЛИ/И-ИЛИ-НЕ. .

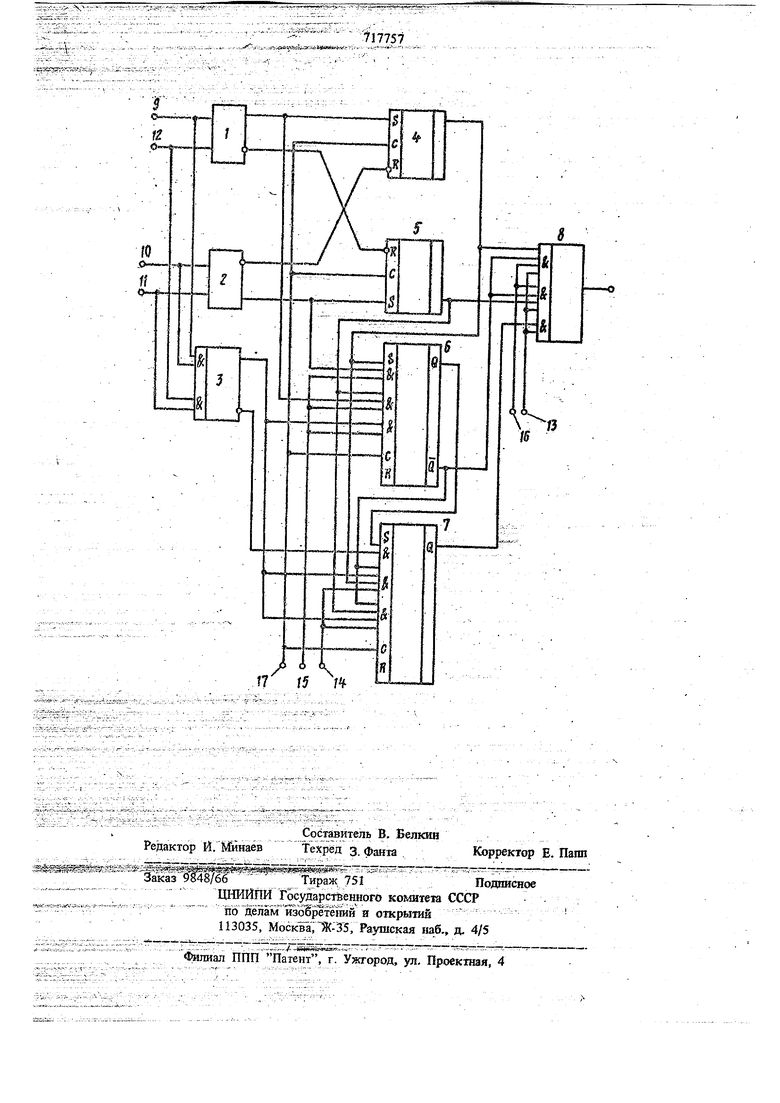

. Устройство содержит элементы 1, 2 И/И- НЕ, 3 ,И-ИЛИ/И-ИЛИ-НВ, триггеры 4, 5, 6, 7, элемент 8 И-ИЛИ/И-ИЛИ-НЁ, входные шины 9, 10 для подачи прямых значений кодов, входные шинь 11, 12 для поДачи инверсных значений кодов чисел А и В соответственно, входную шину 13 для сигнала отгрйса ре- . зультата с-равйёния, ззхоДную шину 14 цегш блокировки, входную шину 15 управления, входну1о шину 16 управления режимом работы, входную шину 17 тактовых импульсов. Работа устройства основана на использова ИМ сботношенет Между единицами и нулями двух сравниваемых шсел, отличаюшихся друг от друга на ± I. ,.

Прямьге и инверсные значения сравниваемых Чисел АЙВ синхронно в последовательном

коде, начиная с младших разрядов, поступают на входы 9, 11 и 10, 12 элементов 1, 2 , И/И-НЕ. На прямых выходах этих, элементов формируются сигналы, определяющие ненулевые разности между одноименными разрядами Ь| сравниваемых чисел Аи В. При а Ь триггер 4 по входу S после окончания действия TaKtOBoro импульса установится в единичное состояние, а триггер 5 по входу R инверсным сигналом с инверсного выхода элемента

2 И/И-НЕ послеокончания действия тактового импульса установится в нулевое состояние. При b; 3 , наоборот, в единичное состояние установится триггер 5, а в нулевое -

триггер 4. .При а- Ц- триггеры 4, 5 сохраняют свое предьщущее состояние. После окончания передачи сравниваемьк кодов триггер 4 будет находиться в единичном .состоянии, если А В, а если А В, то в единичном

состоянии будет находиться триггер 5. При равенстве чисел А и В триггеры 4, 5 будут находиться в нулевом состоянии. Триггер б анализа разрядов чисел в соответствующий момент после окончания действия Тактового

импульса усташавливается в единичное состояние, если в одном числе в т младших разрядах стоят нули, а в другом в этих же разрядах стоят единицы, причем после . группы нулей в следуюш:ем старшем разряде

стоит единица, а после гр}шпы единиц - нуль, а также, если два одноименных разряда сравниваемых чисел равны между собой.

Триггер 7 сравнения на ± 1 сохраняет нулевое состояние или состояние , если

после установки триггера б в единичное состояние последуюшие разряды сравниваемых чисел равны между собой. При других сочетаниях состояния триггера б и разрядов сравниваемых чисел триггер 7 устанавливается в

единич1юе срстояние или не равно.

Исключение составляет сочетание, когда триггер 6 находится в нулевом состоянии и все последуюшие разряды, начиная со второ.го, равньг йежду собой. В этом случае для устранения переброса триггера 7 в состояние не равно на соответствзтощие его входы через 1цину 14 цепи блокировки подается запрещающий сигнал во время, совпадающее с моментом прихода второго разряда сравниваемых

чисел.

При подаче на входную шину 16 управления режимом работы запрещающего уровня результат сравнения чисел будет справедлив для кодов, обладающих свойством цикличности, J отличающихся от обычных двоичных кодов тем, чти если одно из сравниваемых чисел представляет собой совокупность единиц, а другое - совокупность нулей, то эти числа сравнимы между собой на ±1; при подаче раз

решающего уровня на входную шину 16 результат сравнения чисел на ± 1 будет справедлив для кодов, не обладаюшях этим свойством

При сравнении обычных кодов чисел с погрешностью отличной от ±1 на вход 15 подается запрещающий сигнал, который блокирует входы триггера б анализа, разрядов чисел к моменту прихода младших, разрядов кбйЬб. В этом случае числа А и В сравниваются С погрешностью Д ±( -1), где К число определяет количество младших разрядов, не Зчаствующих в сравнении, а число а определяет точнее и допустимьге границы интервала погрешности.

Пои о: 1 чисяа А и В, удовлетворяющие условию . А-В 2, будут сравниваться устройстаом.

При а О числа А и В, удовлетворяюидае условию 21 , могут сравниваться или не сравниваться устройством в зайисимости от их положения на числовой оси.

Запрещающие сигналы на входы 14, 15 подаются в момент; Прихоф младших разрядов сравниваемых чисел и имеют дгаительности равные К+2 И К тактам соответственно.

Устройство 6cyщёctвляёт сравнение пославдовательных кодбв чисел в заданном интервале погрешностей. Это дает возможность использовать предложенное устройство в информационноизмерительных системах сбора и обработки данных, где требуется уменьшить избыточность информации путем обработки только тех измеренных значений параметров, которые бтаМайзУСЙ от предыдущих обработанных значений на величину порога. Уменьшение избыточности информации позволяет значительно увеличить пропускную способность и быстродействие информационно-измерительных систем и повысить информативность измеренных параметров.

. ...

Формула изобретения

Устройство для сравнения чисел, содержащее злементь И/И-ИЕ, И-ИЛИ/И-ИЛИ-НЕ, триггеры, причем первая входаая шина соёДйнена с первым входом первого элемента И/И-НЕ и с первым входом первого элемента И-ИЛЙ/ И-ИЛИ-НЕ, вторая входная шина подключена ко второму входу первого элемента И/Й-НЕ и ко второму входу первого элемента И-ИЛИ/ И-ИЛИ-НЕ, третья входная ишна соединена с первьш входом второго элемента И/И-НЕ и с третьим входом первого элемента И-ИЛИ/ И-ИЛИ-НЕ, четвертая входная шина подклй-;. чена ко второму входу второго элемента И/И-. НЕ и к четвертому входу первого элемента

И-ИЛИ/И-ИЛИ-НЕ, прямой выход первого элемента И/И-НЕ соединен со входом установки в единичное состояние первого тригггра и с первым информационным входом второго триггера, инверсный выход первого элемента. И/И-НЕ подключен ко входу установки в нулевое состояние третьего триггера, инверсный выход второго элемента И/И-НЕ соединен со входом установки в нулевое состояние первого триггера, прямой выход второго эле,мента И/И-НЕ подключен ко входу установки в единшшое состояние третьего триггера и ко второму информационному входу второго триг гера, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения сжатия информации в устройстве прямой выход первого элемента И-ИЛИ/И-ИЛИ-НЕ соединен с третьим информационным входом второго триггера и с первым и вторым информационны ш входами четвертого триггера, инверсный выход .первого элемента И-ИЛИ/И-ИЛИ-НЕ подключен к

третьему информационному входу четвертого триггера, прямой выход первого триггера соединен с первым входом второго элемента

. Й-ЙЛИ/И-ИЛИ-НЕ, с, четвертым информационi ным входом второго триггера и с четверть1М информационным входом четвертого триггера, прямой выход третьего триггера подключен ко второму входу второго элемента И-ИЛИ/ И-ИЛИ-НЕ и к пятым информационным входам второго и четвертого триггеров, 1фямой выход второго триггера соедгшен с iiiecTbiM информационным входом четвертого триггера, инверсный выход второго триггера подключен к третьему и четвертому входам второго элемента И-ИЛИ/И-ИШ -НЕ и к седьмому и восьмому информационным входам четвертого триггера, входи сгахронизации триггеров соединены с пятой входной шиной, шестая входная шина .подключена к шестому, седьмому и восьйьму информацио1шым. входам второго триггера, седьмая входная шина соединена с девятым и десятым информационными входами четвертого триггера, прямой выход кдтЬрого.подключен к пятому вхЬДу второго элемента И-ИЛИ/И-ИЛИ-НЕ, шестой и седьмой входы которого подключетгы к восьмой входной шнне, а девятая входная шина соедшена с восьмым, девятым н десятым входами элемента ;И-ИЛИ/И-Р1ЛИ-11Е; ИстСочники информации, принятые во внимание при экспертизе

Авторы

Даты

1980-02-25—Публикация

1977-09-05—Подача