(54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения чисел | 1977 |

|

SU717757A1 |

| Устройство для сравнения чисел | 1977 |

|

SU620977A1 |

| Устройство для сортировки чисел | 1983 |

|

SU1113797A2 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА РАЗМАХОВ КОЛЕБАНИЙ НАПРЯЖЕНИЯ | 1993 |

|

RU2075752C1 |

| СПОСОБ И УСТРОЙСТВО СЧЕТА ИМПУЛЬСОВ | 2015 |

|

RU2604334C2 |

| Устройство для сравнения чисел | 1987 |

|

SU1439573A2 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1228290A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Демодулятор сигналов с минимальной частотной манипуляцией | 1985 |

|

SU1261136A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в информационно-измерительных системах и устройствах дискретной автоматики.

Известно устройство для сравнения, содержащее элементы И, ИЛИ, НЕ, триггеры, подключенные к выходным элементам И, ИЛИ, счетчик, каждый разряд которого через тумблерну линеШсу подключен к выходному элеNieHTyИ и ко. входу соответствующего элемента НЕ. Это устройство предназначено для сравнения чисел на больше, меньше и равно ij

Недостатком данного устройства является невозможность проведения сравнения кодов чисел с некоторой допустимой погрешностью.

Наиболее близким по техническому решению к предлагаемому является устройство для сравнения чисел,используемое в информационно-измерительных системах для сжатия входного потока данных и содержащее элементы И/И-НЕ, триггеры, причем прямые выходы первого и второго элементов И/И-НЕ соединены с первыми входами установки в единичное состояние первого и второго триггеров

соответственно, инверсные выходы первого и второго элементов И/И-НЕ подключены к-первому и второму входам установки в единичное состояние третьего триггера, входы синхронизации всех триггеров соединены со входом тактовых сигналов устройства, входы установки в нулевое состояние всех триггеров подключены

o ко входу сброса устройства, третий и четвертый.входы установки в единичное состояние третьего триггера соединены со входом задания погрешности управления устройства, прямые

5 выходы первого и второго триггеров подключены к пятому и шестому входам установки в единичное состояние соответственно третьего триггера, инверсный выход первого триггера

0 соединен со вторым входом установки в единичное состояние второго триггера, инверсный выход второго триггера подключен ко второму входу устацовки в единичное состояние первого 5 триггера И .

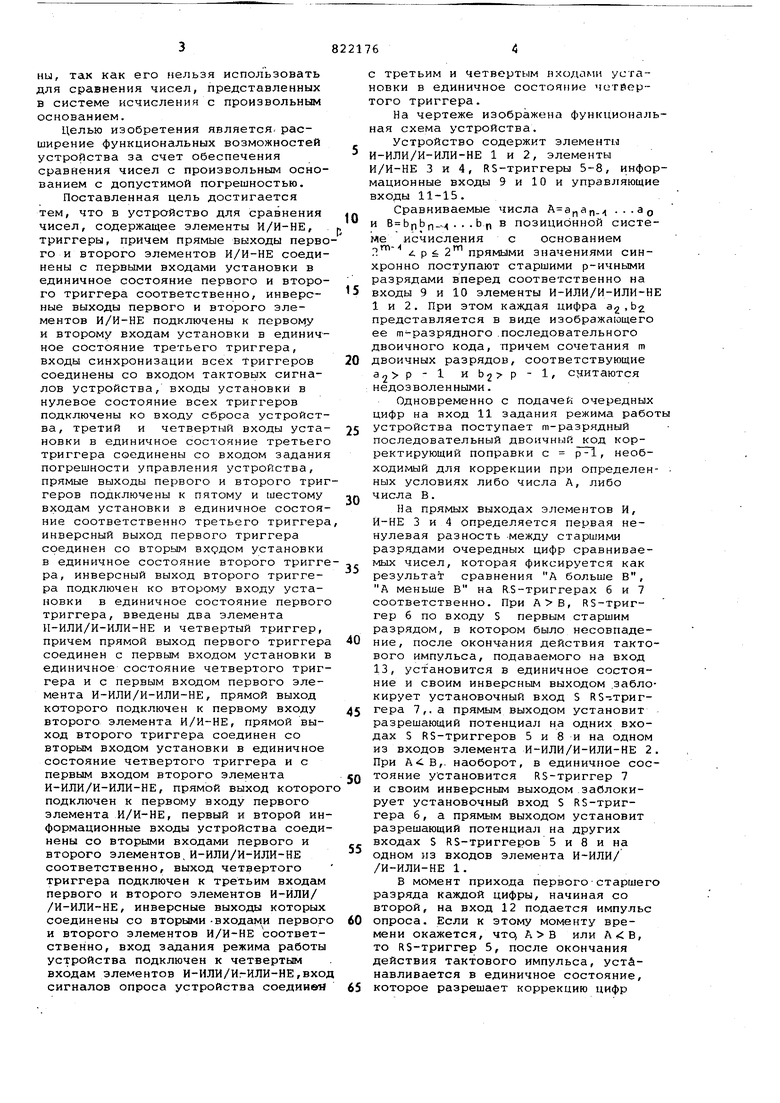

Однако в таком устройстве операция сравнения с допустимой погрешностью выполняется только над двоичными числами, поэтому функциональ0ные возможности устройства эграничвни, так как его нельзя использовать для сравнения чисел, представленных в системе исчисления с произвольным основанием. Целью изобретения является.расширение функциональных возможностей устройства за счет обеспечения сравнения чисел с произвольным основанием с допустимой погрешностью. Поставленная цель достигается тем, что в устройство для сравнения чисел, содержащее элементы И/И-НЕ, триггеры, причем прямые выходы перво го и второго элементов И/И-НЕ соединены с первыми входами установки в единичное состояние первого и второго триггера соответственно, инверсные выходы первого и второго элементов И/И-НЕ подключены к первом у и второму входам установки в единичное состояние третьего триггера, входы синхронизации всех Триггеров соединены со входом тактовых сигналов устройства, входы установки в нулевое состояние всех триггеров подключены ко входу сброса устройства, третий и четвертый входы уста новки в единичное состояние третьего триггера соединены со входом задания погрешности управления устройства, прямые выходы первого и второго три геров подключены к пятому и шестому входам установки в единичное состоя ние соответственно третьего триггер инверсный выход первого триггера соединен со вторым вхддом установки в единичное состояние второго тригг ра, инверсный выход второго триггера подключен ко второму входу установки в единичное состояние первог триггера, введены два элемента И-ИЛИ/И-ИЛИ-НЕ и четвертый триггер, причем прямой выход первого триггер соединен с первым входом установки единичное состояние четвертого триг гера и с первым входом первого элемента И-ИЛИ/И-ИЛИ-НЕ, прямой выход которого подключен к первому входу второго элемента И/И-НЕ, прямой выход второго триггера соединен со вторым входом установки в единичное состояние четвертого триггера и с первым входом второго элемента И-ИЛИ/И-ИЛИ-НЕ, прямой выход которо подключен к первому входу первого элемента И/И-НЕ, первый и второй ин формационные входы устройства соеди нены со вторыми входами первого и второго элементов, И-ИЛИ/И-ИЛИ-НЕ соответственно, выход четвертого триггера подключен к третьим входам первого и второго элементов И-ИЛИ/ /И-ИЛИ-НЕ, инверсные выходы которых соединены со вторыми -входами первог и второго элементов И/И-НЕ соответственно, вход задания режима работы устройства подключен к четвертым входам элементов И-ИЛИ/ИгИЛИ-НЕ,вхо сигналов опроса устройства соединен третьим и четвертым входами устаовки в единичное состояние четверого триггера. На чертеже изображена функциональая схема устройства. Устройство содержит элементы -ИЛИ/И-ИЛИ-НЕ 1 и 2, элементы /И-НЕ 3 и 4, RS-триггеры 5-8, инфорационные входы 9 и 10 и управляющие входы 11-15. Сравниваемые числа ,. ---ао и ., . . . b р в позиционной системе исчисления с основанием . р & 2 прямыми значениями синхронно поступают старшими р-ичными разрядами вперед соответственно на входы 9 и 10 элементы И-ИЛИ/И-ИЛИ-НЕ 1 и 2. При этом каждая цифра ag.bg представляется в виде изображающего ее т-разрядного .последовательного двоичного кода, причем сочетания m двоичных разрядов, соответствующие , считаются недозволенными. Одновременно с подачей очередных цифр на вход 11 задания режима работы устройства поступает т-разрядный последовательный двоичный код корректирующий поправки с р, необходимый для коррекции при определен- ных условиях либо числа А, либо числа В. На прямых выходах элементов И, И-НЕ 3 и 4 определяется первая ненулевая разность -между старшими разрядами очередных цифр сравниваемых чисел, которая фиксируется как результат сравнения А больше В, А меньше В на R.S-триггерах 6 и 7 соответственно. При , RS-триггер б по входу S первым старшим разрядом, в котором было несовпадение, после окончания действия тактового импульса, подаваемого на вход 13, установится в единичное состояние и своим инверсным выходом .заблокирует установочный вход S RS-триггера 7,.а прямым выходом установит разрешающий потенциал на одних входах S RS-триггеров 5 и 8 и на одном из входов элемента И-ИЛИ/И-ИЛИ-НЕ 2. При А-с в,, наоборот, в единичное состояние установится RS-триггер 7 и своим инверсным выходом заблокирует установочный вход S RS-триггера 6, а прямым выходом установит разрешающий потенциал на других входах S RS-триггеров 5 и 8 и на одном из входов элемента И-ИЛИ/ /И-ИЛИ-НЕ 1. В момент прихода первогостаршего разряда каждой цифры, начиная со второй, на вход 12 подается импульс опроса. Если к этому моменту времени окажется, 4Tq или , то RS-триггер 5, после окончания действия тактового импульса, устанавливается в единичное состояние, которое разрешает коррекцию цифр

а , а . , . ... , а о при Л В или цифр Ь ,.. Ьо при А В.

Коррекция осуществляется путем поразрядного логического сложения на элементах И-ИЛИ/И-ИЛИ-НЁ 1 и 2 соответствующих кодов цифр с кодом корректирующей поправки С. Результат сравнения чисел с погрешностью +1 определяется нулевым состоянием RS-триггера 8, переброс которого в состояние не равно осуществляется в соответствии с логическим выражением ,( А В) (. ) V ()(aVbJ), где а- , Ь - одноименные двоичные разряды кодов цифр а, Ь соответственно. Следовательно, RS-триггер 8 сохраняет состояние равно, если после фиксации результата сравнения в оставшихся (i+1)-младших двоичных разрядах числа А стоят нул и в этих же двоичных разрядах числа В с учетом их коррекции стоят единицы, и, наоборот, при А В в (i+1)-младших двоичных рязрядах числа А, с учетом их коррекции, стоят единицы и в этих же двоичных разрядах числа В - нули. Если же будет другое сочетание двоичных рязрядов, например, они будут равны друг друг а bg после фиксации результата , то RS-триггер 8 после окончания действия тактового импульса на момент Jcoвпaдeния одноименных разрядов установится в единичное состойии или не равно.

Опрос результатов сравнения производится после окончания передачи кодов соответствующих чисел, и каходой операции сравнения предшествует импульс сброса устройства, лодBaeMiifi на вход 14.

Результат сравнения чисел определяется анализом нулевых состояний RS-триггеров 6 и 7.

При сравнении чисел с погрешностьюИ на вход 15 подается разрешаю1-;ий потенциал, а при сравнении с погрешностью, отличной от ±1, на вход 15 подается запреша19Щий сигнал, который блокирует входы S RS-триггера 8 на момент анализа млаших разрядов чисел. В этом случае числа А и В сравниваются с погрешностью Д ±(2 p -1-oi) , где число k определяет количество младших цифр, не участвующих в сравнении, а число об - точные и допустимые границы интервала погрешностей. Число 06 р - 1 определяет точные границы интервала погрешностей, и все числа А и В, удовлетворяющие условию IA-B.I р , будут сравниваться устройством.

Число 06 О определяет допустимые границы интервала погрешностей, и числа-А и В, удовлетворяющие условию р |А-В| р, могут сравниваться или не сравниваться устройством в зависимости от их положения на числовой оси.

Следовательно, устройство обеспечивает сравнение чисел с произвольным основанием с допустимой погрешностью путем коррекции одного из двух 5 сравниваемых чисел, осуществляемой с учетом анализа текущих значений кодов

цифр этих чисел.

Использование предлагаемого

Q устройства для сжатия входного потока данных, представляемых в позиционной системе исчисления с произвольным основанием, например в двоично-десятичной системе, позволяет уменьшить объем необходимого оборудования при реализации аппаратными методами компараторов с управляемой точностью сравнения, а также увеличить быстродействие информационно-измерительной системы за счет

0 конвейерной организации обработки массива р-ричных данных.

Формула изобретения

25

Устройство для сравнения чисел, содержащее элементы И/И-НЕ, триггеры, причем прямые выходы первого и второго элементов И/И-НЕ соединены с -., первыми входами установки в единичное состояние первого и второго триггеров соответственно, инверсные выходы первого и второго элементов И/И-НЕ подключены к первому и второму входам установки в единичное

5 состояние третьего триггера, входы синхронизации всех триггеров соединены со входом тактовых сигналов устройства, входы установки в нулевое состояние всех триггеров подключены ко входу сброса устройства, третий и четвертый входы установки в единичное состояние третьего триггера соединены со входом задания погрешности управления устройства, j прямые выходы первого и второго триггеров подключены к пятому и шестому входам установки в единичное состояние соответственно третьего триггера, инверсный выход первого триггера соединен со вторым входом установки в единичное состояние второго триггера,инверсный выход второго триггера подключен ко второму входу установки в единичное состояние первого J триггера, отличающееся

тем, что, с целью расширения функциональных возможностей за счет обеспечения сравнения чисел с произвольным основанием с допустимой погрешностью, в него введены два элемента 0 и-ИЛИ/И-ИЛИ-НЕ и четвертый триггер, причем прямой выход первого триггера соединен с первым входом установки в единичное состояние четвертого триггера и с первым входом первого 5 элемента И-ИЛИ/И-ИЛИ-НЕ, прямой вы

Авторы

Даты

1981-04-15—Публикация

1979-07-04—Подача