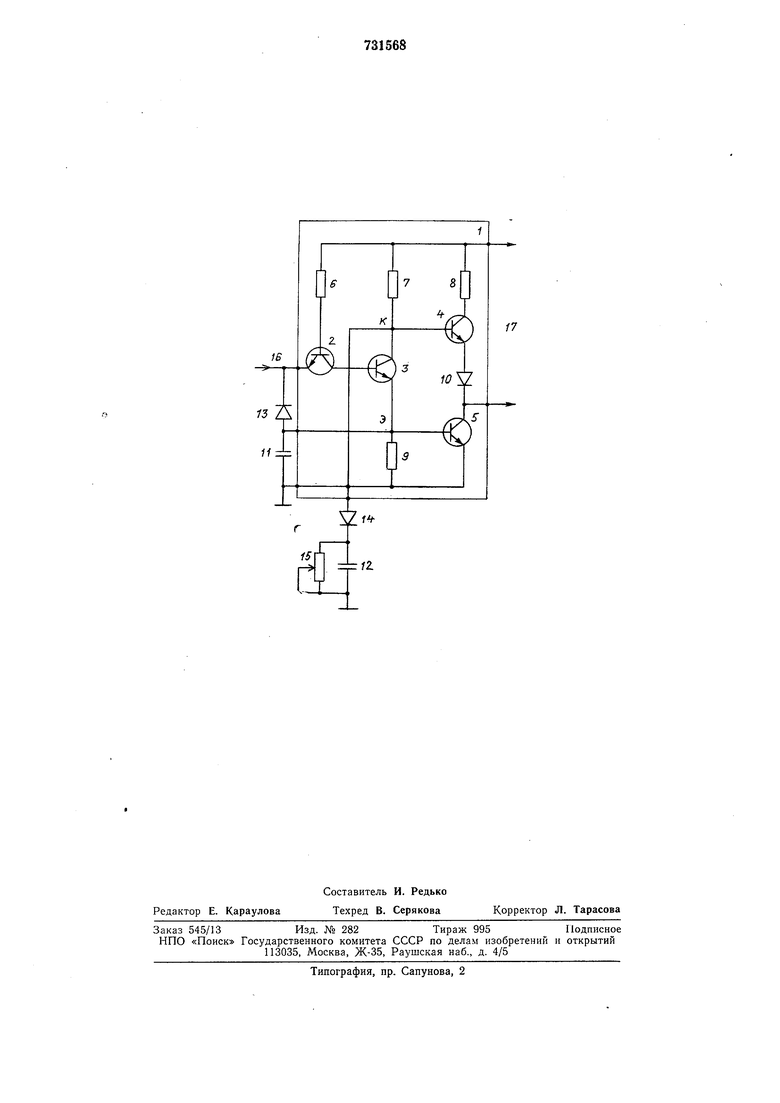

цепи соединен с коллекторным входом логического расширения элемента И-НЕ.

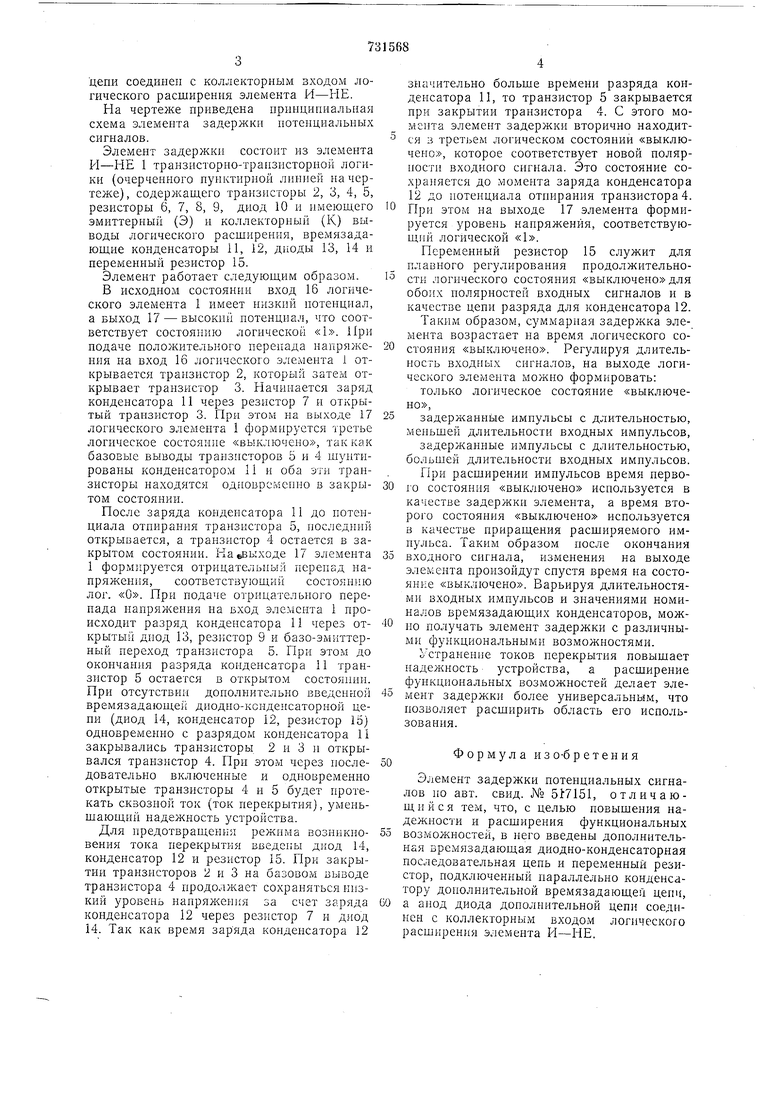

На чертеже приведена принципиальная схема элемента задержки нотеициальных сигналов.

Элемент задержки состоит из элемента И-НЕ 1 транзисторио-траизисториой логики (очерченного иуиктириой линией иачертеже), содержащего транзисторы 2, 3, 4, 5, резисторы 6, 7, 8, 9, диод 10 и имеющего эмиттерный (Э) и коллекторный (К) выводы логического расширения, времязадающие конденсаторы И, 12, диоды 13, 14 и переменный резистор 15.

Элемент работает следующим образом.

В исходном состоянии вход 16 логического элемента 1 имеет низкий иотенциал, а выход 17 - высокий иотеицнал, что соответствует состоянию логической «1. При подаче положительного иереиада нагфяжения на вход 16 логического э;1емента 1 открывается транзистор 2, который затем открывает траизистор 3. Начинается заряд конденсатора И через резистор 7 и открытый транзистор 3. При этом на выходе 17 логического элемента 1 формируется третье логическое состояние «выключеио, так как базовые выводы транзисторов 5 и 4 шуитированы конденсатором И и оба эти транзисторы находятся одновременно в закрытом состоянии.

После заряда конденсатора И до потенциала отиирания транзистора 5, иоследиий открывается, а транзистор 4 остается в закрытом состоянии. На «выходе 17 элемента 1 формируется отрицательиый иереиад напряжения, соответствующий состоянию лог. «О. При подаче отрицательного перепада напряжения на вход элемента 1 происходит разряд конденсатора И через открытый диод 13, резистор 9 и базо-эмиттерный переход транзистора 5. При этом до окончания разряда коидеисатора 11 транзистор 5 остается в открытом состоянии. Прн отсутствии дополнительно введенной времязадающей диодно-ксидеысаторной цени (диод 14, конденсатор 12, резистор 15) одновременно с разрядом конденсатора И закрывались транзисторы 2 и 3 и открывался транзистор 4. При этом через последовательно включенные и одновременно открытые транзисторы 4 и 5 будет протекать сквозной ток (ток перекрытия), умеиьшающий надежность устройства.

Для иредотвращения режима возникиовения тока перекрытия вседепы диод 14, конденсатор 12 и резистор 15. При закрытии транзисторов 2 и 3 на базовом выводе транзистора 4 продолжает сохраняться низкий уровень напряжения за счет заряда конденсатора 12 через резистор 7 и диод 14. Так как время заряда коиденсатора 12

значительно больше времени разряда кондеисатора И, то транзистор 5 закрывается при закрытии транзнстора 4. С этого момента элемент задержки вторично находится 3 третьем логическом состоянии «выключено, которое соответствует новой поляр юстн входного сигнала. Это состояние сохраняется до момента заряда конденсатора 12 до иотенциала отиирания транзистора 4. При этом на выходе 17 элемента формируется уровень нанряженйя, соответствующий логической «1.

Переменный резистор 15 служит для илавного регулирования продолжительности логического состояиия «выключено для обоих полярностей входных сигналов и в качестве цепи разряда для конденсатора 12.

Таким образом, суммарная задержка элемента возрастает на время логического состояния «выключено. Регулируя длительиость входных сигиалоБ, на выходе логического элемента можно формировать:

только логическое состояние «выключено,

задержанные импульсы с длительностью, меньшей длительности входных импульсов,

задержанные импульсы с длительностью, большей длительности входных импульсов.

При расширении импульсов время первого состояния «выключено используется в качестве задержки элемента, а время второго состояния «выключено нспользуется в качестве нриращения расширяемого импульса. Таким образом после окончания входного сигнала, изменения на выходе элемента произойдут спустя время на состояние «выключено. Варьируя длительностями входных импульсов и значениямп номиналов времязадающих конденсаторов, можно иолучать элемент задержки с различными функциональными возможностями.

Устранение токов иерекрытия повышает надежность устройства, а расширение фуикщюнальных возможностей делает элемент задержки более универсальным, что нозволяет расширить область его использования.

Формула пзо-бретения

Элемент задержки потенциальных сигналов но авт. свид. № 517151, отличаюШ и и с я тем, что, с целью повышения надежности и расширения функциональных возможностей, в него введены донолнительная времязадающая диодно-конденсаторная последовательная цепь и переменный резистор, подключенный нараллельно конденсатору дополнительной времязадающей цени, а анод диода дополнительной цепи соединен с коллекторным входом логического расширения элемента PI-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1971 |

|

SU321926A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ | 1967 |

|

SU202216A1 |

| Одновибратор | 1978 |

|

SU733088A1 |

| Генератор задержанных импульсов | 1990 |

|

SU1750037A1 |

| Устройство задержки | 1976 |

|

SU650223A1 |

| ОДНОВИБРАТОР | 1972 |

|

SU345598A1 |

| Ждущий мультивибратор | 1974 |

|

SU514417A1 |

| Генератор импульсных сигналов | 1978 |

|

SU780165A1 |

| Однотактный преобразователь постоянного напряжения | 1990 |

|

SU1767649A1 |

| ОДНОВИБРАТОР | 1973 |

|

SU374711A1 |

Авторы

Даты

1980-04-30—Публикация

1978-03-16—Подача