I

Изобретение относится к вычислительной технике и может быть использовано при построении специализированных вычислительных устройств для решения задач исследования операций.

Задача упорядочения переменных заключается в присвоении каждой из низ соответствующего номера последовательности в зависимости от конкретного значения переменной.

Известно устройство, содержащее индикатор максимального сигнала, осуществляющего выделение требуемой переменной и распределителя матричной релейной схемы, осуществляющего подготовку каналов для переноса последовательности напряжений 1.

Однако такому устройству присущи низкая точность, низкая надежность, трудоемкость автоматического ввода информации, трудоемкость обмена информацией в вычислительных системах с применением универсальных вычислительных мащин.

Наиболее близким по технической сущности к изобретению является устройство, содержащее блок управления, формирователи переменных и однотипные ячейки управляемого распределителя, элементы И и триггеры 2.

Недостаток этого устройства - недостаточная точность.

Цель изобретения - повышение точности устройства.

Поставленная цель достигается тем, что в указанное устройство, содержащее блок управления, коммутирующий блок, элемент И, триггер и счетчик, введены формирователи значений переменных и элементы ИЛИ,

10 причем первый и второй выходы блока управления подключены соответственно к первым входам первого и второго элементов И, третий выход блока управления соединен с первыми входами третьего и четвертого элементов И, второй вход которого подключен

15 к первому выходу триггера, второй выход которого соединен со вторыми входами первого, второго и третьего элементов И, входы триггера подключены к выходам первого и второго элементов ИЛИ, входы которого

20 соединены соответственно с выходами счетчика и третьего элемента ИЛИ, входы которого подключены к выходам формирователей значений переменных, первые входы которых соединены со входом счетчика и подключены к выходу четвертого элемента И, выход третьего элемента И соединен со вторыми входами формирователей значений переменных, третий вход каждого из которых подключен к первому выходу соответствующего коммутирующего блока, второй выход каждого коммутирующего блока, кроме последнего, соединен со вторым входом последующего коммутирующего блока, второй выход последнего коммутирующего блока подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с четвертыми входами формирователей значений переменных и подключен к четвертому выходу блока управления, выход первого элемента И соединен со вторым входом первого коммутирующего блока, выход второго элемента И подключен к третьим входам коммутирующих блоков, четвертые входы которых соединены с выходами соответствующих формирователей значений переменных, кроме того, каждый формирователь значений переменных содержит счетчик, элемент И и триггер, входы которого являются соответственно третьим и четвертым входами формирователя, выход триггера подключен к первому входу элемента И, второй вход которого является вторым входом формирователя, выход элемента И подключен ко входу первого счетчика, вход второго счетчика является первым входом формирователя, выходом которого является выход второго счетчика, вход второго триггера соединен с выходом второго элемента ИЛИ, первый вход которого подключен к выходу регенерационного счетчика, а второй вход - к выходу третьего элемента ИЛИ, каждый из п входов которого соединен с первым полюсом соответствующей модели переменной, причем единичный выход второго триггера соединен с первым входом третьего элемента И, второй вход которого соединен с третьим полюсом блока управления и со вторым входом четвертого элемента И, четвертые полюса моделей переменных объединены и соединены со входом ретенерационного счетчика и выходом третьего элемента И, причем четвертым полюсом каждой модели переменной является вход первого счетчика, а пятым полюсом тех же моделей единичный вход первого триггера.

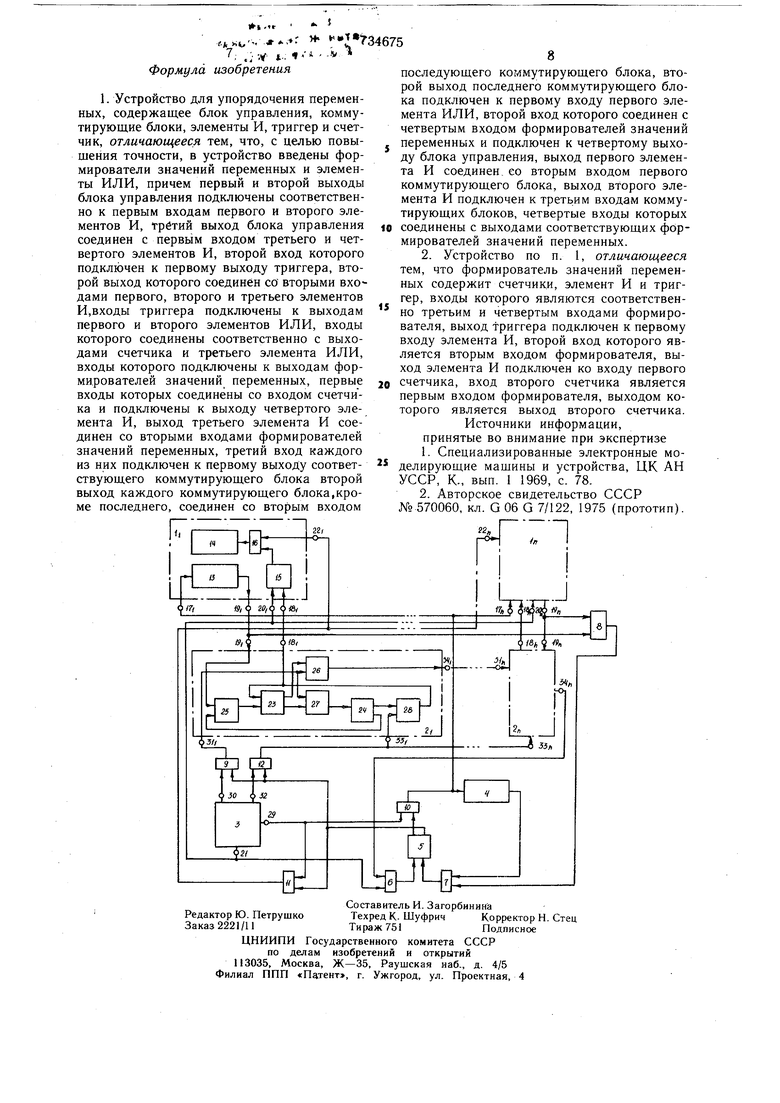

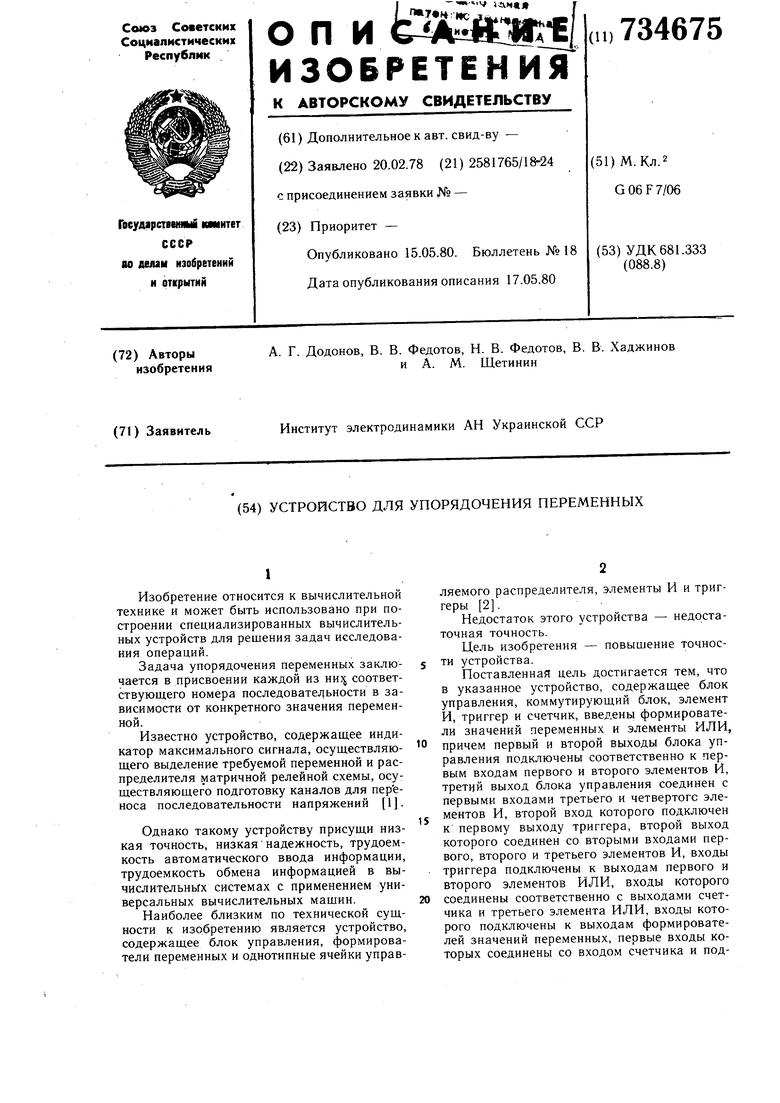

На чертеже представлена блок-схема предлагаемого устройства.

Устройство включает формирователи Ij-In значений переменных, коммутирующие блоки 2i-2, блок 3 управления, регенерационный счетчик 4, триггер 5, элементы 6-8 ИЛИ, элементы 9-12 И.

Каждый из формирователей 11 значений переменных, число которых равно числу упорядочиваемых переменных и числу ячеек коммутирующих блоков содержит счетчики 13 и 14 импульсов, триггер 15 и элемент 16 И. Входы 17 всех формирователей

значений переменных объединены со входом регенерационного счетчика 4 и с выходом элемента 10 И. Вход 18 каждого формирователя значений переменных подключен к разрядному выходу соответствующего коммутирующего блока, а выход 19 к установочному входу того же блока к соответствующему входу элемента 8 ИЛИ. Полюса 20 формирователей Ц-1«. объединены с выходом 21 блока управления и входом элемента 6 ИЛИ а входы 22 подключены к вы ходу элемента И 11.

Коммутирующие блоки представляющие собой идентичные ячейки, число которых равно числу упорядочиваемых переменных, предназначены для организации последоj вательного формирования значений переменных, у которых сформирован номер последовательности. В состав каждого блока 2i входят триггеры 23 и 24, элементы И 25, 26, 27 и 28.

Предлагаемое устройство позволяет осуществить упорядочение переменных как по возрастанию, так и по убыванию. При упорядочении переменных по возрастанию в счетчик 13 каждого формирователя IL значений переменных заносится число импульJ сов (N-li), где N - емкость счетчика 13; ii - число импульсов,пропорциональное величине i-ой переменной.

При упорядочении / еременных по убыванию в счетчик 13 модели tl заносится число импульсов пропорциональное величине

0 i-ой переменной.

Работа устройства при упорядочении переменных по возрастанию и убыванию аналогична. упорядочении переменных только по убыванию после занесения каждой упорядочиваемой переменной в соответствую щий формирователь 11, триггер 5, регенерационный счетчик 4, триггеры 23, 24 блоKOU 2 и счетчики 14 всех формирователей устанавливаются в нулевое состояние.

® Процесс упорядочения переменных состоит из последовательно повторяющихся циклов и начинается с момента подачи импульса «пуск блоком 3 управ 1ения, в функции которого входит также выработка импульсов ГИ1, ГИг и ГИг, сдвинутых относительно друг друга. Импульс «пуск с полюса 21 блока 3 управления поступает на полюса 20 всех формирователей 1 t-1, а также устанавливает триггер 5 через элемент 6 ИЛИ в единичное состояние. В каждом формирователе 1 импульс «пуск с полюса 20 поступает на вход триггера 15 и устанавливает его в единичное состояние. Импульсы ГИ1 с полюса 20 блока управления поступают через элемент 10 И на вход

регенерационного счетчика 4 и через полюс 17 на входы счетчиков 13 всех формирователей Ij-1„. Импульсы ГИ1 поступают на вход регенерационного счетчика и на полюс 17 формирователей до тех пор, пока на полюсе 19 с выхода счетчика 13 какого-либо формирователя не появится импульс переполнения. С появлением импульса переполнения на полюсе 19 происходит блокировка входа элемента 10 И. Это осуществляется следующим образом.

Импульс с полюса 19 поступает на один из входов элемента 8 ИЛИ, а с выхода элемента 8 ИЛИ этот сигнал проходит через элемент 7 ИЛИ и устанавливает в нулевое состояние триггер 5. Нулевое состояние триггера 5 запрещает поступление импульсов FHi через элемент 10 И. Импульс переполнения, поступивший на установочный вход соответствующего коммутирующего блока с полюса 19, устанавливает триггер 23 через элемент 25 И в единичное состояние. Нулевое состояние триггера 5 выдает разрешение на вход элементов 9, 11 и 12 И. В результате чего импульсы ГИ начинают поступать через элемент 11 И на полюсе 22 всех формирователей 11-l, а импульсы ГИ с. полюса 30 блока 3 управления через элемент 9 И поступают на управляющий вход 31 первого блока 21. Блок 3 управления вырабатывает также на полюсе 32 импульсы ГИг, сдвинутые относительно серии импульсов ГИг. Импульсы ГИ поступают через элемент 12 И на синхронизирующие входы 331-33tt. всех блоков 2.

Нервый импульс ГИ1, поступающий на полюс 22, заносится в счетчик 14 через элемент И всех формирователей li-Itt. Следующий за импульсом ГИ,, импульс ГИг поступает на полюс 31 первого блока 21 и распространяется по распределителю, пока не дойдет до выбранного блока, который соответствует формирователю с переполнившимся счетчиком 13.

Происходит это следующим образом.

Предварительно триггеры 23 и 24 устанавливаются в нулевое состояние. При появлении сигнала переполнения на полюсе 19L через элемент 25 И устанавливается в единичное состояние триггер 23 блока 21. Вследствие этого на нулевом его выходе, соединенным со входом элемента 26 И, появляется запрещенный потенциал, а на единичном выходе - разрешающий потенциал. С появлением на полюсе 31 первого импульса серии ГИг, который через элемент 27 И устанавливает триггер 24 блока 2iB едини,чное состояние (если триггер 23 этого блока находится в единичном состоянии). Тем самым снимается разрешающий потенциал со входа элемента 25 И и подается разрещающий потен циал на элемент 28 И. Импульс серии ГИг, следующий за импульсом ГИ2, поступает на полюс 33 коммутируемого блока и через элемент 28 И устанавливает триггер 23 в нулевое состояние, а также этот импульс проходит на разрядный выход блока полюса 18i. Нулевое состояние триггера 23 выдает разрешение на прохождение импульсов ГИг со входа 311 коммутирующего блока на его выход 341 через элемент 26 И. С разрядного выхода этот импульс поступает на полюс 18 того формирователя, у которого первым появляется импульс переполнения на полюсе 19, и устанавливает триггер 15 в нулевое состояние. Нулевое состояние триггера15 блокирует вход элемента 16 И и поэтому в этом формирователе в счетчик 14 не будет заносится больше ни одного импульса ГИ (. Сигнал же с полюса 311 10 первого блока 21 передается от блока к блоку, пропуская те блоки, на входах элементов 25 И которых нет разрещения на формирователей 1. Так, импульс движения распространяется по коммутирующим блокам, пока не появится на выходе 34 последнего блока.

Появившийся импульс на выходе 34пблока 2, пройдя элемент 6 ИЛИ, устанавливает триггер 5 в единичное состояние. Далее весь цикл работы устройства повторяется аналогично описанному.

На полюсах 19 формирователей li-l-n последовательно появляются импульсы переполнения счетчиков 13, что соответствует последовательному выбору нужных переменных. Аналогично от цикла к циклу в счетчики 14 будет заносится по одному импульсу ГИ1, что соответствует возрастанию номера, который присваивается каждой переменной.

Если в процессе упорядочнения переменно ных окажется, что две или более переменных имеют одинаковую величину, то в этом случае устройство произведет их упорядочение по мере возрастания номера блока соответствующего формирователя Ц. Это объясняется тем, что импульс ГИя первым появится 5 на разрядном выходе того блока, который ближе к началу последовательности блоков 2.

Наличие регенерационного счетчика 4 позволяет восстанавливать информацию о величине упорядочиваемых переменных в счетчиках 13формирователей 1|-In. Это происходит потому, что импульс «пуск, выработанный коммутирующими блоками и соответствующий выбору последней их упорядочиваемых переменных, установит триггер 5 в единичное состояние. Единичное состояние 5 триггера 5 выдает разрешение на вход элемента 10 И, что дает возможность поступать импульсам ГИ( на вход регенерационного счетчика 4 и полюса 17 всех формирователей . Импульсы ГИ 1 будут поступать до тех пор, пока на вцходе регенерационного счетчика 4 не появится импульс переполнения. Этот импульс переполнения установит через элемент 7 ИЛИ триггер 5 в нулевое состояние, свидетельствуя о том, что процесс упорядочения и восстановления переменных 5 окончен.

Устройство отличается более высокой точностью по сравнению с устройствами аналогичного назначения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Модель двунаправленной ветви | 1977 |

|

SU736121A1 |

| Устройство для исследования графа | 1978 |

|

SU744593A1 |

| Устройство для вычисления текущих ресурсов | 1978 |

|

SU746589A1 |

| Устройство для расчета сетевыхгРАфиКОВ | 1979 |

|

SU851417A1 |

| Устройство для исследования сетей | 1971 |

|

SU486330A1 |

| Устройство для моделирования сетей | 1983 |

|

SU1138806A1 |

| Устройство для решения линейных дифференциальных уравнений | 1987 |

|

SU1476486A1 |

| Устройство для моделирования сетей | 1984 |

|

SU1179365A1 |

| Устройство для исследования графов | 1979 |

|

SU807313A2 |

| Устройство для исследования графов | 1975 |

|

SU643880A1 |

Авторы

Даты

1980-05-15—Публикация

1978-02-20—Подача