1147

Изобретение относится к цифровой вычислительной технике, в частности к устройствам для решения линейных дифференциальных уравнений.

Цель изобретения - расширение функциональных возможностей за счет решения дифференциальных уравнений высокого порядка.

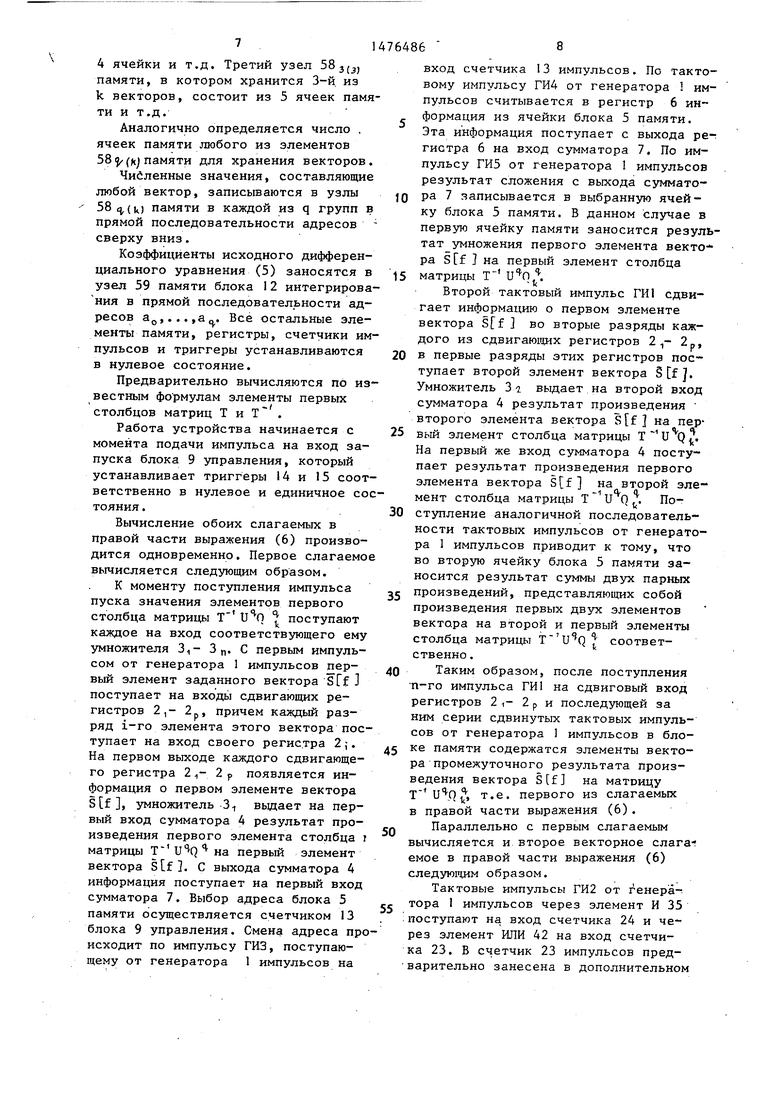

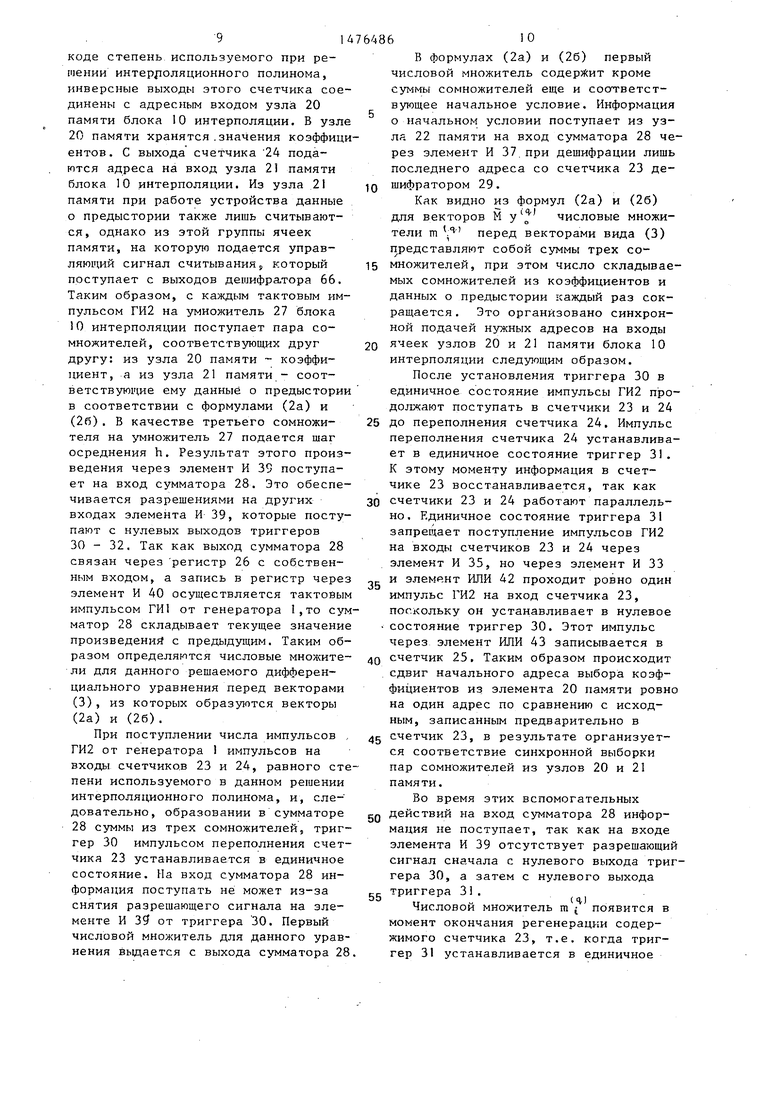

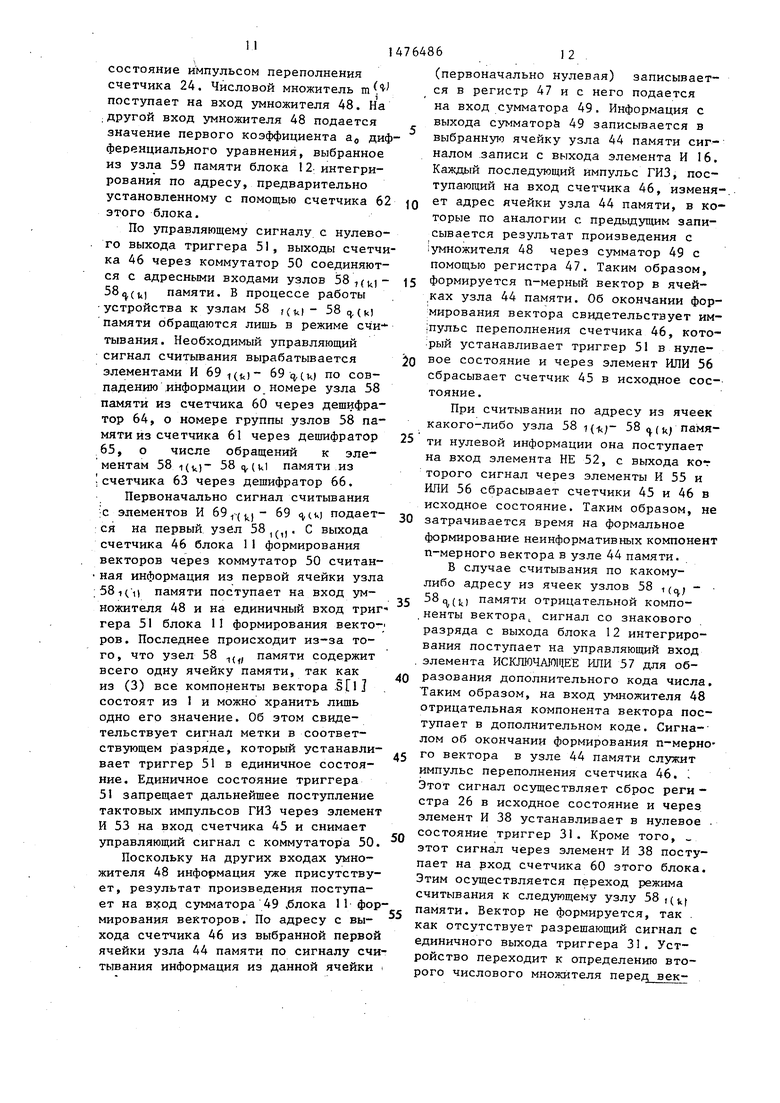

На фиг. изображена схема устройства; на фиг.2 - схема блока интерполяции; на фиг.З - схема блока формирования векторов; на фиг.4 - схема блока интегрирования.

Устройство содержит генератор 1 импульсов, сдвигающие регистры 2,- 2 , умножители 3,- 3h, первый сумматор 4, узел 5 памяти, регистр 6, второй сумматор 7, элементы ИЛИ 8 ,- 8р, блок 9 управления, блок 10 интерполя- ции, блок 1 1 формирования векторов и блок 12 интегрирования.

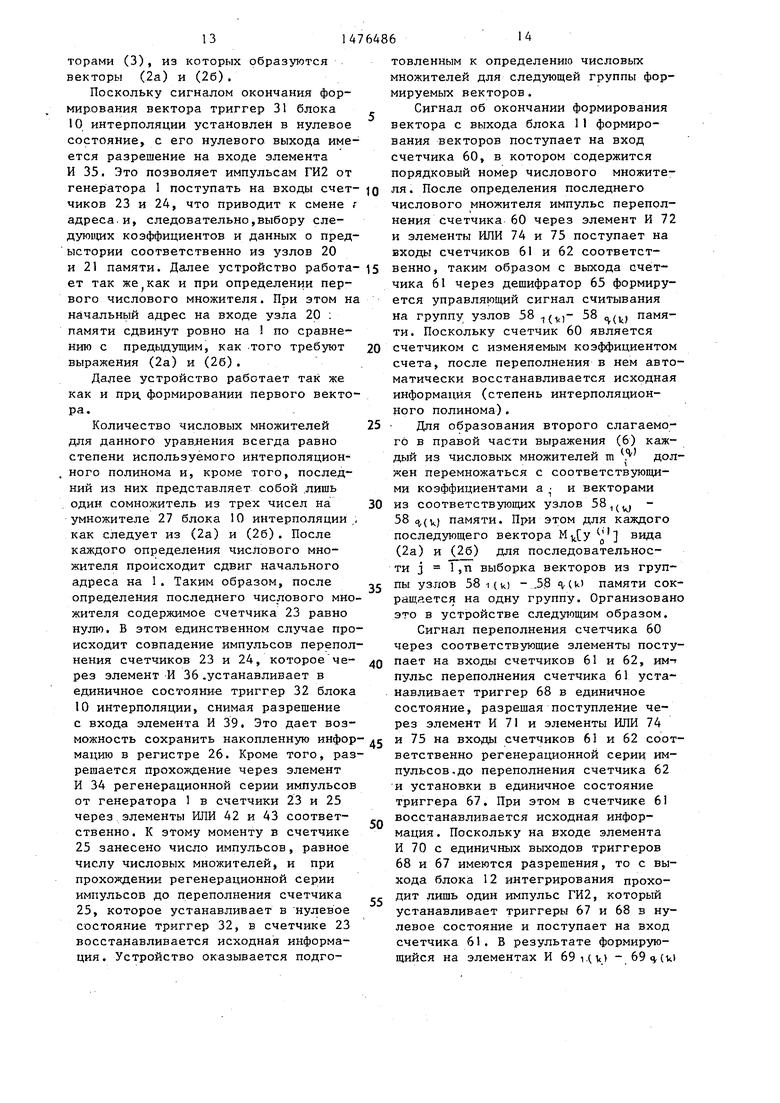

Блок 9 управления состоит из счетчика 13, первого 14 и второго 15 триггеров, первого 16, второго 17 и третьего 18 элементов И и элемента ИЛИ 19.

Блок 10 интерполяции образуют первый 20, второй 21 и третий 22 узлы памяти, первый 23, второй 24 и третий 25 счетчики, регистр 26, умножитель 27, сумматор 28, дешифратор 29, первый 30, второй 31 и третий 32 триггеры, первый 33, второй 34, третий 35, четвертый 36, пятый 37, шестой 38, седьмой 39, восьмой 40 и девятый 41 элементы И, а также первый 42 и второй 43 элементы ИЛИ.

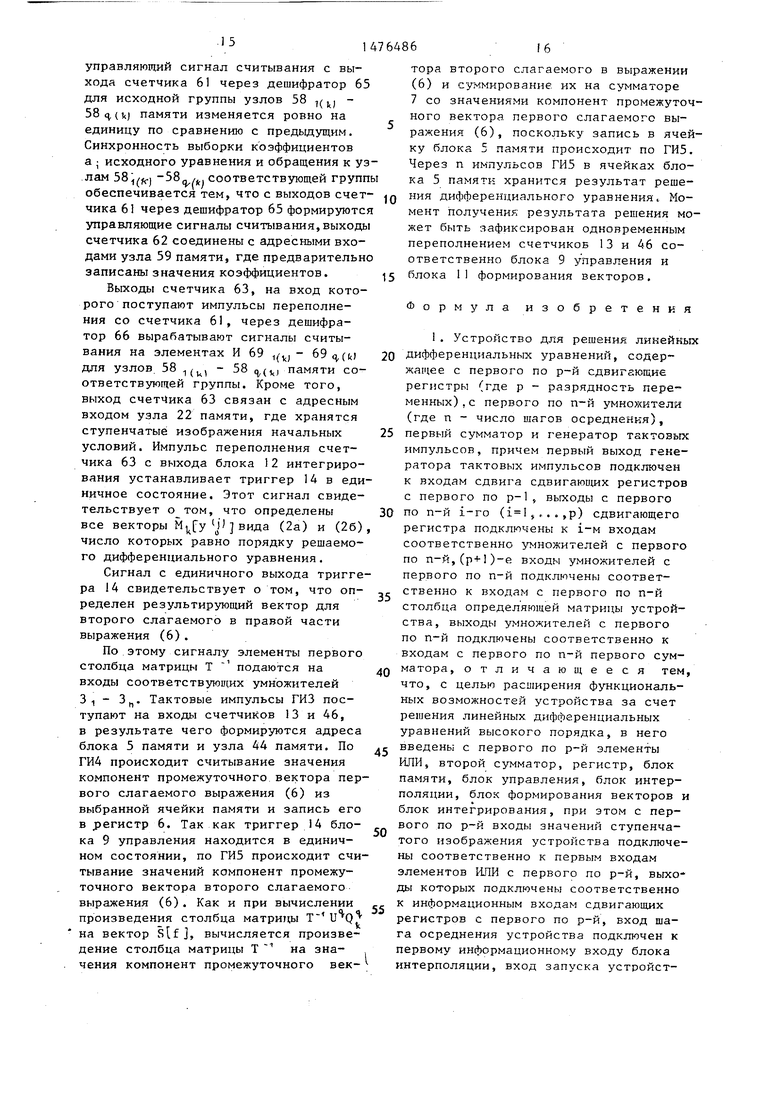

Блок 11 формирования векторов включает з себя узел 44 памяти, первый 45 и второй 46 счетчики, регистр 47, умножитель 48, сумматор 49, коммутатор 50, триггер 51, элемент НЕ 52 первый 53, второй 54 и третий 55 элементы И,,элемент ИЛИ 56 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 57.

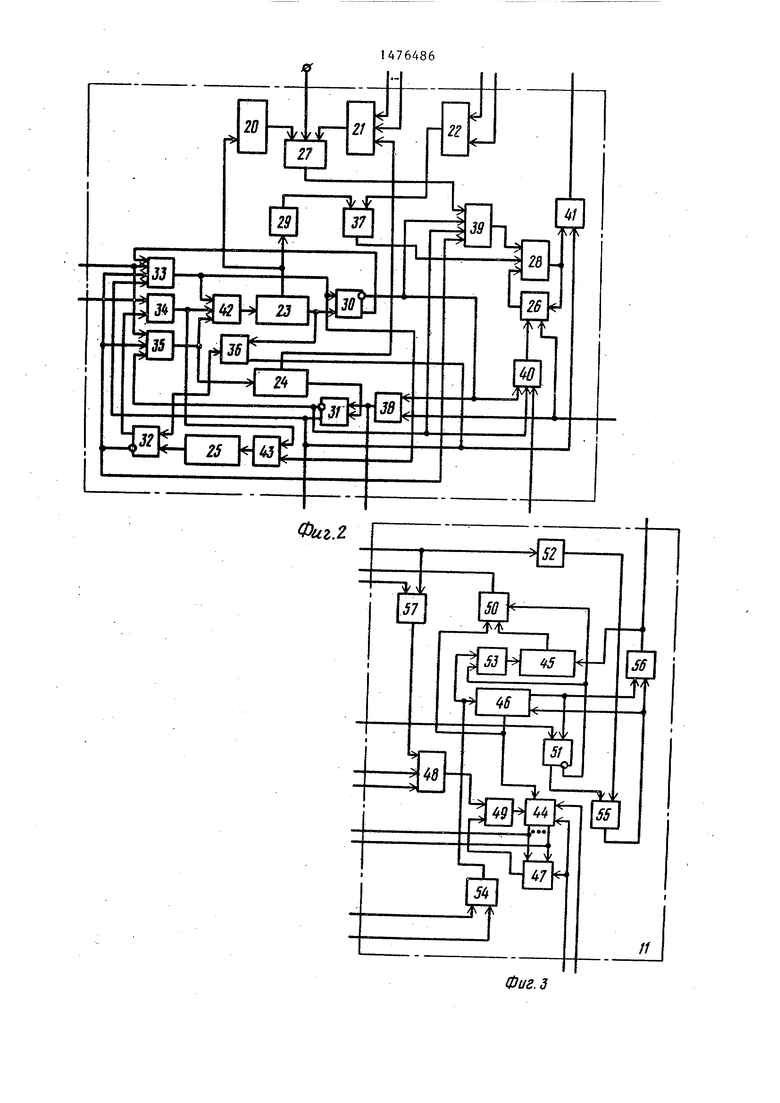

Блок 12 интегрирования содержит группу из q узлов памяти 58 t(Kj- 58 q.U) узел 59 памяти, первый 60, второй 6, третий 62 и четвертый 63 счетчики, первый 64, второй 65 и третий 66 дешифраторы, первый 67 и второй 68 триггеры, группу из элементов И 69 i(v) 69 ci.(t первый 70, второй 71 и третий 72 элементы И, а также первый 73 и второй 74 элементы ИЛИ.

Для простого интегратора справедливы выражения для ступенчатых изображений

(-i) 1

Гу - (V - UPk .

(I)

Обозначим в правой части выражения (I) вектор ступенчатых изображений известных значений через

М ь I У о J который для квадратичной интерполяции имеет вид

МгГУо( +иР4Гу()

h Т

ВСу Г М- - .

U

+ Tf )

sWiV

y;

(.V

« - s t yov

К

(2a)

+ ySj- sCy nsCi +

ч S

СУ(:

s

mlT stl

+ m

(V 5

H

Sc/4

для кубической интерполяции

+ -я 30

35

+

( У (Я+

(

40

i т г

S ,

(26)

где векторы sill, Rd1, Srf n т.д. имеют вид

(1,1,...,I)T;

--

55

-тг

(1,0,...О)

§cf -i- (l,-l,o,...,0)T; h

(3)

5Г- -i- (I,-2,1,00)T

hj

Для выражения (1) имеют

sfyj 14764864

для кубической интерполяции

| название | год | авторы | номер документа |

|---|---|---|---|

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1337904A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СУБОПТИМАЛЬНОГО РАЗМЕЩЕНИЯ И ЕГО ОЦЕНКИ | 2001 |

|

RU2193796C2 |

| Устройство для подсчета минимального значения интенсивности размещения в многопроцессорных кубических циклических системах при однонаправленной передаче информации | 2018 |

|

RU2688236C1 |

| Цифровой интегратор | 1988 |

|

SU1580359A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Устройство для вычисления логических производных многозначных данных | 1990 |

|

SU1837277A1 |

| Устройство для обработки структур данных | 1990 |

|

SU1709328A1 |

ИЗОБРЕТЕНИЕ ОТНОСИТСЯ К ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКЕ ,В ЧАСТНОСТИ, К УСТРОЙСТВАМ ДЛЯ РЕШЕНИЯ ЛИНЕЙНЫХ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ. ЦЕЛЬ ИЗОБРЕТЕНИЯ - РАСШИРЕНИЕ ФУНКЦИОНАЛЬНЫХ ВОЗМОЖНОСТЕЙ ЗА СЧЕТ РЕШЕНИЯ ЛИНЕЙНЫХ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ ВЫСОКОГО ПОРЯДКА. ПОСТАВЛЕННАЯ ЦЕЛЬ ДОСТИГАЕТСЯ ТЕМ, ЧТО УСТРОЙСТВО СОДЕРЖИТ ГЕНЕРАТОР 1 ТАКТОВЫХ ИМПУЛЬСОВ, Р СДВИГАЮЩИХ РЕГИСТРОВ 21-2Р ГДЕ Р - РАЗРЯДНОСТЬ ПЕРЕМЕННЫХ, N УМНОЖИТЕЛЕЙ 31-3Р, ГДЕ N - ЧИСЛО ШАГОВ ОСРЕДНЕНИЯ, ПЕРВЫЙ СУММАТОР 4, БЛОК 5 ПАМЯТИ, РЕГИСТР 6, ВТОРОЙ СУММАТОР 7, Р ЭЛЕМЕНТОВ ИЛИ 81-8Р, БЛОК 9 УПРАВЛЕНИЯ, БЛОКИ 10 ИНТЕРПОЛЯЦИИ, 11 ФОРМИРОВАНИЯ ВЕКТОРОВ И 12 ИНТЕГРИРОВАНИЯ. 3 З.П. Ф-ЛЫ, 4 ИЛ.

и

- (И+) - (я-)4) Q

йЛуУ-.

Допустим необходимо решить дифференциальное уравнение с постоянными коэффициентами

ш

f(t)

(5)

и начальными условиями у(О), у (О),

..., (О).

Подставляя ступенчатые изображения для производных (4) в (5) получают

Т

sly г

I

J +

Ям

i -(

х .

Элементы первого столбца матрицы Т и обратной матрицы Т могут быть вычислены по формулам (см. Береговенко Г.Я., Пухов Г.Е. Ступенчатые изображения и их применение.- Киев: Наукова думка, 1983, с.106).

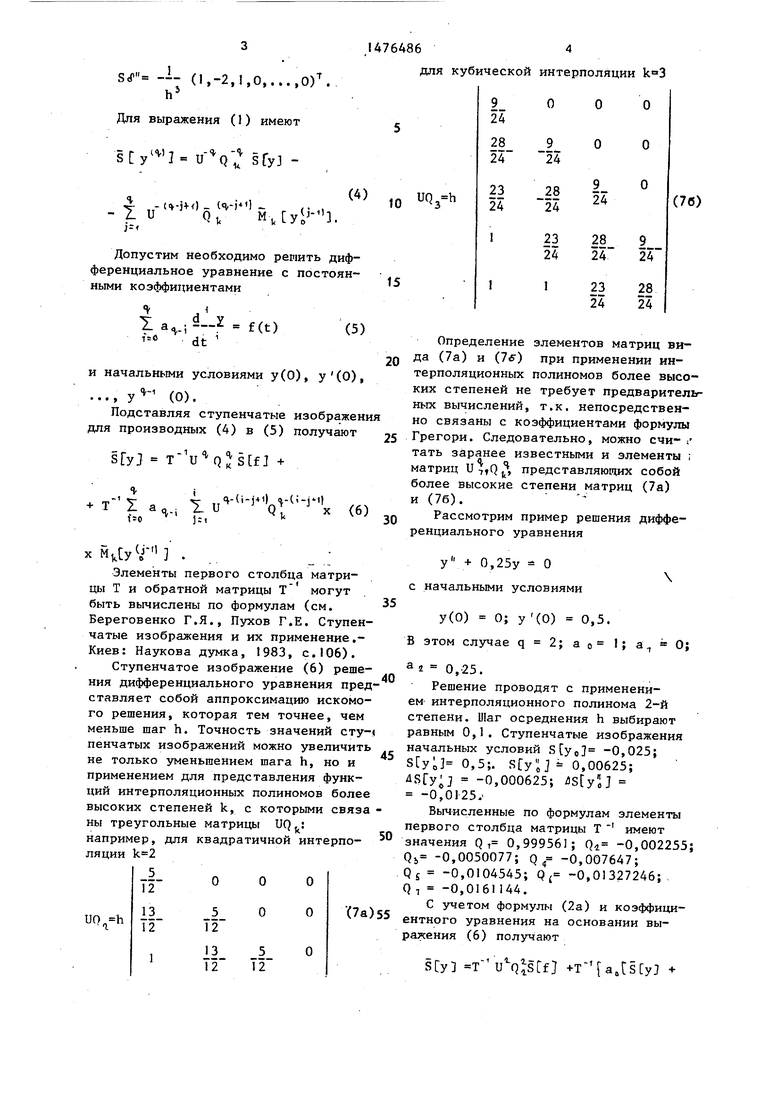

Ступенчатое изображение (6) решения дифференциального уравнения представляет собой аппроксимацию искомого решения, которая тем точнее, чем меньше шаг h. Точность значений ступенчатых изображений можно увеличить не только уменьшением шага h, но и применением для представления функций интерполяционных полиномов более высоких степеней k, с которыми связа ны треугольные матрицы UQ fc: например, для квадратичной интерпо ляции

-

(4) ,0

(76)

20

я

25

30

Определение элементов матриц вида (7а) и (7е) при применении интерполяционных полиномов более высоких степеней не требует предварительных вычислений, т.к. непосредственно связаны с коэффициентами формулы Грегори. Следовательно, можно счи- тать заранее известными и элементы . матриц UifQ, представляющих собой более высокие степени матриц (7а) и (76).

Рассмотрим пример решения дифференциального уравнения

-

35

40

45

50

55

у + 0,25у О с начальными условиями

у(0) О; у (О) 0,5. В этом случае q 2;a0 l a1eO;

а 0,25.

Решение проводят с применением интерполяционного полинома 2-й степени. Шаг осреднения h выбирают равным 0,1. Ступенчатые изображения начальных условий -0,025; SCy;i 0,5;. SfyJJ 0,00625; дБГу;; - -0,000625; -0,0125.

Вычисленные по формулам элементы первого столбца матрицы Т имеют значения Q , 0,999561; Qi -0,002255; Qb -0,0050077; Q -0,007647; QЈ -0,0104545; Q -0,01327246; Q , -0,0161144.

С учетом формулы (2а) и коэффициентного уравнения на основании выражения (6) получают

sCyl -т u -qЈstf} +

51476486,6

+ UPaty + UQa( UPjy ) + . 4,5;5,5;6,5;...)T+0,0000 05208 (0,417;

1,083; 1; ;...) T (0,02500;

+ a,UQt(S y0J + UP2Cy j) 0,07504; 0,12506; 0,17508; 0,22510;

g 0,27501; 0,32501;...)T.

в J + T (Mafy +UQ7M y )Значения компонент искомого вектора SfyJ (0,024989; 0,074951;

-r1UQlSlf + H( +0,17415; 0,22310; 0,271434;0,319180;

)

+ s (Voj + - Л5 У75|1 +Т7 10При п°Дготовке к решению задачи в

2 L J 12, °L J L I/ 1Jсчетчик 23 блока 10 интерполяции и в

счетчик 60 блока 12 интегрирования

+ UQflt(SeCy J + o +заносится в дополнительном коде число импульсов, равное степени интерпоhг т icftl с Г Т cjift 15 ляционного полинома k, используемого г

2 ° У JSL1J + у2 У - Sdjr при решении данного уравнения. В счетчиках 61 и 63 блока 12 интегрирова- UO-Sff + +Ния заносится в дополнительном коде

число импульсов, равное порядку реша+ ™ с + ттп « 5ГП + « - 20 емого Дифференциального уравнения q. + m7,ScT+ + mMS«OJ - Кроме того в ячейки узла 20 памяти f

блока 10 интерполяции заносятся из- -1 rci - вестные численные коэффициенты из

-Т UQ,SlfJ + Т V.формул вида (2а) и (26). В ячейки

25 узла 21 памяти блока 10 интерполяции Значения коэффициентов для векто м заносятся по группам заранее подсчира равнытайные численные значения величин

тпв( + | Sjy (; ,i7Styt(yj (данные о предыстории) и т.д. i 0, где i - номер h .„ ..„ч л Лог . л п... группы. В ячейки узла 22 памяти 1У J ка 10 интерполяции заносятся ступен,5-0,, . . 0,000625 - -0,000005,, Г

2При этом численные коэффициенты и

mia тг soty 0,01 т 0,5 35 данные о предыстории одной группы

размещаются соответственно в блоках

0,000416;VQv 20 и 21 памяти таким образом, чтобы

(.о)„

при подаче прямой последовательности

, - h г- ц,адресов из памяти одновременно извлет14а (SaLy J+ 2 S0Ly I + 40 кались численный коэффициент и соотh Лor l nc n пс ветствующие ему данные о предыстории + f2 Л8«1У J ° 5 + ° 05 согласно (2а) и (26).

0 00625 -01- ---«О 0125 Устройство в процессе решения за 12 дачи оперирует n-мерными векторами,

0,500208;45 но число ячеек памяти для хранения

этих векторов в каждом из узлов m - Ь о г-и Ч п ш . 58 а (памяти не обязательно равно п.

1лл(o°6iyjlj ulio„

1Zi i Например, элемент 58 1tl) памяти содержит одну ячейку памяти для хране- 0,00625 0,000005208.50 ния перВого из векторов вида (3),

так как все элементы этого векто- Используя векторы (3) получают ра равны , Второй из векторов вида

вектор(3) этой группы хранится в узле

V -0,0000052(1; l;...l)r +58Hi) памяти, состоящем всего из

5 2-х ячеек памяти, так как (кроме лер- + 0,00417(1; О; 0;...0)т +вого) остальные элементы вектора

равны 0. Второй узел 58 -геи памяти + 0,05002084(0,417; 1;5; 2,5; 3,5; содержит 3 ячейки памяти, третий 4 ячейки и т.д. Третий узел 583(3 памяти, в котором хранится 3-й из k векторов, состоит из 5 ячеек памяти и т.д.

Аналогично определяется число , ячеек памяти любого из элементов 58ty(b) памяти для хранения векторов.

Численные значения, составляющие любой вектор, записываются в узлы 58q,(b.) памяти в каждой из q групп в прямой последовательности адресов сверху вниз.

Коэффициенты исходного дифференциального уравнения (5) заносятся в узел 59 памяти блока 12 интегрирова ния в прямой последовательности адресов а0,...,а„. Все остальные элементы памяти, регистры, счетчики импульсов и триггеры устанавливаются в нулевое состояние.

Предварительно вычисляются по известным формулам элементы первых столбцов матриц Т и Т .

Работа устройства начинается с момента подачи импульса на вход запуска блока 9 управления, который устанавливает триггеры 14 и 15 соответственно в нулевое и единичное сотояния .

Вычисление обоих слагаемых в правой части выражения (6) производится одновременно. Первое слагаемое вычисляется следующим образом.

К моменту поступления импульса пуска значения элементов первого столбца матрицы поступают каждое на вход соответствующего ему умножителя 3,- 3 п. С первым импульсом от генератора 1 импульсов первый элемент заданного вектора Sff J поступает на входы сдвигающих регистров 2,- 2р, причем каждый разряд 1-го элемента этого вектора поступает на вход своего регистра 2;. На первом выходе каждого сдвигающего регистра 2.,- 2 Р появляется информация о первом элементе вектора , умножитель 3., выдает на первый вход сумматора 4 результат произведения первого элемента столбца i матрицы первый элемент вектора . С выхода сумматора 4 информация поступает на первый вход сумматора 7. Выбор адреса блока 5 памяти осуществляется счетчиком 13 блока 9 управления. Смена адреса происходит по импульсу ГИЗ, поступающему от генератора 1 импульсов на

вход счетчика 13 импульсов. По тактовому импульсу ГИ4 от генератора I импульсов считывается в регистр 6 информация из ячейки блока 5 памяти. Эта информация поступает с выхода регистра 6 на вход сумматора 7. По импульсу ГИ5 от генератора 1 импульсов результат сложения с выхода суммато- jg pa 7 записывается в выбранную ячейку блока 5 памяти. В данном случае в первую ячейку памяти заносится результат умножения первого элемента вектора на первый элемент столбца 15 матрицы .

Второй тактовый импульс ГИ1 сдвигает информацию о первом элементе вектора Sff во вторые разряды каждого из сдвигающих регистров 2,- 2р, 20 в первые разряды этих регистров поступает второй элемент вектора . Умножитель 3 i выдает на второй вход сумматора 4 результат произведения второго элемента вектора на пер- 5 вый элемент столбца матрицы Т мU Q Ј. На первый же вход сумматора 4 поступает результат произведения первого элемента вектора на второй элемент столбца матрицы Q J. По- 0 ступление аналогичной последовательности тактовых импульсов от генератора I импульсов приводит к тому, что во вторую ячейку блока 5 памяти заносится результат суммы двух парных 5 произведений, представляющих собой произведения первых двух элементов вектора на второй и первый элементы столбца матрицы Ј соответственно .

0 Таким образом, после поступления n-го импульса ГИ на сдвиговый вход регистров 2 1- 2 р и последующей за ним серии сдвинутых тактовых импульсов от генератора I импульсов в бло- 5 ке памяти содержатся элементы вектора промежуточного результата произведения вектора на матрицу , т.е. первого из слагаемых в правой части выражения (6). 0 Параллельно с первым слагаемым

вычисляется и второе векторное слагаемое в правой части выражения (6) следующим образом.

Тактовые импульсы ГИ2 от генера- г тора I импульсов через элемент И 35 поступают на вход счетчика 24 и через элемент ИЛИ 42 на вход счетчика 23. В счетчик 23 импульсов предварительно занесена в дополнительном

коде степень используемого при решении интерполяционного полинома, инверсные выходы этого счетчика соединены с адресным входом узла 20 памяти блока 10 интерполяции. В узле 20 памяти хранятся значения коэффициентов. С выхода счетчика 24 подаются адреса на вход узла 21 памяти блока 10 интерполяции. Из узла 21 памяти при работе устройства данные о предыстории также лишь считываются, однако из этой группы ячеек памяти, на которую подается управляющий сигнал считывания, который поступает с выходов дешифратора 66. Таким образом, с каждым тактовым импульсом ГИ2 на умножитель 27 блока 0 интерполяции поступает пара сомножителей, соответствующих друг другу: из узла 20 памяти - коэффициент, а из узла 21 памяти - соответствующие ему данные о предыстории в соответствии с формулами (2а) и (2б). В качестве третьего сомножителя на умножитель 27 подается шаг осреднения h. Результат этого произведения через элемент И 39 поступает на вход сумматора 28. Это обеспечивается разрешениями на других входах элемента И 39, которые поступают с нулевых выходов триггеров 30-32. Так как выход сумматора 28 связан через регистр 26 с собственным входом, а запись в регистр через элемент И 40 осуществляется тактовым импульсом ГИ1 от генератора 1,то сумматор 28 складывает текущее значение произведений с предыдущим. Таким образом определяются числовые множители для данного решаемого дифференциального уравнения перед векторами (3), из которых образуются векторы (2а) и (26).

При поступлении числа импульсов ГИ2 от генератора 1 импульсов на входы счетчиков 23 и 24, равного степени используемого в данном решении интерполяционного полинома, и, следовательно, образовании в сумматоре 28 суммы из трех сомножителей, триггер 30 импульсом переполнения счетчика 23 устанавливается в единичное состояние. На вход сумматора 28 информация поступать не может из-за снятия разрешающего сигнала на элементе И 35 от триггера 30. Первый числовой множитель для данного уравнения выдается с выхода сумматора 28

В формулах (2а) и (26) первый числовой множитель содержит кроме суммы сомножителей еще и соответствующее начальное условие. Информация о начальном условии поступает из узла 22 памяти на вход сумматора 28 через элемент И 37 при дешифрации лишь последнего адреса со счетчика 23 дешифратором 29.

Как видно из формул (2а) и (26) для векторов М числовые множители m перед векторами вида (3) представляют собой суммы трех со5 множителей, при этом число складываемых сомножителей из коэффициентов и данных о предыстории каждый раз сокращается . Это организовано синхронной подачей нужных адресов на входы

о ячеек узлов 20 и 21 памяти блока 10 интерполяции следующим образом.

После установления триггера 30 в единичное состояние импульсы ГИ2 продолжают поступать в счетчики 23 и 24

5 до переполнения счетчика 24. Импульс переполнения счетчика 24 устанавливает в единичное состояние триггер 31. К этому моменту информация в счетчике 23 восстанавливается, так как

0 счетчики 23 и 24 работают параллельно. Единичное состояние триггера 31 запрещает поступление импульсов ГИ2 на входы счетчиков 23 и 24 через элемент И 35, но через элемент И 33 и элемент ИЛИ 42 проходит ровно один импульс ГИ2 на вход счетчика 23, поскольку он устанавливает в нулевое состояние триггер 30. Этот импульс через элемент ИЛИ 43 записывается в

Q счетчик 25. Таким образом происходит сдвиг начального адреса выбора коэффициентов из элемента 20 памяти ровно на один адрес по сравнению с исходным, записанным предварительно в счетчик 23, в результате организуется соответствие синхронной выборки пар сомножителей из узлов 20 и 21 памяти.

Во время этих вспомогательных действий на вход сумматора 28 информация не поступает, так как на входе элемента И 39 отсутствует разрешающий сигнал сначала с нулевого выхода триггера 30, а затем с нулевого выхода триггера 31.

5

5

0

55

и -(И

Числовой множитель m { появится в

момент окончания регенерации содержимого счетчика 23, т.е. когда триггер 31 устанавливается в единичное

1 1

20

25

состояние импульсом переполнения счетчика 24. Числовой множитель m поступает на вход умножителя 48. На другой вход умножителя 48 подается значение первого коэффициента а0 дифференциального уравнения, выбранное из узла 59 памяти блока 12 интегрирования по адресу, предварительно установленному с помощью счетчика 62 этого блока.

По управляющему сигналу с нулевого выхода триггера 51, выходы счетчика 46 через коммутатор 50 соединяются с адресными входами узлов 587(ki 58(ы памяти. В процессе работы устройства к узлам 58 км - 58 q, (ю памяти обращаются лишь в режиме счи тывания. Необходимый управляющий сигнал считывания вырабатывается элементами И 69 к)- 69 q,() по совпадению информации о номере узла 58 амяти из счетчика 60 через дешифратор 64, о номере группы узлов 58 памяти из счетчика 61 через дешифратор 5, о числе обращений к элементам 58 i(kj- 58 q,(ul памяти из

счетчика 63 через дешифратор 66.

Первоначально сигнал считывания с элементов И 69 цм подается на первый узел 58,,,. С выхода счетчика 46 блока 11 формирования векторов через коммутатор 50 считанная информация из первой ячейки узла памяти поступает на вход умножителя 48 и на единичный вход триггера 51 блока П формирования векто- ров. Последнее происходит из-за того, что узел 58 1(f/ памяти содержит всего одну ячейку памяти, так как из (3) все компоненты вектора состоят из I и можно хранить лишь одно его значение. Об этом свидетельствует сигнал метки в соответствующем разряде, который устанавли- вает триггер 51 в единичное состояние. Единичное состояние триггера 51 запрещает дальнейшее поступление тактовых импульсов ГИЗ через элемент И 53 на вход счетчика 45 и снимает управляющий сигнал с коммутатора 50. Поскольку на других входах умножителя 48 информация уже присутствует, результат произведения поступает на вход сумматора 49 .блока 11 формирования векторов. По адресу с выхода счетчика 46 из выбранной первой ячейки узла 44 памяти по сигналу считывания информация из данной ячейки

JQ - 15

30

35

40

20

25

76486 2

(первоначально нулевая) записывается в регистр 47 и с него подается на вход сумматора 49. Информация с выхода сумматора 49 записывается в выбранную ячейку узла 44 памяти сигналом записи с выхода элемента И 16. Каждый последующий импульс ГИЗ, поступающий на вход счетчика 46, изменя- JQ ет адрес ячейки узла 44 памяти, в которые по аналогии с предыдущим записывается результат произведения с умножителя 48 через сумматор 49 с помощью регистра 47. Таким образом, 15 Формируется n-мерный вектор в ячейках узла 44 памяти. Об окончании формирования вектора свидетельствует импульс переполнения счетчика 46, который устанавливает триггер 51 в нулевое состояние и через элемент ИЛИ 56 сбрасывает счетчик 45 в исходное состояние .

При считывании по адресу из ячеек какого-либо узла 58 1(-ь;- 58 .(kj памяти нулевой информации она поступает на вход элемента НЕ 52, с выхода ког торого сигнал через элементы И 55 и ИЛИ 56 сбрасывает счетчики 45 и 46 в исходное состояние. Таким образом, не затрачивается время на формальное формирование неинформативных компонент n-мерного вектора в узле 44 памяти. В случае считывания по какому- либо адресу из ячеек узлов 58 , („j - 58 (jj памяти отрицательной компоненты вектора, сигнал со знакового разряда с выхода блока 12 интегрирования поступает на управляющий вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 57 для образования дополнительного кода числа. Таким образом, на вход умножителя 48 отрицательная компонента вектора поступает в дополнительном коде. Сигналом об окончании формирования п-мерно- го вектора в узле 44 памяти служит импульс переполнения счетчика 46. . Этот сигнал осуществляет сброс реги - стра 26 в исходное состояние и через элемент И 38 устанавливает в нулевое состояние триггер 31. Кроме того, этот сигнал через элемент И 38 поступает на вход счетчика 60 зтого блока. Этим осуществляется переход режима считывания к следующему узлу 58i(k памяти. Вектор не формируется, так как отсутствует разрешающий сигнал с единичного выхода триггера 31. Устройство переходит к определению второго числового множителя перед век30

35

40

торами (3), из которых образуются векторы (2а) и (26) .

Поскольку сигналом окончания формирования вектора триггер 31 блока 10 интерполяции установлен в нулевое состояние, с его нулевого выхода имеется разрешение на входе элемента И 35. Это позволяет импульсам ГИ2 от

генератора 1 поступать на входы счет- jg ля. После определения последнего

чиков 23 и 24, что приводит к смене ; адреса и, следовательно,выбору следующих коэффициентов и данных о предыстории соответственно из узлов 20

числового множителя импульс переп нения счетчика 60 через элемент И и элементы ИЛИ 74 и 75 поступает входы счетчиков 61 и 62 соответст

20

25

30

35

и 21 памяти. Далее устройство работа- 15 венно, таким образом с выхода счет- ет так же(как и при определении первого числового множителя. При этом на начальный адрес на входе узла 20 . памяти сдвинут ровно на по сравнению с предыдущим, как того требуют выражения (2а) и (26).

Далее устройство работает так же как и при. формировании первого вектора.

Количество числовых множителей для данного уравдения всегда равно степени используемого интерполяционного полинома и, кроме того, последний из них представляет собой лишь один сомножитель из трех чисел на умножителе 27 блока 10 интерполяции . как следует из (2а) и (26) . После каждого определения числового множителя происходит сдвиг начального адреса на 1. Таким образом, после определения последнего числового множителя содержимое счетчика 23 равно нулю. В этом единственном случае происходит совпадение импульсов переполнения счетчиков 23 и 24, которое через элемент И 36 .устанавливает в единичное состояние триггер 32 блока 10 интерполяции, снимая разрешение с входа элемента И 39. Это дает возможность сохранить накопленную инфор- ,с мацию в регистре 26. Кроме того, разрешается прохождение через элемент И 34 регенерационной серии импульсов от генератора 1 в счетчики 23 и 25 через элементы ИЛИ 42 и 43 соответственно. К этому моменту в счетчике 25 занесено число импульсов, равное числу числовых множителей, и при прохождении регенерационной серии импульсов до переполнения счетчика 25, которое устанавливает в нулевое состояние триггер 32, в счетчике 23 восстанавливается исходная информация. Устройство оказывается подго40

50

55

чика 61 через дешифратор 65 формируется управляющий сигнал считывания на группу узлов 58 1(1t)- 58 памяти. Поскольку счетчик 60 является счетчиком с изменяемым коэффициентом счета, после переполнения в нем авто матически восстанавливается исходная информация (степень интерполяционного полинома).

Для образования второго слагаемого в правой части выражения (6) каждый из числовых множителей га (. дол жен перемножаться с соответствующими коэффициентами а и векторами из соответствующих узлов 581(w - 58 j,(v.) памяти. При этом для каждого последующего вектора вида (2а) и (26) для последовательности j l,n выборка векторов из группы узлов 58 1(ю - .58 v(k памяти сок ращается на одну группу. Организован это в устройстве следующим образом.

Сигнал переполнения счетчика 60 через соответствующие элементы посту пает на входы счетчиков 61 и 62, им-т пульс переполнения счетчика 61 устанавливает триггер 68 в единичное состояние, разрешая поступление через элемент И 71 и элементы ИЛИ 74 и 75 на входы счетчиков 61 и 62 соот ветственно регенерационной серии импульсов, до переполнения счетчика 62 и установки в единичное состояние триггера 67. При этом в счетчике 61 восстанавливается исходная информация . Поскольку на входе элемента И 70 с единичных выходов триггеров 68 и 67 имеются разрешения, то с выхода блока 12 интегрирования проходит лишь один импульс ГИ2, который устанавливает триггеры 67 и 68 в нулевое состояние и поступает на вход счетчика 61. В результате формирующийся на элементах И 69i(i) - 69q.(-ui

товленным к определению числовых множителей для следующей группы формируемых векторов.

Сигнал об окончании формирования вектора с выхода блока 11 формирования векторов поступает на вход счетчика 60, в котором содержится порядковый номер числового множитечислового множителя импульс переполнения счетчика 60 через элемент И 72 и элементы ИЛИ 74 и 75 поступает на входы счетчиков 61 и 62 соответст0

5

0

5

5 венно, таким образом с выхода счет-

,с

0

0

5

чика 61 через дешифратор 65 формируется управляющий сигнал считывания на группу узлов 58 1(1t)- 58 памяти. Поскольку счетчик 60 является счетчиком с изменяемым коэффициентом счета, после переполнения в нем автоматически восстанавливается исходная информация (степень интерполяционного полинома).

Для образования второго слагаемого в правой части выражения (6) каждый из числовых множителей га (. должен перемножаться с соответствующими коэффициентами а и векторами из соответствующих узлов 581(w - 58 j,(v.) памяти. При этом для каждого последующего вектора вида (2а) и (26) для последовательности j l,n выборка векторов из группы узлов 58 1(ю - .58 v(k памяти сокращается на одну группу. Организовано это в устройстве следующим образом.

Сигнал переполнения счетчика 60 через соответствующие элементы поступает на входы счетчиков 61 и 62, им-т пульс переполнения счетчика 61 устанавливает триггер 68 в единичное состояние, разрешая поступление через элемент И 71 и элементы ИЛИ 74 и 75 на входы счетчиков 61 и 62 соответственно регенерационной серии импульсов, до переполнения счетчика 62 и установки в единичное состояние триггера 67. При этом в счетчике 61 восстанавливается исходная информация . Поскольку на входе элемента И 70 с единичных выходов триггеров 68 и 67 имеются разрешения, то с выхода блока 12 интегрирования проходит лишь один импульс ГИ2, который устанавливает триггеры 67 и 68 в нулевое состояние и поступает на вход счетчика 61. В результате формирующийся на элементах И 69i(i) - 69q.(-ui

10

20

25

управляющий сигнал считывания с выхода счетчика 61 через дешифратор 65

ДЛЯ ИСХОДНОЙ ГРУППЫ УЗЛОВ 58 jj 58 ц, (k) памяти изменяется ровно на единицу по сравнению с предыдущим. Синхронность выборки коэффициентов а исходного уравнения и обращения к узлам 58,ff) -58„/t. соответствующей группы обеспечивается тем, что с выходов счетчика 61 через дешифратор 65 формируются управляющие сигналы считывания, выходы счетчика 62 соединены с адресными входами узла 59 памяти, где предварительно записаны значения коэффициентов.

Выходы счетчика 63, на вход которого поступают импульсы переполнения со счетчика 61, через дешифратор 66 вырабатывают сигналы считывания на элементах И 69 1(-w - 69 (ы для узлов 58 1(k, - 58 , памяти соответствующей группы. Кроме того, выход счетЧика 63 связан с адресным входом узла 22 памяти, где хранятся ступенчатые изображения начальных условий. Импульс переполнения счетчика 63 с выхода блока I2 интегрирования устанавливает триггер 14 в единичное состояние. Этот сигнал свидетельствует о том, что определены все векторы Ф вида (2а) и (2б), число которых равно порядку решаемого дифференциального уравнения.

Сигнал с единичного выхода триггера 14 свидетельствует о том, что определен результирующий вектор для второго слагаемого в правой части выражения (6).

По этому сигналу элементы первого столбца матрицы Т подаются на входы соответствующих умножителей 31 - 3h. Тактовые импульсы ГИЗ поступают на входы счетчиков 13 и 46, в результате чего формируются адреса блока 5 памяти и узла 44 памяти. По ГИ4 происходит считывание значения компонент промежуточного вектора первого слагаемого выражения (6) из выбранной ячейки памяти и запись его в регистр 6. Так как триггер 14 бло- ка 9 управления находится в единичном состоянии, по ГИ5 происходит считывание значений компонент промежуточного вектора второго слагаемого выражения (6). Как и при вычислении , произведения столбца матрицы U Q на вектор , вычисляется произведение столбца матрицы Т 1 на значения компонент промежуточного век-

)5

30

35

40

45

0

тора второго слагаемого в выражении (6) и суммирование их на сумматоре 7 со значениями компонент промежуточного вектора первого слагаемого выражения (6), поскольку запись в ячейку блока 5 памяти происходит по ГИ5. Через п импульсов ГИ5 в ячейках блока 5 памяти хранится результат решения дифференциального уравнения Момент получения результата решения может быть зафиксирован одновременным переполнением счетчиков I3 и 46 соответственно блока 9 управления и 5 блока И формирования векторов.

Формула изобретения

0

5

,

0

5

0

5

I. Устройство для решения линейных дифференциальных уравнений, содержащее с первого по р-й сдвигающие регистры (где р - разрядность переменных), с первого по n-й умножители (где п - число шагов осреднения), первый сумматор и генератор тактовых импульсов, причем первый выход генератора тактовых импульсов подключен к входам сдвига сдвигающих регистров с первого по р-I, выходы с первого по n-й i-ro (...,p) сдвигающего регистра подключены к i-м входам соответственно умножителей с первого по п-й,(р+1)-е входы умножителей с первого по n-й подключены соответственно к входам с первого по п-й столбца определяющей матрицы устройства, выходы умножителей с первого по n-й подключены соответственно к входам с первого по n-й первого сумматора, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет решения линейных дифференциальных уравнений высокого порядка, в него введены с первого по р-й элементы ИЛИ, второй сумматор, регистр, блок памяти, блок управления, блок интерполяции, блок формирования векторов и блок интегрирования, при этом с первого по р-й входы значений ступенчатого изображения устройства подключены соответственно к первым входам элементов ИЛИ с первого по р-й, выходы которых подключены соответственно к информационным входам сдвигающих регистров с первого по р-й, вход шага осреднения устройства подключен к первому информационному входу блока интерполяции, вход запуска устройстна подключен к входу запуска блока управления, первый выход генератора тактовых импульсов подключен к первому входу синхронизации блока интер

полиции, второй выход генератора тактовых импульсов подключен к второму входу синхронизации блока интерполяции и первому входу синхронизации блока интегрирования, третий выход генератора тактовых импульсов подключен к входу синхронизации блока формирования векторов и первому входу синхронизации блока управления, четвертый выход генердтора тактовых импульсов подключен к второму входу синхронизации блока управления, входу записи регистра и входу чтения блока памяти, пятый выход генератора тактовых импульсов подключен к треть ему входу синхронизации блока управления и входу записи блока памяти, выход первого сумматора подключен к первому входу второго сумматора, выход которого подключен к информацией- 25 входу счетчика и второму входу треть-:

35

ному входу блока памяти, выход которого подключен к выходу результата устройства и информационному входу регистра, выход которого подключен к второму входу второго сумматора, пер- 30 вый выход блока интегрирования подключен к входу режима блока управления, с первого по пятый выходы которого подключены соответственно к выходу признака результирующего вектора устройства, адресному входу блока памяти, первому и второму управляющим входам блока формирования векторов и входу запуска генератора тактовых импульсов, шестой выход которого до подключен к третьему входу синхронизации блока интерполяции и второму входу синхронизации блока интегрирования, первый, второй и третий выходы блока интерполяции подключены соот- дс ветственно к первому, второму информационным входам блока формирования векторов и первому информационному входу блока интегрирования, выходы с второго по (я+3)-й которого подключены соответственно к информационным входам с второго по (q+3)-n блока интерполяции, (q+4)-ft информационный вход которого подключен к первому выходу блока формирования векторов, выходы с второго по (р-Н)-й которого подключены соответственно к вторым входам элементов ИЛИ с первого по р-й,(р+2)-й выход блока формиро50

55

его элемента И, третий синхровход блока управления подключен к вторым входам первого и второго элементов И, информационный выход счетчика и выход второго элемента И подключены соответственно к второму и третьему выходам блока управления, выходы первого и третьего элементов И подключены к входам элемента ИЛИ, выход которого подключен к четвертому ьыходу блока управления, прямой вчход второго триггера подключен к пятому выходу блока управления.

0

вания векторов подключен к второму информационному входу блока интегрирования, выходы которого с (q+4)-ro по (q+7)-ft подключены соответственно к информационным входам с третьего по шестой блока формирования векторов , при этом блок управления содержит счетчик, два триггера, три элемента И и элемент ИЛИ, причем вход запуска блока управления подключен к входу установки в О первого триггера и входу установки в .1 второго триггера, вход режима блока управления подключен к входу установки в 1 первого триггера, прямой выход которого подключен к первому входу первого элемента И и первому выходу блока управления, инверсный выход первого триггера подключен к первым входам второго и третьего элементов И, первый и второй синхровходы блока управления подключены соответственно к счетному

5

0 о с

0

5

его элемента И, третий синхровход блока управления подключен к вторым входам первого и второго элементов И, информационный выход счетчика и выход второго элемента И подключены соответственно к второму и третьему выходам блока управления, выходы первого и третьего элементов И подключены к входам элемента ИЛИ, выход которого подключен к четвертому ьыходу блока управления, прямой вчход второго триггера подключен к пятому выходу блока управления.

19

подключен к входу установки в 1 второго триггера, прямой выход которого подключен к второму входу четвертого элемента И, а инверсный вы1- ход - к вторым входам второго и третьего элементов И и первому входу шестого элемента И, выход которого подключен к первому входу сумматора, выход которого подключен к первому входу седьмого элемента И и информационному входу регистра, выход которого подключен к второму входу сумматора, выход переполнения второго счетчика подключен к входу установки в О второго триггера, информационный выход первого счетчика подключен к входу дешифратора и адресному входу первого узла памяти, выход которого подключен к первому входу умножителя, выход которого подключен к второму входу шестого элемента И, выход дешифратора подключен к первому входу восьмого элемента И, выход которого подключен к третьему входу сумматора, прямой выход первого триггера подключен к третьему входу второго элемента И, выход которого подключен к второму входу первого элемента ИЛИ, входу установки в О первого триггера и второму входу второго элемента ИЛИ, выход первого элемента И подключен к входу записи- считывания регистра, выход третьего элемента И подключен к третьему входу п ервого элемента ИЛИ и счетному входу третьего счетчика, информационный выход которого подключен к первому адресному входу второго узла памяти, выход которого подключен к второму входу умножителя, выход переполнения третьего счетчика подключен к входу установки в 1 третьего триггера, инверсный выход которого подключен к третьему входу третьего элемента И, к второму входу первого элемента И и третьему входу шестого элемента И, инверсный выход первого триггера подключен к четвертому входу шестого элемента И, третьему входу первого элемента И и первому входу девятого элемента И, выход седьмого элемента И подключен к первому выходу блока интерполяции, прямой выход третьего триггера подключен к второму выходу блока интерполяции, четвертому входу второго элемента И, вторым входам пятого и седьмого элементов И, выход девятого элемента

1

10

15

20

25

- 40

7648620

И подключен к третьему выходу блока интерполяции и входу установки в О третьего триггера, первый информационный вход блока интерполяции подключен к третьему входу умножителя, информационные входы с второго по (q+l)-H блока интерполяции подключены соответственно к адресным входам с второго по (q-H)-fl второго узла памяти, (q+2)-u и (q+3)-u информационные входы блока интерполяции подключены соответственно к входу чтения и адресному входу треть-, его узла памяти, выход которого подключен к второму входу восьмого элемента И, (q+4)-u информационный вход блока интерполяции подключен к входу установки в О регистра и к второму входу девятого элемента И.

30

35

45

50

55

вход блока подключен к входу записи регистра и входу чтения узла памяти, выходы с первого по р-й которого подключены соответственно к выходам с второго по (р+1)-й блока и соответственно к информационным входам с первого по р-й регистра, выход которого подключен к второму входу сумматора, вход синхронизации блока подключен к второму входу первого элемента И, выход которого подключен к счетному входу первого счетчика и второму входу второго элемента И, выход которого подключен к счетному входу второго счетчика, информацион- ный выход первого счетчика подключен к адресному входу узла памяти и второму информационному входу коммутатора, выход которого подключен к (р+2)-му выходу блока, выход переполнения первого счетчика подключен к входу установки в О триггера и второму входу элемента ИЛИ, выход элемента НЕ подключен к второму входу третьего элемента И.

выход третьего дешифратора подключен к (q+2)-My входу первого элемента И группы, выходы с второго по q-й третьего дешифратора подключены соответственно к (q+2)-M входам элементов И с второго по q-й и выхо-; дам с второго по (q+l)-u блока интегрирования , выходы элементов И с первого по q-й группы подключены соответственно к входам чтения узлов памяти с первого по q-й, выход узла памяти подключен к (q+4)-My выходу блока, первые выходы узлов памяти

группы подключены к (q+5)-My выходу блока, вторые выходы узлов памяти группы подключены к (q+6)-My выходу блока, третьи выходы узлов памяти группы подключены к (q+7)-My выходу

0 блока интегрирования, прямой выход первого триггера подключен к вторым входам первого и второго элементов И, выход переполнения первого счетчика подключен к первому входу

5 третьего элемента И, выход первого элемента И подключен к первому входу первого элемента ИЛИ и входам установки в О первого и второго триггеров, выход второго элемента И под0 ключей к второму входу первого элемента ИЛИ и первому входу второго элемента ИЛИ, выход которого подключен к счетному входу третьего счетчика, выход переполнения которого

5 подключен к входу установки в 1 второго триггера, инверсный выход которого подключен к третьему входу второго элемента И и второму входу третьего элемента И, выход которого

0 подключен к второму входу второго элемента ИЛИ и третьему входу первого элемента ИЛИ, выход которого подключен к счетному входу четвертого счетчика, информационный выход ко5 торого подключен к входу второго дешифратора, а выход переполнения - к счетному входу второго счетчика и входу установки в 1 первого триггера, инверсный выход которого под- .

Q ключей к входу чтения узла памяти, прямой выход второго триггера, информационный выход и выход переполнения третьего счетчика подключены соответственно к третьему входу пер5 вого элемента И, адресному входу узла памяти и входу установки в I второго триггера.

Фиг.2

Фиг.з

Фиг.Ь

| Урмаев А.С | |||

| Основы моделирования на аналоговых вычислительных машинах,- М.: Наука, 1974 | |||

| Цифровой интегратор | 1980 |

|

SU928351A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-04-30—Публикация

1987-10-08—Подача