(54) УСТРОЙСТВО ПРИОРИТЕТА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приоритета | 1981 |

|

SU960817A1 |

| Устройство для управления прерыванием программ | 1981 |

|

SU978150A1 |

| Устройство приоритета | 1976 |

|

SU634279A1 |

| Устройство приоритета | 1978 |

|

SU822184A1 |

| Устройство для приоритетного подключения источников информации к магистрали | 1979 |

|

SU860073A2 |

| Многоканальное устройство для сопряжения каналов ввода-вывода с внешними устройствами | 1980 |

|

SU868742A1 |

| Устройство приоритета | 1979 |

|

SU802964A1 |

| Устройство приоритета | 1982 |

|

SU1049909A1 |

| Устройство для сопряжения процессоров в мультипроцессорной системе | 1984 |

|

SU1188747A1 |

| Устройство для формирования очереди запросов | 1985 |

|

SU1280630A1 |

i

Изобретение относится к вычислительной технике и может найти применение в автоматизированных системах управления и вычислительных системах.

Известно устройство приоритета содержащее триггеры, элементы ИЛИ-НЕ, и элементы ИЛИ н реализующие функции выбора старшего по приоритету запроса из очереди поступивших запросов .

Недостатсж этото устройства состоит в низкой достоверности, поскольку для правильного функционирования его необходимо, чтобы длительность сигнала запроса была меньше времени его обработки, а формирование импульса сброса обработанного запроса должно осуществляться на предварительном запоминании номера выбранного запроса. При приходе запроса с более высоким приоритетом в устройстве также-возможны сбои из-за помех, образующихся от переходных процессов.

Наиболее близким по сущности технического решения является устройство приоритета, содержащее узлы анализа состояния канала по числу источников лапргхчш, соединенные первым входом с соответствующим входом запроса устройстпа, я порным выходом - с соответствующим выходом идентификации источника запроса устройства, группа входов блокировки каждого узла анализа состояния канала соединена соответственно со вторыми выходами всех бо5 Лее старщих по приоритету узлов анализа состояния канала, элемент ИЛИ, выход которого соединен с первым входом элемента И, выход которого подключеи к управляющему выходу устройства, входы элемента ИЛИ подключены к первым выходам соот10ветствующих узлов анализа состояния канала, элемент НЕ, дополнительные элементы И, дещифратор, элемент задержки н дополнительный элемент ИЛИ, причем входы дещифратора соединены соответственно с входами элемента ИЛИ, инверсный выход

15 дещифратора соединен со вторым входом элемента И, прямой выход дещифратора подключен к выходу неисправности устройства и первому входу дополнительного элемента ИЛИ, выход которого соединен со вторыми

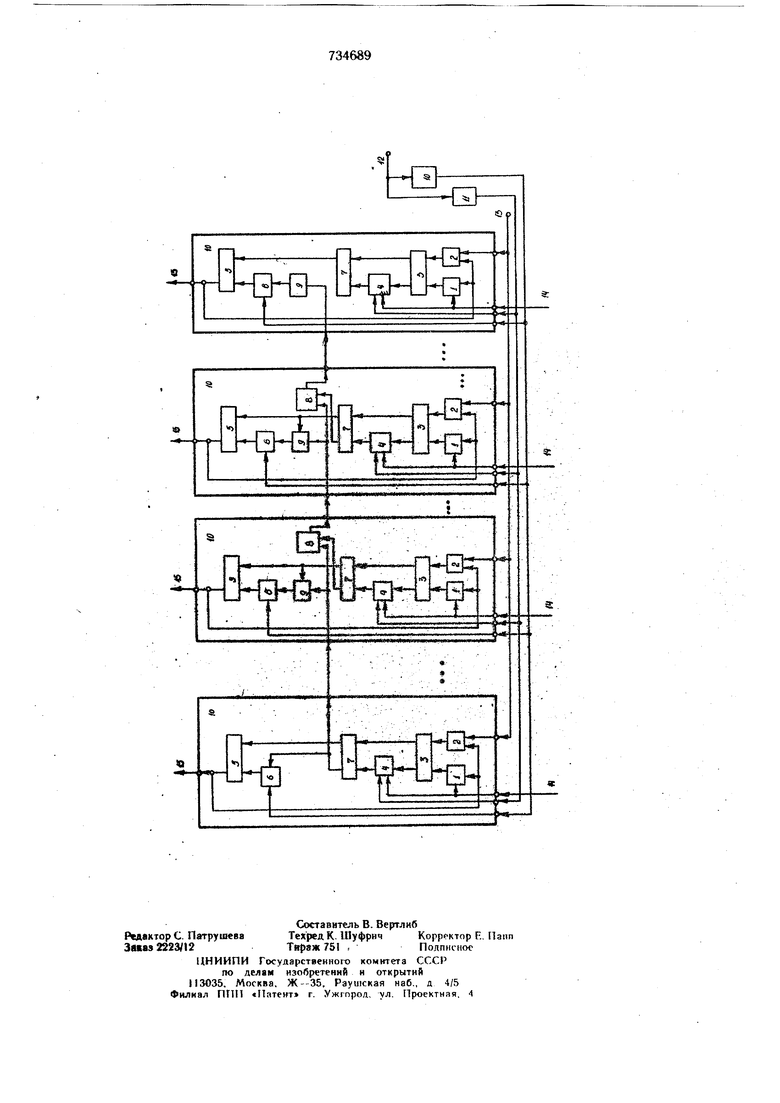

20 входами узлов анализа состояния канала, третьи входы которых соединены Через элемент НЕ с выходом элемента ИЛИ, четвертый вход и первый выход каждого узла анализа состояния канала соединены соотвстственно с выходом и первым входом одноименного дополнительного элемента И, вторые входы дополнительных элементов И подключены ко входу гашения устройства и входу элемента задержки, выход которого связан со вторым входом элемента ИИ, Кроме того, узел анализа состояния канала содержит два триггера и элемент И, причем единичный и нулевой входы первого триггера соединены соответственно с первым и четвертым входами узла, нулевой и единичный выходы первого триггера подклю, чены соответственно ко второму выходу узла и первому входу элемента И, второй вход и выход которого соединены соответственно с третьим входом узла и единичным входом второго триггера, нулевой вход и выход второго триггера подключены соответственно ко второму входу и первому выходу узла, группа входов блокировки которого Соединена с соответствующими входами элемента И. Недостаток этого устройства заключается в низкой достоверности работы устройства, обусловленный жесткими требованиями к поступающим на вход устройства сигналом. Цель изобретения состоит в повыщении достоверности работы устройства. Поставленная цель достигается тем, что в устройстве приоритета, содержащем узлы анализа состояния канала по числу источников запросов, соединенные первым входом с соответствующим входом запроса устройства, первым выходом - с соответствующим выходом идентификации источника запроса устройства, входом сброса - со входом сброса устройства, а вторым входом - с выходом элемента НЕ, и элемент задержки, вход блокировки каждого узла анализа состояния канала соединен с выходом наличия запроса более старщего по приоритету узла анализа состояния канала, входы разрещения узлов анализа состояния канала соединены с выходом элемента задержки, вход которого и вход элемента НЕ соединены с управляющим входом устройства. Кроме того, узел анализа состояния канала содержит триггер защиты, единичный и нулевой входы которого соединены соответственно с выходами первых элементов ИЛИНЕ и И, а единичный и нулевой выходы - соответственно с первым входом второго элемента И и нулевым входом триггера запроса, единичный вход и единичный выход которого соединены соответственно с выходом второго элемента И, вторым выходом подключенного ко второму входу узла, и первому входу элемента ИЛИ, подключенного выходом к выходу наличия запроса, а вторым входом - к первому входу второго элемента ИЛИ-НЕ и выходу блокировки узла, и выходной триггер, соединенный выходом с первым выходом узла и первыми входами первых элементов И и ИЛИ-НЕ, а единичным и нулевым входами - соответственно с выходом третьего элемента И, входы которого подключены соответственно к выходу второго элемента ИЛИ-НЕ и входу разрещения узла, и с нулевым выходом триггера запроса и вторым входом второго элемента ИЛИ-НЕ, второй вход первого элемента ИЛИ-НЕ соединен с третьим входом второго элемента И и первым входом узла, второй вход первого элемента И подключен к первому входу узла. На чертеже представлена блок-схема устройства. Устройство содержит первые элементы И 1 и ИЛИ-НЕ 2, триггер 3 защиты, второй элемент И 4 выходной триггер 5, третий элемент И 6, триггер 7 запроса, элемент ИЛИ 8 и второй элемент ИЛИ-НЕ 9, которые составляют узел 10 анализа состояния канала, элемент 11 задержки, элемент НЕ И, управляющий вход 12, вход 13 сброса устройства, входы 14 запроса и выходы 15 идентификации источника запроса устройства. Устройство работает следующим образом. В исходном состоянии на единичном входе и выходе каждого триггера 3 присутствует единичный потеницал, а на единичных входе и выходе каждого триггера 7 - нулевые потенциалы. При поступлении сигнала «Запрос на К-й вход 15 устройства на входе триггера 3 К-го узла 10 появляется нулевой потенциал И, вход триггера 3 блокируется. Сигнал «Запрос через второй элемент И 4 поступает на единичный вход триггера 7, с единичного выхода которого единичный потенциал через элемент ИЛИ 8 поступает на первые входы элемента ИЛИ-НЕ 9 узлов 10, имеющих более низкий приоритет. Нулевой потенциал с выхода триггера 7 поступает на второй вход элемента ИЛИ-НЕ 9 своего узла 10 и при отсутствии запрета от сигналов с более высоким приоритетом на входе блокировки узла (первый вход элемента ИЛИ-НЕ 9), преобразуется на его выходе в единичный потенциал и поступает на второй вход элемента И 6. Выбор запроса для обработки происходит при поступлении на управляющий вход 12 устройства сигнала «Обработка запроса. При этом на вторые входы всех узлов 10 поступает нулевой потенциал, блокирующий переключение триггеров 7 и разрещающий запись в выходной триггер 5 старшего по приоритету узла 10, получившего сигнал по входу 14. В результате на выходе К-го элемента И 6 появляется единичный потенциал, поступающий на единичный вход выходного триггера 5, на единичном выходе которого появляется: единичный потеницал, поступающий на выход 15 К-го узла 10. Запрет накопления запросов на время длительности сигнала «Обработка запроса введен для защиты от помехи во время записи запроса с высшим приоритетом в выходной триггер 5. Помеха может возникнуть при приходе нового запроса с более высоким приоритетом. Чтобы избежать потери запросов в период работы устройства при поступлении с.игнала «Обработка запроса, длительность последнего не должна превышать времени записи запроса в выходной триггер 5. С учетом этого -ограничения выдвигается требование и к минимальной длительности сигнала «Запрос. Длительность сигнала «Запрос должна быть не меньше удвоенной величины сигнала «Обработка запроса.

Обработка запроса может проводиться по любому алгоритму и влияния на работу предлагаемого устройства не оказывает.

После обработки запроса с К-го узла 10 на входе 13 появляется импульсный сигнал «Сброс, поступающий на входы элементов И 2 всех узлов 10, опрокидывающий триггер 3 К-го узла 10. На нулевом выходе триггера 3 появляется единичный потенциал, сбрасывающий триггер 7 в исходное состояние, сигналом которого устанавливается в исходное состояние выходной триггер 5 узла 10, запрос которого обработан. Установка триггера 3 в исходное состояние осуществляется либо снятием сигнала «Запрос, если длительность данного сигнала больше времени его обработки, либо установкой в исходное состояние выходного триггера 5.

Длительность импульсного сигнала «Сброс определяется временем опрокидывания, триггеров 3.

Время задержки импульсного сигнала «Обработка запроса элементом задержки 10 определяется длительностью переходных процессов и не должно быть меньше их.

Следует отметить, что узлы 10 состояния канала, установленные на входах 14 наинизшего и наивысшего приоритета могут иметь несколько иную конструкцию. В частности, без ущерба для работы устройства в узле 10 наинизщего приоритета может отсутствовать элемент ИЛИ 8, а в узле 10 наивысшего приоритета - второй элемент ИЛИНЕ 9 и элемент ИЛИ 8 (показаны на чертеже). В этом случае в узле 10 наивысшего приоритета единичный выход триггера 7 должен быть подключен к первому входу третьего элемента И 6 и выходу наличия запроса узла 10.

Таким образом, устройство позволяет исключить возможность ошибочной работы при поступлении запросов старших приоритетов во время переходных процессов выбора их на обработку, что повышает достоверность его работы.

Формула изобретения

входом с соответствующим входом запроса устройства, первым выходом - с соответствующим выходом идентификации источника запроса устройства, входом сброса - со входом сброса устройства, а вторым входом - с выходом элемента НЕ, и элемент

задержки, отличающееся тем, что, с целью повьшения достоверности работы устройства, вход блокировки каждого узла анализа состояния канала соединен с выходом наличия запроса более старшего по приоритету узла анализа состояния канала, входы разрешения узлов анализа состояния канала соединены с выходом элемента задержки вход которого и вход элемента НЕ соединены с управляющим входом устройства.

элемента ИЛИ, подключенного выходом к выходу наличия запроса, а вторым входом - к первому входу второго элемента ИЛИ-НЕ и выходу блокировки узла, и выходной триггер, соединенный выходом с первым выходом узла и первыми сходами первых элементов И и ИЛИ-НЕ, а единичным и нулевым входами - соответственно с выходом третьего элемента И, входы которого подключены соответственно к выходу второго элемента ИЛИ-НЕ и входу разрешения узла, и с

нулевым выходом триггера запроса и вторым входом второго элемента ИЛИ-НЕ, второй вход первого элемента ИЛИ-НЕ соединен с третьим входом второго элемента И и первым входом узла, второй вход первого элемента И подключен к первому входу узла.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1980-05-15—Публикация

1977-12-12—Подача