I

Изобретение относится к вычислительной текнике и может быть использовано в устройствах вычисления спектра по алгоритму быстрого преобразования Фурье (БПФ).

Известно устройство для выполнения быстрого преобразования Фурье, и специализированное арифметическое устройство для операций с комплексными числами 1 и 2.

В этах устройствах все операции над действительными числами выполняются параллельно, чем обеспечивается их высокое быстродействие. Недостатком указанных устройств является большое количество оборудования, так как для каждой арифметической операции применяется отдельный перемножитель и отдельный сумматор.

Наиболее близким к изобретению техническим решением является устройство для быстрого преобразования Фурье, содержащее четыре входных регистра, входы которых являются входами уст-

ройства, блок умножения, сумматор, блок управления, два регистра комплексной весовой функции, коммутатор сомножителей, четыре регистра произведений, коммутатор слагаемых два регистра. слагаемых, причем первый выход блока управления соединен с управляющими аходами блока умножения и сумматора, информационные выходы двух входных регистрров и регистров комплексной весовой

to функции соединены с информационными входами коммутатора сомножителей, управляющий вход которого соединен с вторым выходом блока управления, а информационный выход - с информационным

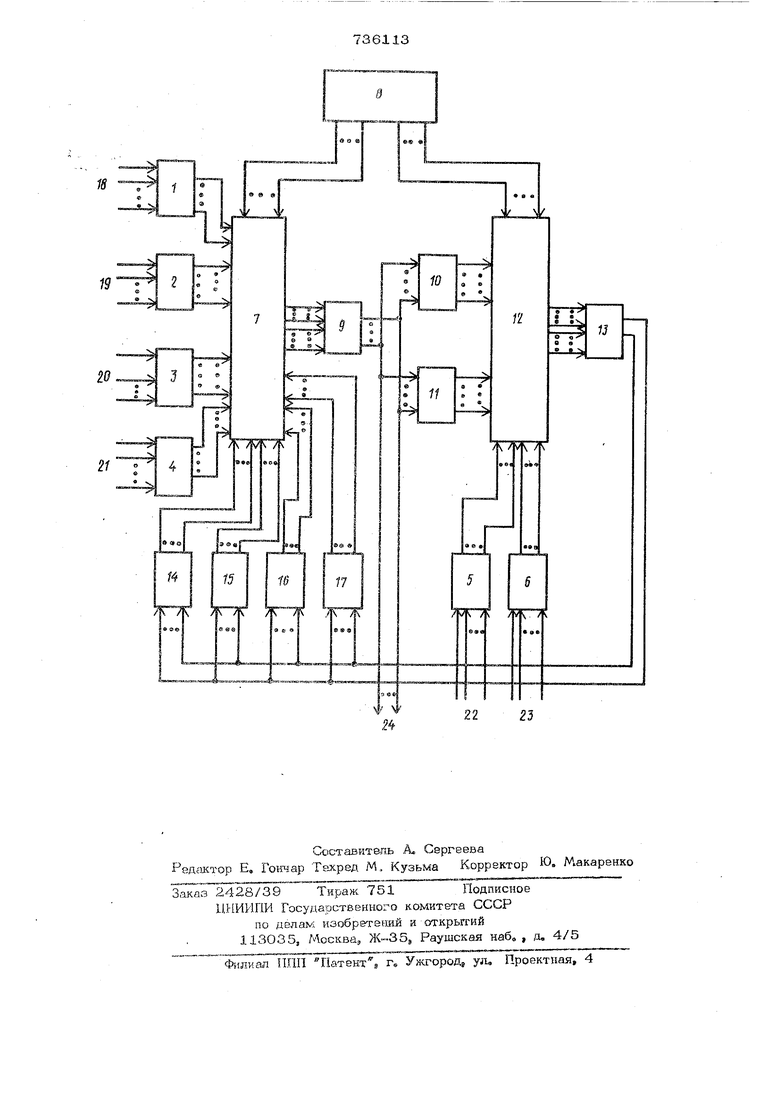

15 входом блока умножения, информационный вьсход блока умножения соединен с входами регистров произведений, выходами соединенных с первыми четырьмя информационными аходами коммутатора слагаемых, информационный выход которого соединен с информационным входом сумматора, и управляющий аход - с третьим выходом блока управления, выход сумматоpa соединен с выходом устройства и с в.ходами регистров слагаемых, выходы которых соединены с пятым и шестым информационными входами коммутатора слагаемых, в:ходы регистров комш ;ексной весовой функции являются входами уст ройства, выходы двух других входных ре гистров соединены соответственно с сед мыми и восьмыми информационшзшси в.ходами коммутатора слагаемыхСЗЛ. Свойственное этому устройству низкое быстродействие объясняется тем, что из восьми тактов работы устройства только в течение двух тактов (третьего и четвертого) работы блок умножения и сумматор работают одновременно. В течение первых двух тактов работы устройства работает один блок умножения5 в течение пятого, шестого, седьмого и восьмого тактов работы устройства , работает один сумматор. Целью изобретения является повышение быстродействия без дополнительных затрат на оборудование. Это достигается тем, что в устройст во для быстрого преобразования Фурье, содержащем четыре входных регистра чисел и два входных регистра комплексной весовой функции входы которых являются входами устройства, блок умножения, сумматор, коммутатор сомножителей, коммутатор слагаемых, четыре регистра произведений, два регистра слагаемых и блок управления, первый выход которого соединен с управл тезщим входом коммутатора слагаемых, второй выход - с управляющим аходом комму- тщ-ора сомножителей, информационные вых ды регистров комплексной весовой функции соединены с первыми двумя информацион ными входами коммутатора сомножителе выход которого соединен с информационHbiM входом блока умножения, а его выход-с входами регистров произведени выходы которых соединены с первы1уш четырьмя информационными входами ком мутатора слагаемых, а выходы входньк регистров одного числа соеди- некь с пятым и шестым входами коммутатора слагаемых, информационньп выход которого соединен с информационным входом сумматора, а выход с;ут/:ма тора соединен с выходом устройства и с входами регистров слагаемых, вьрсоды регистров слагаемых соединены соответ ственно с третьим и четвертым игсфор- мационными аходами коммутатора сомножителей, а информационные выхо,ды 7 34 двул входных регистров другого числа соединены с седьмыл и восьмым инфор- мацион{1ыми входами коммутатора слагаемых. Сущность изобретения заключается в том, что в четырех тактах работы устройства блок умножения и сумматор работают одновременно, что повьшшет быстродействие устройства по сравнению с прототипом па 25%, На чертеже представлена блок-схема устройства,, В его состав входят входные регистры l--4f регистры 5 и 6 комплексной весовой функции, коммутатор слагае- мых 7, блок управления 8, сумматор 9, регистры слагаемых 1О и И, коммутатор сомножителей 12, блок умножения 13, регистры произведений 14-17,, Устройство выполняет след тошие операции: ( Re Ъ - ReC (Re А:,-Т2.е В -Лт С amA:|-3wbjl anB 3wmRe -«e-B -vB6C.(X wK: -anii&). где A-j - первое колгплексное число Ei-i - второе комплексное число C-f - комплексная весовая функция. По входам 18-23 в регистры 1-6 записьшаются исходные данные Re А i , Dvn Л-i j ReB-i , Oni B-i .. Коммутатор слагаемых 7 направляет на сумматор 9 входные данные для получения промежуточных сумм (), { dvuKi-QimBi), которые записываются в регистры слагаемых 10, 11, и выходных величин Rs -i-v-t, Зw , которые подают-, ся на выход 24, Образование этих сумм происходит в -течение первых четырех тактов работы устройства. Во втором, третьем, четвертом и пятом тактах устройства коммутатор сомножителей 12 подает соответственно на блок умножения 13 величины Кес,№еА-яеБ ),атц,(зу 1А -атъ-,аь1Ц-, (R.eA-Ueb;,,iRec-,(3wA;,-3niB;iT для образования промежуточных произведенийRec..(ueA-UeB -),:ivnCAT(,(.3niA -3mfo i, .№eA,;-iie,P,R.,tawAi-aniB), которые записьшаются в регистры произведений 14-17. В пятом и шестом тактах работы устройства коммутатор 7 ела- гаамьк подает промел уточные произведения из регистров произведений 14-17 на сумматор 9 для образования конечных результатов ReU-i ,v3wu , которые подаются на выход 24, Таким образом.

. - 57

в течение второго, третьего, четвертого и пятого тшстов работы устройства сумматор 9 и блок умножения 13 работают одновременно. Тактовые импульсы для обеспечения работы устройства вьщает

блок управления 8.

Таким образом, в предлагаемом устройстве цикл, работы состоит из шести тактов. В четырех тактах работы уст-, ройства (втором, третьем, четвертом и пятом) сумматор и блок умножения работают одновременно. Быстродействие устройства по сравнению с прототипом повышается на 25%, Формула изобретения

Устройство для быстрого преобразования Фурье, содержащее четыре аходных регистра чисел и два входных регистра комплексной весовой фушсции, аходы которых являются аходами устройства, блок умножения, сумматор, KOKtмутатор сомножителей, коммутатор сл&гаемых, четыре регистра произведений, два регистра слагаемых и блок управления, первый выход которого соединен с управляющим входом коммутатора слагаемых, второй выход - с управляющим ахо дом коммутатора сомножителей, информационные выходы регистров комплексной весовой функции соединены с пераы-

136

ми информационными входами коммутатора сомножителей, выход которого соединен с ийформационньтм входом блока умножения, а его выход - с входами регистров п{юизведений, выходы которых соединены с первыми четырьмя информационными входами коммутатора слагаемых, а выходы двух входных регистров одного числа соединены с пятым ишестым входами коммутатора слагаемых, инфорглациовный выход которого соединен с информационным входом сумматора, а выход со цинен с выходом устройства и со входами регистров слагаемых, о т л и ч а е е с я тем, что, с целью повышевия быстродействия, выходы регистров слагаемых соединены соответственно с третьим и четвертым информационными аходами коммутатора сомножителей, а информационные выходы двух входных регистров другого числа соединены с седьмым и восьмым информационными входами коммутатора слагаемых.

Источники информации, принятые во внимание при экспертизе - 1, Патент США № 38O013Q, кл. 235-156, опубл. 1974. .;

2.Авторское свидетельство СССР

№ 399859, кл, QO6F 7/38, 1971,

3.Авторское, свидетельство СССР по заявке Мз 23092О8/18-24,

кл. G06 F 15/34, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выполнения быстрого преобразования фурье | 1976 |

|

SU598085A1 |

| Устройство для быстрого преобразования Фурье | 1981 |

|

SU1042029A1 |

| Устройство для быстрого преобразования Фурье | 1981 |

|

SU995096A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1982 |

|

SU1101835A1 |

| Устройство для быстрого преобразования Фурье | 1982 |

|

SU1101836A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1983 |

|

SU1149275A1 |

| Процессорный элемент устройства для быстрого преобразования Фурье | 1985 |

|

SU1288716A1 |

| Устройство для быстрого преобразования Фурье | 1981 |

|

SU1078433A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1981 |

|

SU972517A1 |

| Устройство для умножения двоичных чисел | 1987 |

|

SU1439579A1 |

Авторы

Даты

1980-05-25—Публикация

1977-11-22—Подача