03

О1

114395

Изобретение относится к вычислительной техш1ке и может быть использовано в ЭВМ для выполнения арифмети ческих действийо

Целью изобретения является повыгне- ние быстродействия при задании сомножителей последовательным кодомо

На фиг о 1 представлена, схема уст

ров 1 и 2, означают номера разрядов мнояотмого и множителя.

Под действием указанных, последовательностей разрядов множимого и множителя на выходах элементов И 4 и 3 первой и второй групп формируются последовательности конъюнкций, отображенных на соответствующих вре

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения двоичных чисел | 1988 |

|

SU1509877A1 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1532918A1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1765839A1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1711152A1 |

| Устройство для возведения в квадрат | 1987 |

|

SU1451686A1 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1587498A1 |

| Устройство для возведения в квадрат | 1988 |

|

SU1534458A2 |

| Устройство для умножения в избыточном последовательном коде | 1983 |

|

SU1173410A1 |

| Вычислительное устройство | 1988 |

|

SU1647553A1 |

| Устройство для умножения | 1991 |

|

SU1807481A1 |

Изобретение относится к арифметическим устройствам цифровых вычислительных машин и позволяет вычислять произведения двоичных чисел в последовательном коде при последовательном приеме сомножителейо Целью изобретения является повьаиение быстродействия при задании сомножителей последовательным кодом Устройство для умножения двоичных: чисел содержит регистр 1 множимого и регистр 2 множителя, в которые в последовательном коде вдвигаются сомножители, элементы И 4, 3 первой и второй групп, формирующие последовательности конъюнкций с весовыми функциями 2, 2, 2 00D соответственно, первьй и BTOpof одноразрядные сумматоры 6 и 5 и регистры 7 группы, которые суммируют в каждом такте конъюнкции, имеющие одинаковые весовые функции соответственно с нечетными и четными значениями степени k О, 1 о«. о Коммутатор 8 подключает на выход устройства разряды произведения с выхода суммы второго и первого сумматоров 5 и 6 в первых и вторых половинах тактов соответственно 2 ил.

ройства для умножения двоичных чисел; 0 менных диаграммах двуразрядными кодами, первьй и второй разряды которых являются соответственно разрядами множимого и множителя, перемножаемыми на элементах И групп.

При этом на выходах элементов

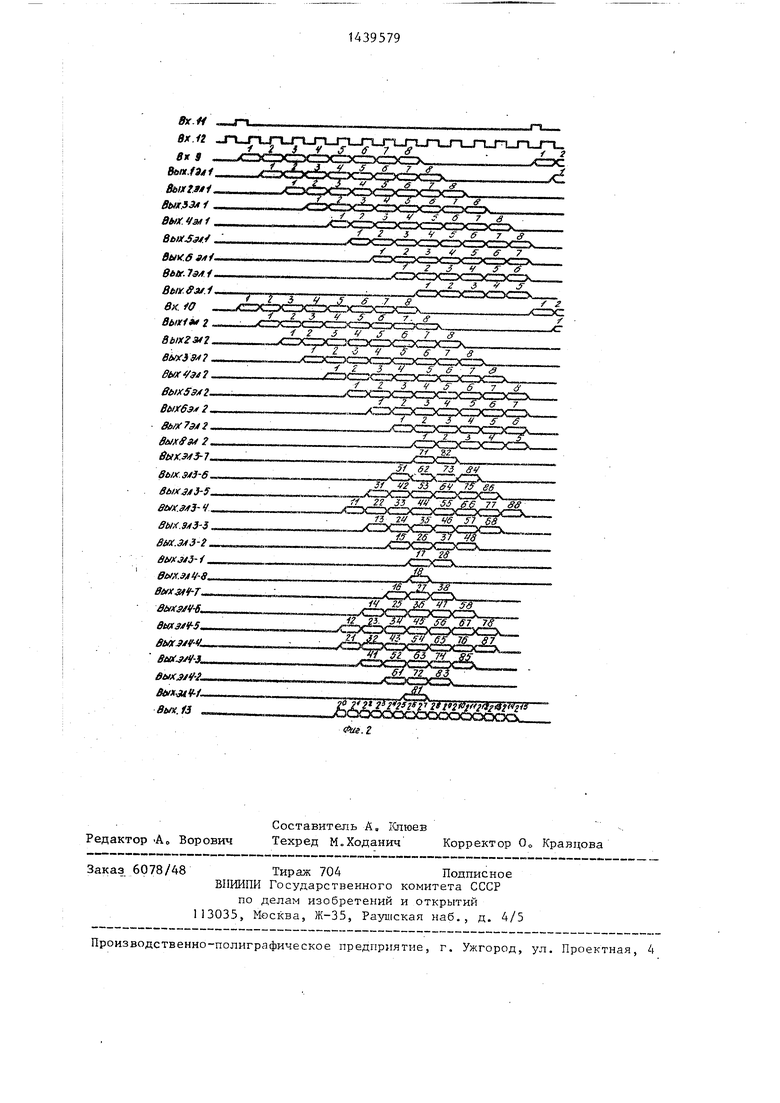

на фиг о 2 временная диаграмма рабе-, ты устройства для у п ожегщя двоичных чисел с,

Устройство {фиг о 1) содержит регистр t множимого, регистр 2 множи- 15

теляз вторую грзщпу элементов И З- , 3-25 ., первую грзшпу элементов И 4-15, 4-2у .оэ 4-8,, второй одноразрядный сз №1атор 5, первьй одно- ;разрядньй сумматор б, регистры 7-1 и 7-2 группы, Коммутатор 8 вход 9 мнолдамого устройстваJ вход 10 множителя устройстваJ вход 11 сброса устройства, тактовьй вход 12 устройства и выход- 13 устройстваS,

Устройство (фиг о 1) работает сле- ДУЮ1Д1-Ш образом

На тактовьй вход 12 устройства поступают сжкроимдульеы (СИ) типа, меандр, тактирующие рабо ру устройства о

На входы 9 и 10 множимого и мноаш- теля устройства с частотой следования СИ поступают в последовательном коде разр51ды, начиная с первого млад ttierо множимого и множителя соответственно;,

На вход 11 сброса устройства поступает импульс 5 сопровожда1ся1;ий со- множители Этот импульс сбрасьшает в ноль регистры 1 и 2 множимого и мноркителяэ ,а та1сже регистры 7--1 и группы

Под действием СИ, поступаюгцих на входы управления сдвигом регистров 1 и 2 множимого и множителя, разряды множимого и множителя продвигаются в каждом такте в регистрах 1 и 2 на одну позипкю в сторону старших разрядов о

При этом на выходах разрядов регистров 1 и 2 множимого и множителя формируются последовательности разрядов множимого и множителя в соответствии ,с временными диаграммами (фиг. 2)„

Числа, указанные на временных дд1аграммах выходов разрядов регист-

И , 3-2,- 0,0, 3-7 второй группы формируются конъюнкции с весовыми функциями 2°5 2., о ,, 2, а на выходах элементов И 4-1, 4-2, ..о, 20 первой группы формируются конъюнкции с весовыми функциями 2, 2,

25

40

45

50

55

2

ikfk о, 1

30

. На втором одноразрядном суш-ито- ре 5 складываются конъюнкции, имеющие одинаковые в такте весовые функций с четным значением k, а также сигналы с выходов четных разрядов переносов сумматора 5, задержанные на регистрах 7 грзшпы, и сигналы с выходов нечетных разрядов переносов сумматора 6, задержанные на регистрах 7 грзшпЫо

На первом одноразрядном сумматоре 6 складьюаются конъюнкции, имеюидае одинаковые в такте весовые функции с нечетным значением k, а также сигнал с выхода первого разряда переноса сумматора 5, сигналы с выходов нечетных разрядов переносов сумматора 5, задер жанные на регистрах 7 группы, и сигналы с выходов четных разрядов переносов сумматора 6., задержанные на регистрах группы .7 о

Сигналы с выходов суммы второго и -первого одноразрядных сумматоров 5 и б поступают соответственно на первьй и второй информационные входы коммутатора 8, который под действием СИ подключает указанные сигналы на выход 13 устройства соответственно в первых и вторых половинах тактов .

Таким образом, с выхода 13 устройства с удвоенной частотой следова шя СИ С1шмается последовательньй код произведения, причем в первых и вторых половинах тактов вырабатываются разряды произведения, имеюпще весо- вые функции с четными и нечетными значениями k (значения весовых функИ , 3-2,- 0,0, 3-7 второй группы формируются конъюнкции с весовыми функциями 2°5 2., о ,, 2, а на выходах элементов И 4-1, 4-2, ..о, первой группы формируются конъюнкции с весовыми функциями 2, 2,

2

ikfk о, 1

5

0

5

0

5

0

. На втором одноразрядном суш-ито- ре 5 складываются конъюнкции, имеющие одинаковые в такте весовые функций с четным значением k, а также сигналы с выходов четных разрядов переносов сумматора 5, задержанные на регистрах 7 грзшпы, и сигналы с выходов нечетных разрядов переносов сумматора 6, задержанные на регистрах 7 грзшпЫо

На первом одноразрядном сумматоре 6 складьюаются конъюнкции, имеюидае одинаковые в такте весовые функции с нечетным значением k, а также сигнал с выхода первого разряда переноса сумматора 5, сигналы с выходов нечетных разрядов переносов сумматора 5, задержанные на регистрах 7 группы, и сигналы с выходов четных разрядов переносов сумматора 6., задержанные на регистрах группы .7 о

Сигналы с выходов суммы второго и -первого одноразрядных сумматоров 5 и б поступают соответственно на первьй и второй информационные входы коммутатора 8, который под действием СИ подключает указанные сигналы на выход 13 устройства соответственно в первых и вторых половинах тактов .

Таким образом, с выхода 13 устройства с удвоенной частотой следова шя СИ С1шмается последовательньй код произведения, причем в первых и вторых половинах тактов вырабатываются разряды произведения, имеюпще весо- вые функции с четными и нечетными значениями k (значения весовых функ1439579

одноразрядного сумматора, отличающееся тем, что, с целью повышения быстродействия задании сомножителей последовательным кодом, оно содержит коммутатор, причем второй вход i-го элемента И первой группы соединен с выходом (9-i)ro разряда регистра множимого (i 1-8), вто -|Q рой вход j-TO элемента И второй группы соединен с выходом (9-j)-ro разряда регистра множителя (j 1-7), входы сброса регистров гшожимого и множителя, а также входы сброса регист- 15 ров группы объединены между собой и под1шючены к входу сброса устройства, управляющий вход кoм гyтaтopa соединен с тактовым входом устройства, выход которого соединен с выходом ком- 20 мутатора, первьпЧ и второй информационные входы которого соединены соответственно, с выходами суммы второго и первого одноразряд1- ых сумматоров, выходы третьего,, второго и первого раз- 25 рядов переноса первого одноразрядного сумматора и выходы третьего и второго разрядов переноса второго одноразрядного сз мматора соединены соответственно, с входами разрядов с первого по 30 пятый первого регистра группы, выход первого разряда которого соединен с информационным входом второго регистра грзшпы, выход которого соединен с входом восьмого слагаемого второго рой группы, выходы элементов И первой п одноразрядного сумматора, входы давя- группы соединены с входами соответ-того и десятого cлaгae ыx которого

Ствующих слагаемых первого одноразрядного сумматора, выходы элементов И

ПИЙ указаны на временной диаграмме, выхо 13) с,

Для предлагаемого устройства начало вьщачи произведения отстоит от импульса сопровождения сомножителей на пять тактов, а конец вьщачи - на тринадцать тактов, Дополнительньй положительньй эффект по сравнению с известным устройством состоит в сокращении аппаратурных затрат и повышении производительности. Формула изобретения

Устройство для умножения двоичных чисел, содержащее регистр множимого, регистр множителя, две группы элементов И, два одноразрядных сумматора и группу регистров, причем вход пер- .вого разряда регистра мнолсимого и вход первого разряда регистра множителя подключены к входам множимого и множителя устройства соответственно, вход управления сдвигом регистра множителя объединен,с входами записи регистров группы и с управления сдвигом регистра множимого и подключен к тактовому входу устройства первые входы элементов И первой груп пы соединены с выходами соответствующих разрядов регистра множителя, выходы разрядов, кроме младшего, регистра мноясимого соединены соответственно с первыми входами элементов И втовторой группы соединены с входами со

соединены соответственно с выходами третьего и пятого разрядов первого регистра группы, выход четвертого и ответствзпощих слагаемых второго одно- 40 второго разрядов которого .соединены разрядного сумматора, выход первогосоответственно, с входами десятого

разряда переноса которого соединени одиннадцатого слагаемых первого

с входом девятого слагаемого первогоодноразрядного сумматора.

ftr.«V в If. It вя S

BuM. Bbixtati ЫХ.ЗЛ1 /, Ш Vat f. BtiixSM.

Bti.eail в1 кЛэл1. Bbn.Sa/.i

ex. iO - с:1ХЦЭСГх зс :х™х™х л

BuxiMj 8ыхгм2. вЫ) fftfjf yf.

в1 1Х5э/(2- BttfJfff-S 2

В1 /х7элг.

ых. . . ых.элЗ- У . №(.3jl3-2 быхлЗ- i

.ЭЛЧ-в.

ыхзлЧ-Т. вб/хэ Ч-6. StffS f-S. KTjVf-V. AWJvy-A . BbixMV-i. 8ЫУ.13

i г

-.XnrXL-.-. 3 V S б

H

4

--y--)f

3V .T у .

tf

6

л

f

.

7

4 6 7 S

--y--)

3V 5 ff 7 S .T . 4 - (5- 7

tf/ г5

| Устройство для умножения чисел | 1979 |

|

SU817702A1 |

| Устройство для умножения | 1984 |

|

SU1203512A1 |

Авторы

Даты

1988-11-23—Публикация

1987-02-16—Подача