1

Изобретение относится к импульсной те.хнике и может быть использовано для организации син.хронной работы каналов резервированного цифрового ко1мплекса.

Известны резервированные делители импульсов 1 и 2.

Первое из известнь х устройств содержит делитель частоты, элемент памяти, мажоритарный элемент, сигнал с выхода которого непосредственно используется для синхронизации работы делителей различных каналов 1 .

Недостатком известного устройства является влияние одного отказа на синхронный пуск делителей при условии использования в качестве источников счетных импульсов автономных для каждого канала генераторов.

Наиболее близким по технической сущности является резервированный делительформирователь, содержащий счетчик на D-триггерах, RS-триггер, элемент задержки на базе D-триггера, подключенного через мажоритарный элемент и элемент ИЛИ к запускающему входу счетчика 2.

Недостатком известного устройства является нарушение синхронного пуска счетчиков при одном отказе: нанри.мер, отказ одного из каналов фиксируется на входе мажоритарных элементов как разрешающий сигнал для прохождения импульсов, снимаемых с элемента задержки собственного и со5 селнего каналов. В этом случае мажоритарный элемент не может блокировать одну возможную неисправность, источники счетных импульсов в каждом канале - независимые асинхронные генераторы.

Цель изобретения - повышение надежно ности работы устройств.

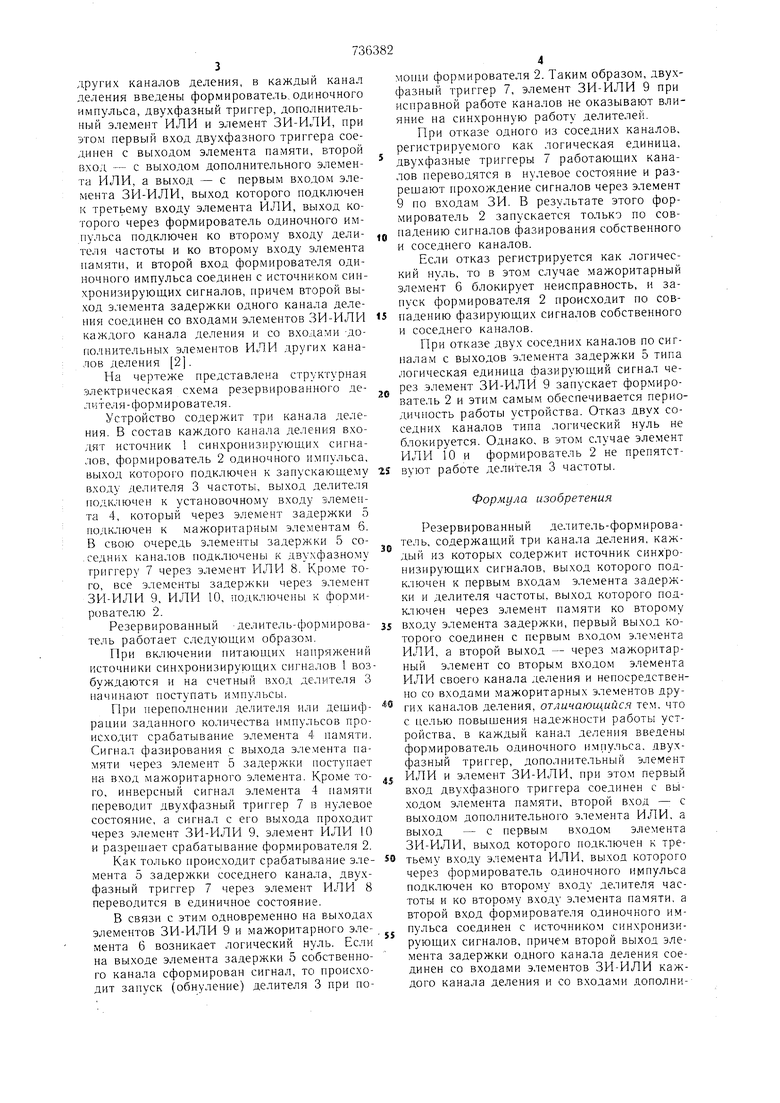

Поставленная цель достигается тем, что в резервированном делителе-формирователе, содержащем три канала деления, каждый из которых содержит источник синхронизирующих сигналов, выход которого подключен к первым входам элемента задержки и делителя частоты, выход которого подключен через элемент памяти ко второму входу элемента задержки, первый выход которого соединен с первым входом элемента ИЛИ, а второй выход - через мажоритарный элемент со вторым входом элемента ИЛИ своего канала деления и непосредственно со входами мажоритарных элементов других каналов деления, в каждый канал деления введены формирователь, одиночного импульса, двухфазный триггер, дополнительный элемент ИЛИ и элемент ЗИ-ИЛИ, при этом первый вход двухфазного триггера соединен с выходом элемента памяти, второй вход - с выходом дополнительного элемента ИЛИ, а выход - с первым входом элемента ЗИ-ИЛИ, выход которого подключен к третьему входу элемента ИЛИ, выход которого через формирователь одиночного импульса подключен ко второму входу делителя частоты и ко второму входу элемента памяти, и второй вход формирователя одиночного импульса соединен с источником синхронизирующих сигналов, причем второй выход элемента задержки одного канала деления соединен со входами элементов ЗИ-ИЛИ каждого канала деления и со входами -дополнительных элементов ИЛИ других каналов деления 2. На че)теже представлена структурная электрическая схема резервированного делителя-формирователя. Устройство содержит три канала деления. В состав каждого канала деления входят источник 1 синхронизнруюодих сигналов, формирователь 2 одиночного импульса, выход которого подключен к запускающему входу ;:|,елителя 3 частоты, выход делителя подключен к установочному входу элемента 4, который через элемент задержки 5 подключен к мажоритарным элементам 6. В свою очередь элементы задержки 5 со.седних каналов подключены к двухфазному триггеру 7 через элемент ИЛИ 8. Кроме того, все элементы задержки через элемент ЗИ-ИоТИ 9, ИЛИ 10, подключены к формирователю 2. Резервированный делитель-формирователь работает следующим образом. Ири включении питаюн.1их напряжений источники синхронизирующих сигналов 1 воз буждаются и на счетный вход делителя 3 начинают поступать импульс)1. При переполнении делителя или дешифрации заданного количества импульсов происходит срабатывание элемента 4 намяти. Сигнал фазирования с выхода элемента памяти через элемент 5 задержки поступает на вход мажоритарного элемента. Кроме того, инверсный сигнал элемента 4 памяти переводит двухфазный триггер 7 в нулевое состояние, а сигнал с его выхода проходит через элемент ЗИ-ИЛИ 9, элемент ИЛИ 10 и разрешает срабатывание формирователя 2. Как только ироисходит срабатывание элемеита 5 задержки соседнего канала, двухфазный триггер 7 через элемент ИЛИ 8 переводится в единичное состояние. Б связи с этим одновременно на выходах элементов ЗИ-ИЛИ 9 и мажоритарного элемента 6 возникает логический нуль. Если на выходе элемента задержки 5 собственного канала сформирован сигнал, то происходит запуск (обнуление) делителя 3 при поMonui формирователя 2. Таким образом, двухфазный триггер 7, элемент ЗИ-ИЛИ 9 при исправной работе каналоЕ не оказывают влияние на синхронную работу делителей. При отказе одного из соседних каналов, регистрируемого как логическая единица, двухфазные триггеры 7 работающих каналов переводятся в нулевое состояние и разрещают ирохождение сигналов через элемент 9 по входам ЗИ. В результате этого формирователь 2 запускается только но совпадению сигналов фазирования собственного и соседнего каналов. Если отказ регистрируется как логический нуль, то в этом случае мажоритарный элемент 6 блокирует неисправность, и запуск формирователя 2 происходит по совпадению фазирующих сигналов собственного и соседнего каналов. При отказе двух соседних каналов по сигналам с выходов элемента задержки 5 типа логическая единица фазирующий сигнал через элемент ЗИ-ИЛЙ 9 запускает формирователь 2 и этим самым обеспечивается периодичность работы устройства. Отказ двух соседних каналов тина логический нуль не блокируется. Однако, в этом случае элемент ИЛИ 10 и формирователь 2 не препятствуют работе делителя 3 частоты. Формула изобретения Резервированный делитель-формирователь, содержащий три канала деления, каждый из которых содержит источник синхронизирующих сигналов, выход которого подключен к первым входам элемента задержки и делителя частоты, выход которого подключен через элемент памяти ко второму входу элемента задержки, первый выход которого соединен с первым входом элемента ИЛИ, а второй выход - через мажоритарный элемент со вторым входом э,темента ИЛИ своего канала деления и непосредственно со входами мажоритарных элементов других каналов деления, отличающийся тем, что с нелью повышения надежности работы устройства, в каждый канал деления введены формирователь одиночного импульса, двухфазный триггер, дополнительный элемент ИЛИ и элемент ЗИ-ИЛИ, при этом первый вход дт,вухфазного триггера соединен с выходом элемента памяти, второй вход - с выходом дополнительного элемента ИЛИ, а выход - с первым входом элемента ЗИ-ИЛИ, выход которого подключен к третьему входу элемента ИЛИ, выход которого через формирователь одиночного импульса подключен ко второму входу делителя частоты и ко второму ВХОД} элемента памяти, а второй вх.од формирователя одиночного импульса соединен с источником синхронизирующих сигналов, причем второй выход элемента задержки одного канала деления соединен со входами элементов ЗИ-ИЛИ каждого канала деления и со входами дополнительных элементов ИЛИ других каналов деления.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 427480, кл. Н 03 К 23/02, 1974.

2.Авторское свидетельство СССР

№ 477545, кл. Н 03 К 23/02, 1975 (прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный генератор синхроимпульсов | 1981 |

|

SU1008931A1 |

| Резервированное многоканальное устройство | 1981 |

|

SU1058098A1 |

| Резервированное многоканальное устройство для формирования тактовых импульсов | 1978 |

|

SU767764A1 |

| Резервированный генератор импульсов | 1978 |

|

SU743245A1 |

| Резервированнный генератор импульсов | 1978 |

|

SU866800A2 |

| Резервированный генератор импульсов | 1982 |

|

SU1102066A2 |

| Резервированный формирователь тактовых импульсов | 1977 |

|

SU632108A1 |

| Резервированное многоканальное устройство для формирования тактовых импульсов | 1990 |

|

SU1714607A1 |

| Резервированный генератор синхроимпульсов | 1984 |

|

SU1175037A1 |

| САМОКОРРЕКТИРУЮЩИЙСЯ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2036554C1 |

i канал

Авторы

Даты

1980-05-25—Публикация

1977-12-06—Подача