Изобретение относится к радиоэлектронным устройствам и устройствам автоматики и может найти применение в система} передачи данных дискретных сообщений, цифровых комплексах с резервированием. Известны резервированные устройст а, содержащие резервированный формирователь импульсов и в каждо кансиле автономный задающий генератор. Для обеспечения принципа ремон топригодности каналы известных устройств выполняют как разъемные конструктивные единицы. Объединение каналов между собой осуществляют пр помощи приемопередающих трактов, включающих в свой состав передакицие устройства для работы на линию связи и приемные устройства для согласования линии связи с логическими интег альными схемами {. и 2. Недостатком устройств является влияние эадеркек сигналов в приемопередающих трактах на номинальное значение частоты вызсодных сигналов Наиболее близким по технической сущности к предлагаемому является резервированное многоканальное устройство для формирования тактовых импульсов, содержащее в каждом канале резервированного форлирователя импульсов высокочастотный генера ор, подключенный к связанньЕм между собой блоку п мюритета, блоку привязки фазы и нониусному делителю частоты и подключенный через линии связи к аналогичным блокам других кансшов. По этим линиямсвязи осуществляют передачу сигналов, задсшщих.режим, один ведущий, другие ведо№1е кансшы по частоте выходншс сигналов. . В устройстве при помощи резервированного формирователя импульсов получают не перекрьтающиеся во времени последовательности импульсных с 1гналов Ef-B, следуюзшх один за другим в определенном порядке. Первьм следует сигнал Е, он проходит через блоки приоритета, воздействует на блоки привязки фазы, которые вырабатывают сигнал блокировки блоков приоритета и корректируют фазу нониусного делителя частоты з. . Однако влияние тракта по передаче сигнала Е в собственном канале из-за вероятностных характеристик задэржек может вызвать отклонение частоты от нокинёшьного ее значения fl собственном канале, т.е. сигнал, вырабатываемый блоком привязки фазы не подтверждает коэффициент деления 1нониусного делителя младших разря дов частоты а изменяет его. фичем это изменение зависит случайным образом от задержек сигналов в приемо перёдеиощеМ тракте. Цель изобретения - обеспечение независимости номинального значения частоты от задержек сигналов в трактах формирования и передачи синхронизирующих э1гналов. Поставленная цель достигается тем, что резервированное многоканальное устройство/ содержащее в каждом из ); каналов задающий генератор, подключенный к счетному входу формирователя импульсных сигналов, обменные входы и выходы которого соединены соответственно с обменными вмходс1ми и входами формирователей импульсных сигналов других каналов, а выход опорного сигнала формирователя импульсных сигналов подключен к выходу обнуления блока приоритета, в каждом канале содержит Ц-1 согласующих каска.цов, маркер канала и коммутатор, счетный вход которого подключен к выходу опорного сигнали форм11рователя импульсных сигналов, Н входов синхронизации - к соответствующим ;11 выходам синхронизации формирователя импульсных сигналов, вход блокировки - к выходу блока приоритета, информациооные выходы к установочным входам формирователя импульсных сигналов и блока приоритета, информационный вход, соответствукядий номеру канала, к маркеру собственного канала, а n-l других информационных входов коммутатора через согласукнцие каскады других каналов подключены к соответствукзщим выходам синхрони- . зации формирователя импульсных сигналов . 1Чроме того, коммутатор содержит ц блоков контроля и (rt+l)-входовой .элемент ИЛИ, n+1-й вход которого подключен к входу блокировки коммутатора, а каждый из И входов к выходу соответствующего блока контроля, каждый из которых содержит элемент 2 ИЛИ, два элемента совпадения и элемент сравнени.я частот, первый вход которого подключен к счетному входу коммутатора, второй вход - к соответствующему информационному входу коммутатора и входу элемента 2 ИЛИ, выход к второму входу элемента 2 ИЛИ и первому входу первого элемента совпадения, второй вход которого подключен к соответствующему входу синхронизации коммутатора, а выходы элементов 2 ИЛИ и первого элемента совпадения через второй элемент совпадения подключены к выходу блоков контроля. На фиг. 1 представлена блоксхема устройства; на фиг. 2 - схе-. Ма коммутатора; на фиг. 3 - схема формиро вателя импульсных сигналов; на фиг. 4 - схема маркера канала

на фиг. 5 - схема согласующего каскада; на фиг. 6 - схема блока приоритета; на фиг. 7 - схема элемента сравнения частот кбммутатора

Устройство (фиг. 1) содергжит в каждом из трех каналов формирователь 1 импульсных сигналов, задгиощий генератор 2, блок 3 приоритета коммутатор 4, маркер 5 канала и согласукяцие каскады 6. Обменные входы 7 и 8 и обменные выходы 9 и 10 формирователя 1 при помощи линий 11-16 связи объединяют всеформирователи 1 в резервированный формирователь импульсных сигналов, выход 17 опорного сигнала которого подключен к счетному входу 18 коммутатора 4 и входу 19 обнуления блока 3, а выходы 20 - 22 синхронизации соответственно - к входал синхронизации 23 - 25 коммутатора установочный вход 26 - к информационному выходу 27 коммутатора 4 и к установочному входу 28 блока 3 а счетный вход 29 - к выходу генератора 2. Согласующие каскады 6 подключены к соответствующему номеру подключаемого канала, информационным входам коммутатора 4 соседних каналов при помощи линий 30-35 связи, при этом информационные входы, соответствующие собственному номеру канала 36-1, 37-2 38-3, при помощи линий связи 39-41 подключены к соответствующим маркерг1М 5. Выход 42 блока 3 подключен к входу 43 коммутатора 4.

Коммутатор 4 (фиг. 2) содержит (п+1)-входовой элемент ИЛИ 44, блоки 45-1 - 45-3 контроля, каждый из которых включает в свой состав элемент 46 сравнения частот, элемент 2 ИЛИ 47, первый 48 и второй 49 элементы совпадений. В коммутаторе 4 соответствующий информационный вход 36, 37 или 38 подключен к второму входу 50 элемента 46 и первому входу элемента 2 ИЛИ 47, второй вход которого подключен к выходу 51 элемента 46 и первому входу элемента 48, второй вход которого подключен к соответствующему входу 23, 24 или 25, а выход к второму входу второго элемента 49 первый вход которого соединен с входом элемента 2 ИЛИ 47, а выход И-входу элемента ИЛИ 44,д +1-й вход которого соединен с входом 43 блокировки, при этом счетные входы 52 элемента 46 подключены к счетному входу 18 коммутатора 4,

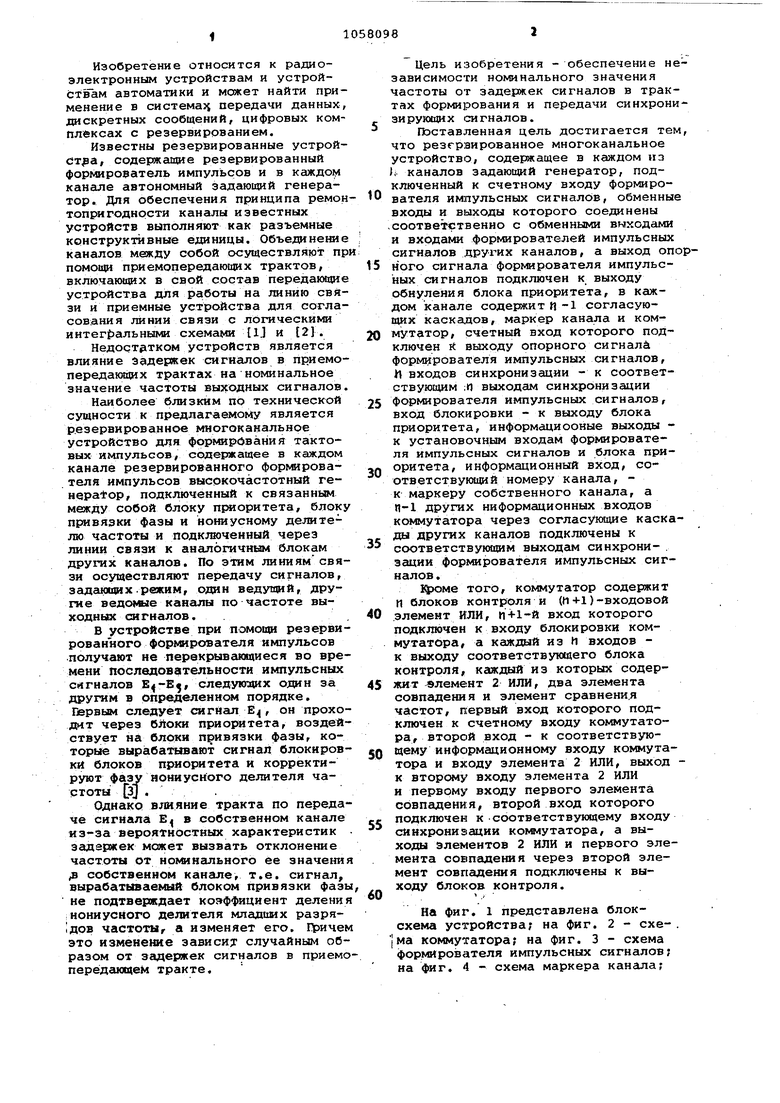

В состав формирователя 1 (фиг.З входят блоки 53-1 и 53-2 формирования одиночного импульса, делители 54 и 55 младших разрядов на триггерах, делитель 56 - 58 старших разрядов на 3 К триггерах, дешифра|торы 59-62 сигналов Ео-Е2 и E-j соответственно, элементы 63-66 задержки на 3 k триггерах, мажоритарный элемент 67, KS-триггер 68 на инверторах 63-1 и 68-2, элементы НЕ 69-74. элементы И-НЕ 75-77 и триггеры 78 и 79. Блок 53 фиг. 3) содержит выходы 80-82, синхронизирукиций вход 83, информационный вход 84.

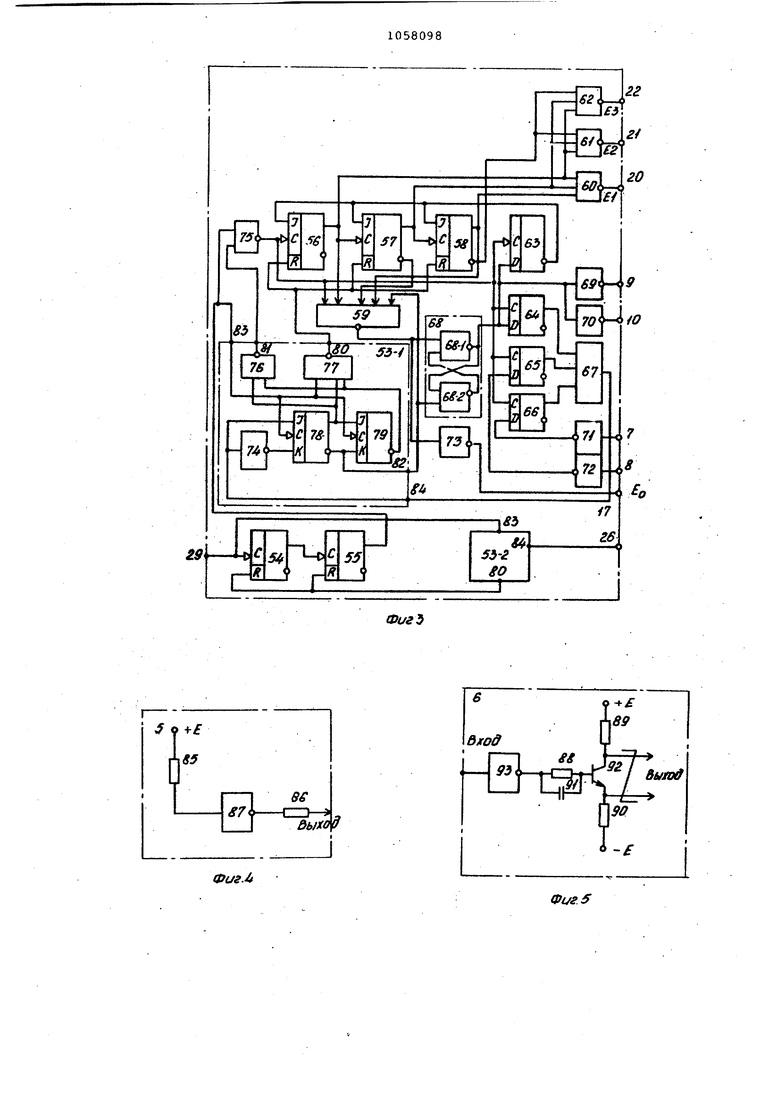

Маркер 5 (фиг. 4) содержит резисторы 85 и 86 и элемент КЕ 87, каскад 6 (фиг. 5) - резисторы 88-90 конденсатор 91, транзистор 92 и элемент НЕ 93, блок 3 (фиг. 6) - резисторы 94 и 95, конденсаторы 96 и 97 и RS-триггер 98, а элемент 46 коммутатора 4 (фиг. 7) состоит из триггеров 99-102, элементов НЕ 103-105 и элемента 2 ИЛИ-НЕ 106.

Синфазирование выходных сигналов устройства осуществляют в два этапа.

На первом этапе осуществляют Синфазирование работы делителей 56- 58 (фиг. 3) при помощи элемента 67, блока 53-1, дешифратора 59 и триггеров 63-66 и 68. Г$)и этбм погрешность расфазировки сигналов между каналами д t(p определяется как nvf, где m - коэффициент делителей 54 и 55 (фиг. 3), а f - частота генратора 2 (фиг. 1).

На втором этапе при помощи блока 3 и коммутатора 4 осуществляют выбор ведущего по частоте канала, а при помощи делителей 54 и 55 и блока 53-2 осуществляют синфазирова ние работы каналов с погрешностью 1/f.

Синфазирование работы делителей 56-58 осуществляют следующим образом.

При пересчете входных сигналов на выходах разрядов делителя набирается определенный код, который дешифрируется дешифратором 59 и запоминается триггером 68. Как только в соседнем канале происходит дешифрация аналогичного кода, во всех каналах срабатывает мажоритарный элемент 67, сигнал с выхода которого относительно сигналов генератора 2 имеет произвольную фазу. Для однозначного приведения всех разрядов делителей частоты используется блок 53-1, в котором вырабатывается импульсный сигнал, время появления которого относительно момента времени срабатывания элемента 67 определяется как О, iti/f.

Формирователь 1 работает следующим образом.

На вход делителей 56-58 с выхода делителя 55 поступает высокочастотный сигнал. наборе на выходах разрядов делителя соответствующей комбинации сигналов срабатывает дешифратор 59, который переводит RS-триггер 68 в единичное состояние. Сигнал с выхода инверI тора 68-1 поступает на элементы ; 64 и 65 и через элементы 69 и 70 навыходы 9 и 10. Через интервал времени, определяемый длительностью периода сигналов на счетных входах элементов 63 и 64, происходит их срабатывание. Элемент 63 блокирует по входам 3 разряды .делителей 56-58, т.е. пересчет импульсов, прекращается. Как только сработает элемент 65 или 66 от сигналов, пришедших с соседних формирователей 1, происходит срабатывание элемента 67. Мажоритарные элементы 67 во всех формирователях 1 срабатывают одновременно и запускают блок 53-1, при помощи которого осуществляется обнуление разрядов делителей 56-58 перевод триггера 68 в нулевое состояние. Далее через интервал времени, определяемый длительностью сигналов, снимаемых с выхода делителя 55, происходит переход триггера 68 в единичное состояние и начинается работа делителей 56-5

Поскольку делитель обнулен, то во всех каналах начинается одновременный счет импульсов. Сигналы дешифрируются в различные моменты времени от начала отсчета, чем и достигается их разнесение во времени.

При. поступлении на вход блока 53-2 формирователя 1 сигналов, например Е первого канала, в первом канале происходит подтверждение состояний разрядов делителя 55 поскрльку сигнал E сформирован в этом же канале, а во втором и третьем каналах происходит корретировка фазы делителя 55 относительно сигналов Е, т.е. частота работы во втором и третьем каналах определяется первым каналом.

Таким образом, на первом этапе синфазирования во всех каналах получают одинаковые по частоте сигналы EQ-E, при этом разноименные сигналы различных канадов не перекрываются между собой во времени, т.е. «имеют временную селекцию.

На втором этапе синфазирования разделенные so времени сигналы используются для управления блоком 3, представляющим собой элемент памяти (триггер 98). фи этом сигналы EQ воздействуют на блок 5 непосредственно, а сигналы через коммутатор 4.

Прохождение сигналов чере коммутатор 4 подчиненр следующим правилам: при совпадении номера сигнала с номером канала последовательность одноименных сигналов поступает на выход коммутатора 4, минуя приемопередающий тракт; если номер канала не совпадает с номером сигнала, то последний проходит через приемопередающий тракт; первым через коммутатор 4 проходит сигнал первого канала, вто,рым - сигнал второго канала и т.д. сигнал, прошедший коммутатор 4 первым, запрещает прохождение всех последующих сигналов.

Элемент 46 (фиг. 7) работает еледующим образом.

При поступлении на вход элемента 46 импульсного сигнала на выходе имеется нулевой потенциал. 15эи поступлении статического потенциала на вход эл€ мента 46 получают на выходе 1.

Изменение состояний элемента.46 осуществляется следующим образом.

На входы 50 и 52 элемента 46 поступают сигналы Е и ЕО соответствено. Сигнал Е проходит через элементы 103 и 104 и устанавливает D-триггеры 99 и 100 в единичное состояние. Сигнал с инверсного выхода триггера 100 разрешает прохождение сигналов Е на выход элемента 106. В связи с этим триггеры 101 и 102 также устанавливаются в единичное состояние. На выходе 51 получают нулевой потенциал, снимаемый с инверсного выхода триггера 102.

При наличии на входе 50 О, т.е. сигнала с маркера 5, на выходе 51 формируется l следующим образом.

На выходе элемента 103 имеется 1, на выходе элемента 106 - О, на выходе элемента 105 - 1, на входе S триггера 100 - О, и сигнал Е переводит триггеры 101 и 102 в нулевое состояние.

Таким образом, информация с выхода ,элемента 46 определяется сигналом на ее входе, который в свою очередь является информационным входом блока 45п, где ti - номер канала, на второй синхронизирующий вход блока 45 поступает одноименный сигнал собственного канала. Если к информационному входу блока 45 и подключен маркер 5, задающий ртатический потенциал на входе, то элемент 46 разрешает прохождение сигнала собственного канала на выход коммутатора 4 через элемент ИЛИ 44, т.е. сигнал собственного канала минует приемопередающий тракт. Если на информационном входе блока контроля имеется импульсный сигнал, то этот сигнал проходит элемент ИЛИ 44.

Рассмотрим прохождение сигналов через коммутатор 4. Допустим, что

логические элементы в составе коммутатора 4 положительные. В этом случае-нулевой логический сигнал, поступивший с маркера 5, переводит элемент 46 в состояние логической единицы, через элемент 48 пропускается последовательность сигналов Е а на выходе элемента 47 имеется разрешающий потенциал для элемента 49. В связи с этим сигнал Е проходит на вход элемента ИЛИ 44. В других блоках контроля поступают на входы элемента ИЛИ 44 соответственно сигналы Ej второго канала и Eg. третьего канала.

Прохождение сигналов соседних каналов осуществляется следующим образом.

Во втором канале на вход 36 при помощи линии связи подаются сигналы Е первого канала. Как отмечалось, при поступлении на элемент 46 импульсного сигнала Е первого канала на выходе этого эле-, мента формируется логический нуль, которьай блокирует элемент 48 и разрешает прохождение сигналов Ej первого канала через элемент 47 и элемент 49 на вход элемента ИЛИ 44.

Таким образом, на входах элемента ИЛИ 44 имеются все последовательности импульсных сигналов

Е -Eg.

Первым по временной диаграмме проходит сигнал Е|, который воздействует на,вход 19 обнуления блока 3 и на вход 26 установки. Блок 3 блокрует элемент 44. Таким образом, на входы установки формирователя 1 действуют во всех каналах сигналы Е. Однако в первом канале они пропускаются через минимальное количество микросхем, минуя межканальные связи

В первом канале сигналы Е| подтверждают внутреннее состояние формирователя 1, во втором и третьем синхронизируют работу формирова- телей 1,задавая им частоту первого канала.

При отключении первого канала :на входах Зб блоков контроля коммутаторов 4 второго и третьего каналов устанавливается логическая единица, при воздействии которой

-(статического уровня) на элемент 46 на выходе получают нулевой потенциал. Пэ входу 36 сигналы отсутству;ют, а прохождение сигналов 23 запрещено. На выходе элемента 49 устанавливается нулевой потенциал, который не влияет на,работу элемента 44. Шскольку сигналы второго каoнала Е2 попадают через элементы 44, выходы 27 на выходы блока 3 раньше, чем сигналы третьего канала, то ведущим становится второй канал, при этом сигналы ЕЗ на вход собственного канала благодаря маркеру 5 по5ступают по кратчайшему тракту и не меняют внут1)еннего состояния формирователя 1 второго канала, т.е. , сигналы ведущего по частоте канала для подтвеЕвкдения состояния дели0телей 55 пропускаются по кратчайшему пути через элементы собственного канала.

Положительный эффект изобретения заключается в устранении влияния

5 тракта по формированию и передаче фазирующего канала на номинальное значение ведущего по частоте канала, т.е. частота фазирукядих сигналов определяется только коэффициентом

0

деления ведущего по частоте канала резервированного формирователя импульсов. Отмеченные свойства устройства снимают ограничения по длине линии связи между каналами, что

5 в свою очередь улучшает технологичные и. эксплуатационные характеристики устройства. Кроме того, предлагаемое устройство не чувствительно к отказс1М в цепях передачи фазирующих сигналов типа О и 1,что

0 повышает адаптивность устройства.

Указаннь1е преимущества достигаются введением передающих устройств, коммутатора и маркера каналов, позво хяющето для фазирующих сигналов

5 собственного канала исключить тракт по передаче фазирующего сигнала и обеспечить кратчайший путь по его передаче с входа на выход, используя элементы.только собствен0ного канала.

9 85

ФигЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный генератор синхроимпульсов | 1984 |

|

SU1175037A1 |

| Резервированнный генератор импульсов | 1978 |

|

SU866800A2 |

| Резервированное многоканальное устройство для формирования тактовых импульсов | 1978 |

|

SU767764A1 |

| Резервированный делитель-формирователь | 1977 |

|

SU736382A1 |

| Резервированный генератор импульсов | 1982 |

|

SU1102066A2 |

| Резервированный генератор импульсов | 1978 |

|

SU743245A1 |

| РАДИОЛУЧЕВОЙ ДАТЧИК ОХРАНЫ | 1992 |

|

RU2079889C1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Устройство для воспроизведения цифровых сигналов с носителя магнитной записи | 1986 |

|

SU1352527A1 |

| Устройство для воспроизведения сигналов цифровой информации с носителя магнитной записи | 1986 |

|

SU1332370A1 |

1. РЕЗЕРВИРОВАННОЕ мнет ОКАНАЛЬНОЙ УСТРОЙСТЮ, содержащее в Ксисдом из п каналов задающий генератор, подключенный к счетному входу формирователя импульсных сигналов, обменные входы и выходы которого соединены соответственно с o6мeнны ФI выxoдa вI и входами формирователей импульсных сигналов других каналов, а выход опорного сигнала формирователя импульсных сигналов подключен к выходу обнуления блока приоритета, отличающееся тем, что, с целью обеспечения независимости номинального значения частоты от задержек в трактах формирования и передачи синхронизирующих сигналов, оно в каждом канале содержит согласующие каскады, маркер канала и коммутатор, счетный вход которого подключен к выходу опорного сигнала формирователя импульсных сигналов, ti входов синхронизации - к соответствующим а выходам синхронизации формирователя импульсных сигналов, вход блокировки - к выходу блока приоритета, информационные выходы к установочным входам формирователей импульсных сигналов и.блока приоритета, информационный вход/ соответствующий номеру канала - к маркеру собственного канала, а п-1 других информационных входов коммутатора через согласующие каскады других каналов подключены к соответствующим канальным выходам синхронизации формирователя импульсных сигналов. 2. Устройство по п. 1, о т л ичающееся тем, что котчмутатор содержит П блоков контроля и (п+1)входовой элемент ИЛИ, (п+1)-й СП вход которого подключен к входу блокировки коммутатора, а кажлый из П входов - к выходу соответствующего блока контроля, каждый из которых содержит элемент 2 ИЛИ, два элемента совпадения и элемент сравнения частот, первый вход которого подключен к счетному входу коммутатора, второй вход - к соответствуел 00 ющему информационному входу коммутатора и входу элемента 2 ИЛИ. выход - к второму входу элемента о ю 00 2 ИЛИ и первому входу первого элемента совпадения, второй вход которого подключен к соответствующему входу синхронизации коммутатора, а выходы элементов 2 ИЛИ и первого элемента совпадения через второй элемент совпадения подключены к выходу блоков контроля.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Резервированный формирователь тактовых импульсов | 1977 |

|

SU632108A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1983-11-30—Публикация

1981-10-30—Подача