(54) ДВОИЧНЫЙ СЧЕТЧИК

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетчик | 1977 |

|

SU660270A1 |

| Способ поиска дефектов в цифровых блоках и устройство для его осуществления | 1985 |

|

SU1260884A1 |

| Устройство для управления тиристорным ключом | 1982 |

|

SU1134089A1 |

| РЕЛЕ ВРЕМЕНИ (С ВЫХОДОМ НА СИМИСТОРЕ) | 1992 |

|

RU2130213C1 |

| Однотактный регистр сдвига | 1979 |

|

SU826424A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU902243A1 |

| Формирователь импульсов | 1978 |

|

SU744942A1 |

| Устройство для управления электродвигателем постоянного тока | 1979 |

|

SU864568A1 |

| Буферный логический элемент и @ л типа | 1981 |

|

SU980289A1 |

| Оптоэлектронный модуль | 1987 |

|

SU1444940A1 |

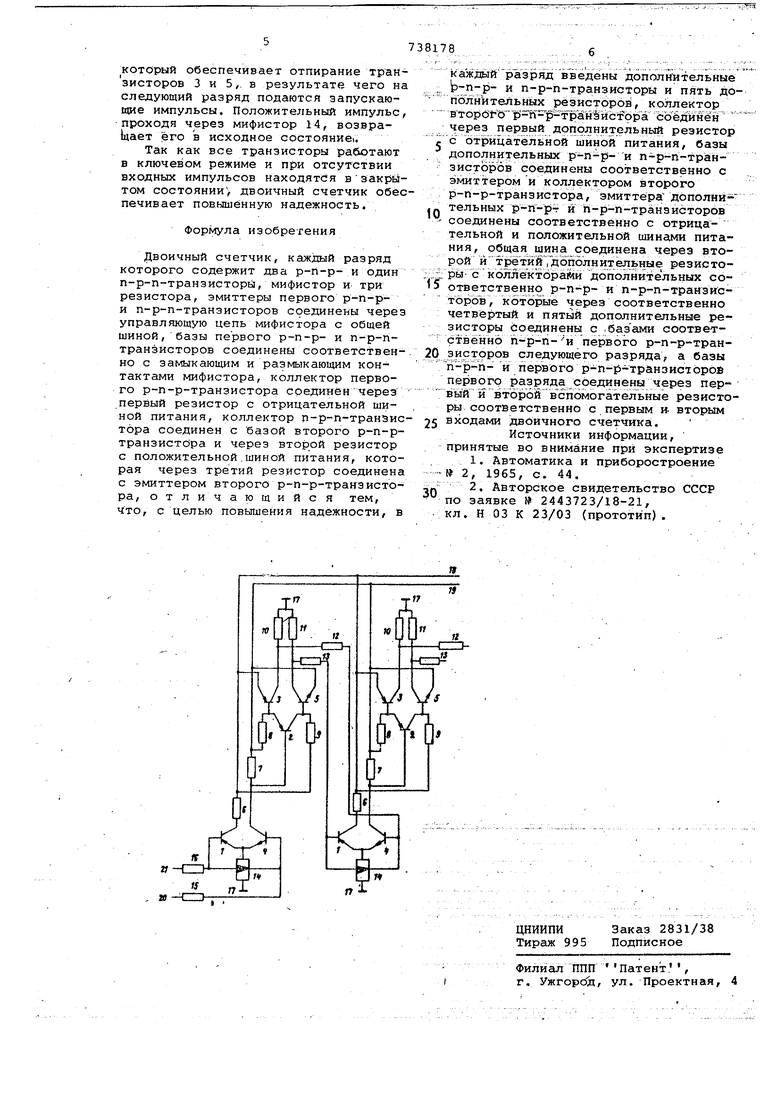

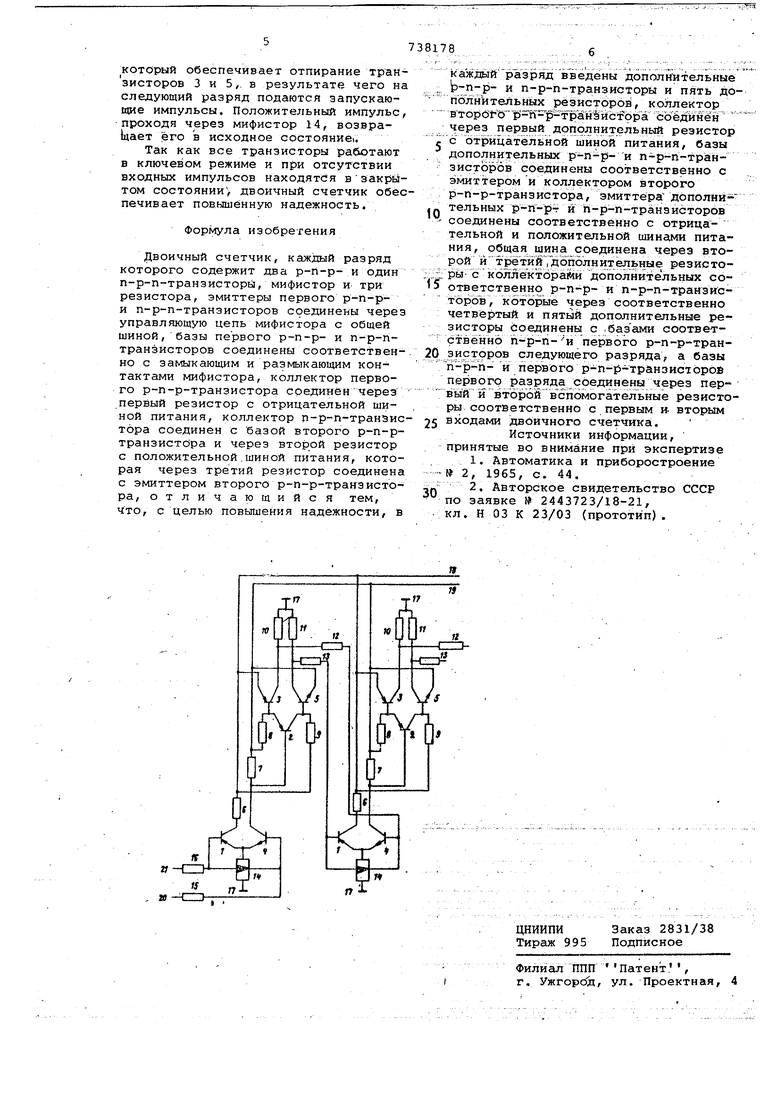

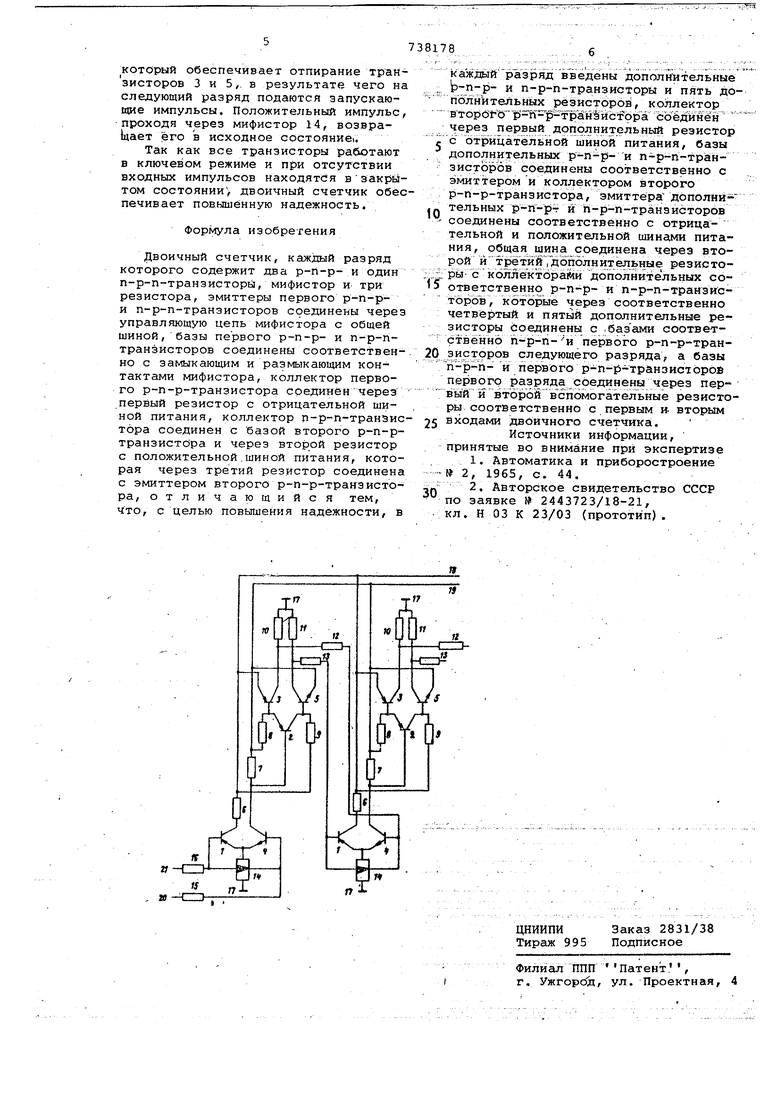

предлагаемый двоичный счетчик предназначен для использования в уст ройствах промышленной автоматики, вы числительных устройствах, работающих в спецрежимах. Известен двоичный счетчик, содержащий р-п-р и п-р-п-транзисторы и элемент памяти в каждом разряде 1. Недостатком этого двоичного счетчика является низкая надежность. Известен также двоичный.счетчик, кг1ждый разряд которого содержит два р-п-р и один п-р-п-транзисторы, мифистор и три резистора, эмиттеры пер вого р-п-р- и п-р-п-транзисторов сое динены через управляющую цепь мифистора с общей шиной, базы первого р-п-р- и п-р-п-транзисторов соединены соответственно с замыкающим и рэзмыкающим контактами мифистора, коллектор первого р-п-р-транзистора сое динен через первый резистор с отрицательной шиной питания, коллектор п-р-п-транзистора соединен с базой второго р-п-р-транзистора и через второй резистор с положительной шиной питания, которая через третий резистор соединена с эмиттером второго |р-п-р-транзистора 2. Недостатком этого счетчика является относительно низкая надежность. Цель изобретения-повышение надежности . Поставленная цель достигается тем, что в двоичный счетчик каждый разряд которого содержит два р-п-р и один п-р-п-транзисторы, мифистор и три резистора, эмиттеры первого р-п-р- и п-р-п-транзисторов соединены через управляющую цепь мифистора с общей шиной, базы первого р-п-р- и п-р-птранзисторов соединены соответственно с замыкающим и размыкающим контактами мифистора, коллектор первого р-п-р-транзистора соединен через пёрвый рёзИстор е Отрицательной шиной питания, коллектор п-р-п--транзистОЦ а соединен с базой второго р-п-р-транзистора и через второй резистор с положительной шиной питания, которая через третий резистор соединена с эмиттером второго р-п-р-транзистора, в каждый разряд введены дополнительные р-п-р- и п-р-п-транзисторы и пять дополнительных резисторов, коллектор второго р-п-р-транзистора соединен Черёз первый дополнительный резистор а отрицательной шиной питания, базы Йрполнительных р-п-р- и п-р-п-тран;эястс 6в соединены Ъбдтветствённо с эмиттером, и котшектором второго р п-р-транзистора, эмиттеры дополнительных р-п-р- и ri-p-n-транзисторов сЬёйинены соответственно с отрицательной И положительной шинаСми питания. Общая шина соединена через второй и третий дополнительные резистоjpHd коллекторами дополнительных ССтвётетвёНИб р-п-р- и h-p- n-транзисторов, которые через соответственно четвертый и пятый дополнительные резисторы соединены с Сазами соответст вёйнб п-р-п- и первого р-п-р-т)ранзис торов следующего разряда, а базы п-р-п- и первого р-п-р-транзисторов первого разряда соединены через первый и второй вспоМОгательные резисто ры соответственно с первым и вторым ;входами двоичного счетчика. Структурная схема двоичного счетчика показана наче ртеже. Двоичный счетчик в каждом разряде содержит три р-п-р-транзистора 1,2,3 и два п-р-п-транзистора 4 и 5, восемь резисторов 6-13 и мифистор 14, а та.кжё вспомогательные резисторы 15 и Те У В к c joifvi раз раде э m т теры п ёр вых р-п-р- и п-р-п-транзисторов 1 и - -еотёдйвейы через управляющую цепь мифистора 14 с общей шиной 17. Базы первых р-п-р- и п-р-п 4 транэйегоро 1 и 4 сб1едййёны еЬатветствёййб с sait Кайщим и размыкающим контактами мифйстора 14. Коллектор -первого р-п-ртранзистора 1 соединен через первый резистор 6 с отрицательной шиной 18 пй гания. Коллектор первого п-р-п-транзистора 4 соединен с базой второго р-п-р-транзистора 2 и через второй резистор 7 с положительной шиной 19 питания, которая через третий резистор 8 соединена с эмиттером второго р-п-р-транзистора 2, Коллектор второго р-п-р-транзистора 2 соединен через четвертый резистЬр 9 с отридательной шиной 18 питания базы трет его р-п-р и второго п-р-п-транзисторов 3 и 5 соединены соответственно с эмиттером и коллектором второго р-п-р-транзистора 2.-Эмиттеры третьего р-п-р- и йторогО n-p-n-тpaнзиc т бpбй coвдинeны соответственно с отрицательной 18 и положительной 19 ши « Вмйп тШйя Общая шина 17 соединена через резисторы 10 и 11 с коллек УОраМи сб6 ветс вённ6 третьего р-п-р и второго п-р-п-транзисторов 3 и 5, 1РГо1(5рае С0Ответственно через резисторы 12 и 13 соедянекы с базами со iswefCTSeKHo первых п-р-п- и р-п-ртранзисторов 4 и 1 Следующего раэрядаУ а баЗы первыхh-jp-ii- и jp-ft-p- транзисторов 4 и 1 первого разряда ;Ьёдий1ены через первый 15 и второй I fi Шпбмбгатёльнйё реэистора совтветртвённо с первым 20 и вторым 21 входами двоичного счетчика. . Двоичный счетчик работает следующим образом. В отсутствии входного сигнала все транзисторы счетчика закрыты. Транзисторы 1 и 4 закрыты нулевыми потенциал.ами на сьоих базах, так как база транзистора 1 заземлена, через резистор 16, если данный разряд в нулевом логическом состоянии, или через контакт мифистора 14, если данный разряд в единичном логическом состоянии. Транзистор 4 э;акрыт, так как его база заземлена, или через размыкающий контакт мифистора 14, если данный разряд находится в состоянии логического нуля, или через резистор 13, если данный разряд находится в единичном логИЧеском состоянии. Транзистор 2 закрыт положительным потенциалом на базе, поданным через резис- тор 7, и транзистор 3 закрыт положительным потенциалом, поданным через резистор 8. Транзистор 5 закрыт потенциалом, поданным через резистор 9. в этом состоянии счетчик устойчив и практически не потребляет энергии от источника питания. Все транзисторы счетчика работают в ключевом режиме и проводят ток только.в моменты действия входных сигналов. Переключение мифисторов 14 происходит после окончания действия, входного сигнала с фиксированной задержкой относительно его нача.ла. ВходньПЛИ импульсами для каждого из разрядов служат положительный и отрицательный импульсы, поступающие от предыдущего разряда через резисторы 12 и 13 соответственно, для всех разрядов, кроме первого, для которого эти импульсы подаются на входы 20 и 21 соответственно и проходят через резисторы 15 и 16 соответственно. При одновременной подаче импульсов положительный импульс оказывается эашунтированным размыкающим контактом мифистора14, если первый разряд находился fe нулевйм состоянии, а отрицательный импульс открывает транзистор. 1. Этот транзистор пропускает импульс тока, который, проходя через мифистор 14, обеспечивает его срабатывание, что Приводит к переключению его контактов. Замыкаюйдай контакт замыкается, шунтируя вход транзистора 1, а размыкающий подготавливает к приходу следующей пары входных импульсов транзистор 4. Разряд переходит в единичное логическое состояние следующая пара входных импульсов приводит к отпиранию транз стора 4. Этообёс печив ает формирование на коллекторе этого транзистора отрицательного импульса перекоса одновременно с входным сигналом. Чтот импуЛьс отпирает транзистор 2,

Авторы

Даты

1980-05-30—Публикация

1977-05-10—Подача