Изобретение относится к микроэлектронике и может быть использовано для обеспечения согласования по логическому уровню микросхем И Л-типа с микросхемами ТТЛ, ДТЛ и т.д.

Известен выходной каскад цифрового логического элемента, изготовленного методом интегральной технологии и использованием инжекции, содержащий три п-р-п-транзистора и два резистора. Первый многоколлекторный п-р-п-транзистор является усилителем тока, первый коллектор второго п-р п-транзистора соединен с базой третьего п-р-п-транзистора и первым выводом резистора, второй вывод которого соединен с источником питания . и выводом второго резистора, второй вывод последнего соединен с коллектором третьего п-р-п-транзистора, эмиттер которого соединен с вторым коллектором второго п-р-п-транзистора и выходной шиной 1.

При изменении полярности входного сигнала второй транзистор закрывается, третий - открывается. При этом нагрузочная способность устройства ограничивается резистором в цепи третьего транзистора. Уменьшение этого резистора приводит к увеличению

потребляемой мощности в режиме короткого замыкания. Кроме того, наличие резисторов в схеме увеличивает площадь, занимаемую устройством на кристалле .

Наиболее близким к предлагаемому является устройство согласования уровня выходного сигнала И Л-элементов, содержащее четыре п-р-п-тран10зистора и три р-п-р-транзистора, причем один из них является источником тока (инжектирующим транзистором) для первого и шестого двухколлекторных п-р-п-транзисторов 2.

15

Однако величина выходного тока. .определяется током базы второго транзистора и его коэффициентом усиления по току, что затрудняет изготовление

20 выходного каскада, так как в случае изготовления второго транзистора с коэффициентом усиления по току большим, чем расчетная величина, в режиме короткого замыкания мощность, выделяемая на нем, превьыает допустимую

25 величину, что может привести к выходу из строя этого транзистора.

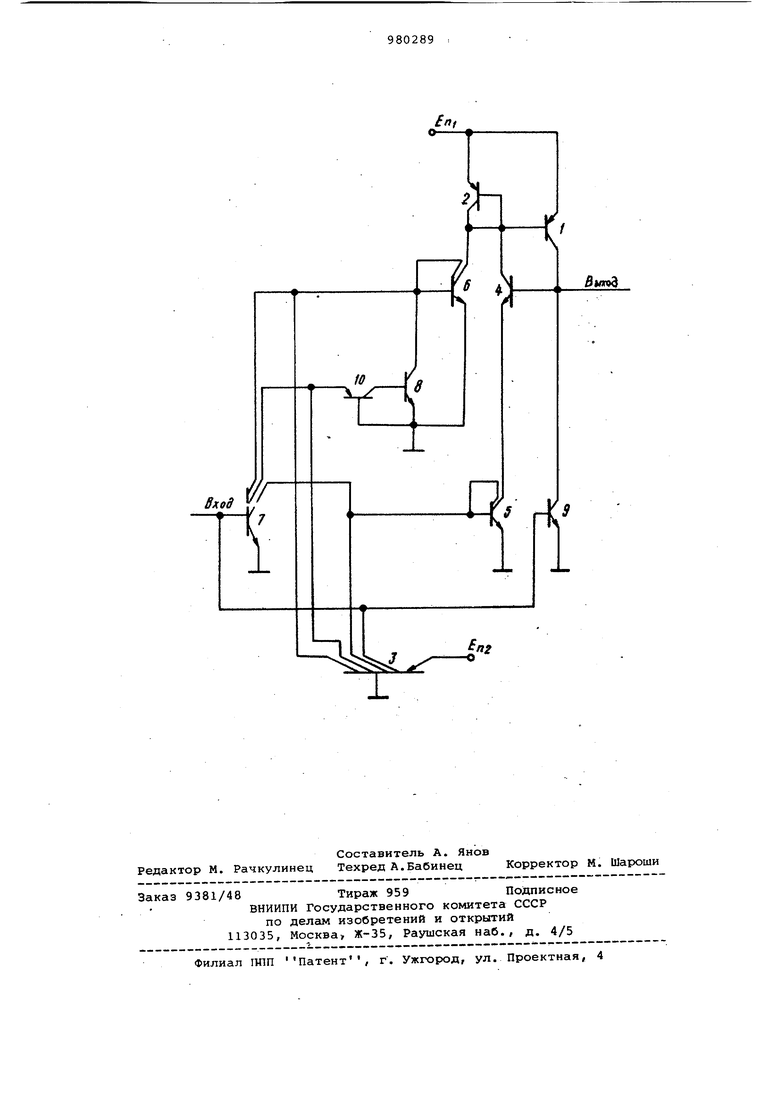

Таким образом, недостатком известного устройства является низкая наг30рузочная способность. Цель Изобретения - повышение нагрузочной способности логического буферного элемента, а также снижени мощности, потребляемой элементов в режиме ко ро т ко го з амык а ни я. Для достижения поставленной цели в элемент/ содержащий четыре п-р-п и три р-п-р-транзистора, причем эми теры первого и второго р-п-р-тран|3исторов соединены с первой шиной питания, коллектор первого р-п-ртранзистора соединен с базой первог п-р-п-транзистора, эмиттер которого соединен с первым коллектором второ го п-р-п-транзистора, эмиттер которого соединен с шиной нулевого потен циала, с эмиттером третьего и четвер того п-р-п-транзисторов и базой третьего р-п-р-транзистора, эмиттер которого соединен со второй шиной питания, а коллекторы соединены.соответственно с базами третьего и четвертого п-р-п-транзисторов, первы коллектор четвертого п-р-п-транзистора соединен с базой третьего п-р-п транзистора, первый коллектор которого соединен с базой первого р-п-ртранзистора, база четвертого п р-птранзистора соединена с входной ши ной, введены пятый, шестой п-р-птранзисторы и четвертый р-п-р-транзистор, база которого соединена с шиной нулевого потенциала, эмиттером пятого и шестого п-р-п-транзисторов база пятого п-р-п-транзистора соединена с коллектором четвертого р-п-ртранзистора, эмиттер которого соединей с первым коллектором третьего р-п-р-транзистора и вторым коллектором четвертого п-р-п-транзистора, третийколлектор которого соединен со вторым коллектором третьего р-п-р транзистора, с базой и вторым коллек тором второго .п-р-п-транзистора, база и коллектор второго р-п-р-транзистора объединены с базой первого р-п-р транзистора и коллектором первого п-р-п-транзистора, база которого соединена.свыходной шиной и коллектором шестого п-р-п-транзистора, база которого соединена с входной V шиной, коллектор пятого п-р-п-транзистора соединен с базой и вторым коллектором третьего п-р п-транзистора.. I- . На чертеже представлена электриtjecKaH принципиальная схема буферно fo логического элемента И Л типа. Элемент содержит первый 1, второ 2, третий 3 р-п-р-транзисторы, первый 4, второй 5, третий 6, четверты 7, пятый 8, шестой 9 п-р-п-транзисторы и четвертый р-п-р-транзистор 1 База четвертого п-р-п-транзистора 7 соединена с входом элемента Н Л-типа и первым коллектором треть его р-п-р-транзистора 3, первый коллектор четвертого п-р-п-транзистора 7 соединен с эмиттером четвертого р-п-р-транзистора 10 и вторым коллектором третьего р-п-р-транзистора 3. Так как коллектором четвертого р-п-р-транзистора 10 является база пятого п-р-п-транзистора 8, то четвертый р-п-р и пятый п-р-п-транзисторы 10 и 8 образуют логическую схему, выполняющую функцию линии задержки. Второй коллектор четвертого п-р-п-транзистора 7 соединен с третьим коллектором третьего р-п-р-транзистора 3, коллектором пятого п-р-птранзистора 8, а также с объединенными коллектором и базой.третьего п-р-п транзистора б, второй коллектор треть его п-р-п-транзистора б соединен с базой и коллектором второго р-п-ртранзистора 2, с коллектором первого п-р-п-транзистора 4 и базой первого р-п-р-транзистора 1, эмиттер первого п-р-п-транзистора 4 соединен с первым коллектором второго п-р-п-транзистора 5, база которого соединена с вторым коллектором второго п-р-птранзистора 5, .третьим коллектором четвертого .п-р-п-транзистора 7 и четвертым коллектором третьего р-п-рТранзистора 3, база первого п-р-птранзистора 4 объединена с коллекторами первого р-п-р и шестого п-р-птранзисторов 1,9 и выходной шиной, эмиттеры первого и второго р-п-ртранзисторов 1 и 2 соединены с первым высоковольтным источником питания, база первого п-р-п-транзистора 4 соединена с входной шиной, эмиттер третьего р-п-р-транзистора 3 соединен со вторым источником напряжения. Эмиттеры второго, третьего-, четвертого, пятого и шестого п-р-п-транзисторов 5-9 объединены с базами третьего и четвертого р-п-р-транзисторов 3,10 и шиной нулевого потенциала . Логический элемент работает следующим образом. Допустим, на входе элемента находится сигнал О. В этом случае ток, инжектируемый третьим р-п-ртранзистором 3 в базы четвертого и . шестого п-р-п-транзисторов 7 и 9, ответвляется на входную шину, поэтому четвертый и шестой п-р-п-транзисторы 7 и 9 закрываются, а ток, инжектируемый третьим р-п-р-транзистором 3 в базу пятого п-р-п-транзистора 8 через четвертый р-п-р-транзистор 10, приводит к отпиранию пятого п-р-п-транзистора 8, который через свой коллектор отбирает ток с базы третьего п-р-п-транзистора 6, поэтому последний запирается. При этом первые п-р-п и р-п-р-транзисторы 4 и 1 открываются. На выходе элемента появляется потенциал EncUjt Qj. , который соответствует логической единице. Пятый п-р-п-транзистор 8 представ ляет собой токовый повторитель, ограничивающий ток через второй р-п-р и первый п-р-п-транзисторы 2 и 4. Использование токового повторителя позволяет исключить из рассматриваемой схемыограничивающие резисторы. В этом случае через первый и второй п-р-п-транзисторы 4 и 5 протекает то достаточный для отпирания первого р-п-р-транзистора 1. При изменении значения входного сигнала на логическую единицу открываются четвертый и шестой п-р-п-тран зисторы 7 и 9. Отпирание четвертого п- р-п-транзистора 7 приводит к запиранию пятого п-р-п-транзистора 8, при этом третий п-р-п-транзистор 6 (не открывается, так как ток, инжекти руемый третьим р-п-р-транзис.тором 3 в базу ТЕ етьего п-р-п-транзистора 6, ранее отбираемый в коллектор пятого п-р-п-транзистора 8, отбирается четвертым п-р-п-транзистором 7. .Запирание второго п-р-п-транзистора 5 и от пирание шестого п-р-п-транзистора 9 приводит к запиранию первого п-р-птранзистора 4, что, в свою очередь, приводит к запиранию р-п-р-транзисто ра 1. На выходе логического элемента устанавливается Ьихомной уровень напряжения Цопос соответствующий логическому нулю, при этом разряд емкости нагрузки происходит -герез открытый транзистор 9. При изменении значения входного сигнала с i на О происходит заряд емкости нагрузки, причем время заряда определяется не только величи ной нагрузочной емкости, но и велйчи ной тока заряда, т.е. током, который течет через первый р-п-р-транзистор Для увеличения этого тока в момент изменения входного сигнала на короткое время включается третий п-р-птранзистор 6, который позволяет заJiaTb начальную величину базового тока первого п-р-п-транзистора 1 выше, нежели в стационарном режиме. Ограни чение величины этого тока осуществля ется путем использования токового по торителя. Время задания импульса ток в базу третьего п-р-п-транзистора 6 определяется временем переключения четвертого р-п-р и пятого п-р-п-тран зисторов 10 и 8. Таким образом, при установлении на входе элемента И Л-типа логическо го нуля запираются четвертый и шесто п-р-п-транзисторы 7 и 9, учитывая, что -до этого момента времени -пятый п-1 -п-транзистор 8 закрыт и ток, инжектируемый третьим р-п-р-транзистором 3, поступает в базу-пятого п-р-п транзистора 8 через четвертый р-п-ртранзистор 10. Следовательно, пятый п-р-п-транзистор 8 открывается с задержкой и в течение времени задержки на базе третьего п-р-п-транзистора 6 имеется единичный сигнал, который открывает третий п-р-п-транзистор 6. Ток, который течет через третий п-р-п и второй р-п-р-транзисторы 6 и 2, обеспечивает импульс тока в базу первого р-п-р-транзистора 1, который открывается. Открываются также первый и второй п-р-п-транзисторы 4 и 5. После отпирания пятого п-р-п-транзистора 8 ток, инжектируемый третьим р-п-р-транзистором 3 в базу третьего п-р-п-транзистора 6, отбирается в коллектор пятого п-р-п-транзистора 8, при этом третий п-р-п-транзистор б закрывается, однако ток, протекающий через второй р-п-р, первый и второй п-р-п-транзисторы 2,4 и 5, обеспечивает открытое состояние первого п-р-птранзистора 1. Таким образом, путем формирования тока в базу первого р-п-р транзистора 1 увеличивается ток, протекающий через этот транзистор, а следовательно, увеличивается и нагрузочная способность данного элемента. Немаловажным достоинством предлагаемого элемента является снижение потребляемой мощности в режиме короткого замыкания. Если на выходе элемента имеется происходит короткое замыкание, то в первую очередь закрывается первый п-р-п-транзистор 4, поэтому в стационарном режиме через второй р-п-р-транзистор 2 ток не протекает, что приводит к запиранию первого р-п-р-транзистора 1. Если короткое замыкдние длительно, то при изменении входного сигнала с на О открывается третий п-р-п-транзистор 6, что приводит к отпиранию первого р-п-р-транзистора 1 на время, равное максимальному требуемому фронту нарастания выходного сигнала. Поэтому ток, протекающий через первый р-п-р транзистор 1, является импульсным и не может привести к выходу из строя этого транзистора. В случае, если на входе элемента длительное время будет О, то в режиме короткого замыкания мощность, выделяемая на первом р-п-р-транзисторе 1, равна нулю. Таким образом, предлагаемый буферный элемент по сравнению с известным имеет более высокую нагрузочную способность и потребляемая ею мощность в режиме короткого замыкания снижается более чем в 10 раз. Более высокая нагрузочная способность объясняется следующим. Выходной ток первого р-п-р-транзистора 1 в момент формирования переднего фронта .выходного импульса задается большим током коллектора третьего п-р-птранэистора б, а выходной ток, формирующий вершину импульса, задается значительно меньшим током коллектора второго п-р-п-транзистора 5. Таким образом, первый п-р-п-транзистор 4 при коротком замыкании не открывается и через первый р-п-ртранзистор 1 протекают импульсы тока со скважностью 10 и более. При такой скважности бескорпусные .транзисторы и транзисторы в полупроводниковых схемах могут припускать импульсные токи, превышающие постоян Ные в 2-5 раз. Итак, предлагаемый элемент позво ляет увеличить нагрузочную способность по сравнению с известным за счет использования импульсных парам ров выходного транзистора. При коро ком замыкании,такой элемент не толь ко не выходит из строя, но и рассеи вает меньшую мощность, чем известны В результате элемент И Л-типа отличается более высокой, эксплуатацией, надежностью, а большая нагрузочная способность эквивалентна сокращению числа микросхем в цифровой системе, что сказывается на массе, габаритах .потребляемой мощности, надежности и стоимости системы. Формула изобретения Буферный Логический элемент И Л-т па, содержащий первый, второй и третий р-п-р-транзисторы, первый,второй третий и четвертый п-р-п-транзисторы причем эмиттеры первого и второго р-п-р-транзисторов соединены с перво шиной питания, коллектор первого р-п-р-транзистора соединен с базой первого п-р-п-транзистора, эмиттер которого соединен с первым коллектором второго п-р-п-транзистора, эмиттер которого соединен с шиной нулевого потенциала, с эмиттером третьего, четвертого п-р-п-транзисТС ров и базой третьего р-п-р-транзистора, эмиттер которого соединен с второй шиной питания, а коллекторы соединены соответственно с базой третьего и четвертого п-р-п-транзисторов, первый коллектор четвертого п-р-птранзистора соединен с базой третьего п-р-п-транзистора, первый коллектор которого соединен с базой первого р-п-р-транэистора, база четвертого п-р-п-транзистора соединена с входной шиной, отличающийся тем, что, с целью повышения нагрузочной способности, в него введены пятый, шестой п-р-п-транзисторы и четвертый р-п-р-транзистор, база которого соединена с шиной нулевого потенциала, эмиттером пятого и шестого п-р-п-транзисторов, база пятого п-р-птранзистора соединена с коллектором четвертого р-п-р-транзистора, эмитуер которого соединен с первым коллектором- третьего р-п-р-транзистора и вторым коллектором четвертого п-р-птранзистора, третий коллектор которого соединен с вторым коллектором третьего р-п-р-транзистора, с базой и вторым коллектором второго п-р-птранзистора, база и коллектор второго р-п-р-транзистора объединены с базой первого р-п-р-транзистора и коллектором первого п-р-п-транзистора, база которого соединена с выходной шиной и коллектором шестого п-р-п-транзистора, база которого соединена с входной шиной, коллектор пятого п-р-птранзистора соединен с базой и вторым коллектором третьего п-р-п-транзис. тора. Источники информации, принятые во внимание при экспертизе 1.Патент ФРГ № 2907597, кл. Н 03 К 19/08, 1979. 2.Аваев Н.А. и др. Большие интегральные схемы с инъекционным питанием. М., Советское радио ,.1977, с. 187, рис. 4.20 (прототип).

Ь

Btm

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство передачи дискретных сигналов | 1990 |

|

SU1709513A2 |

| Тактируемый @ -триггер в интегральной инжекционной логике | 1982 |

|

SU1051692A1 |

| Двоичный делитель частоты @ типа | 1983 |

|

SU1112533A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU868840A1 |

| Устройство питания абонентской телефонной линии | 1983 |

|

SU1164907A1 |

| Ячейка памяти | 1982 |

|

SU1140165A1 |

| Устройство для преобразования входного двоичного сигнала в телеграфный сигнал | 1983 |

|

SU1125765A1 |

| Устройство для контроля электронных схем | 1985 |

|

SU1270732A1 |

| Формирователь прямоугольных импульсов | 1983 |

|

SU1112540A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU902243A1 |

Вход

4Н/

Ч

Авторы

Даты

1982-12-07—Публикация

1981-06-25—Подача