(54) МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО

1

Изобретение относится к области вычислительной техники и может быть использовано в аналоговых и цифроанёшоговых вычислительных машинах.

. Изве.стное множителбно-делитель- 5 ное устройство содержит четыре ключа, два интегратора, нуль-орган, блок срсшнения, логические элементы, триггеры, тактовый генератор и аналоговый запомина рщий блок tH.

Недостатком этого уст)ойства является, невозможность- получения результата от произвольного большого числа напряжений, что значитель-15 но снижает его функциональные возможности, ,-,..,

Наиболее близким по технической сущности к предложенному устройству 20 является множительно-делительное устройство, содержащее схемы сравнения, первые входы которых являются входами устройства, источник опорного напряжёйия первый интегратор, 25 выход которого соединен со вторыми входами схем сравнения, в::лходы схем сравнения соединены со входами элемента ИЛИ, выход которого соединен ,с управляющим входом ключа, выход 30

Которого соединен со входом второго интегратора, выход которого являе.т с я выходом устройства, первый умножитель, первый вход которого сЪединен с информационным входом ключа, а второй, вход - с выходом первого интегратора, второй умножитель, входа которого соединены со входом первого интегратора и выходом второго интегратора, последовательно соединенные первые блок сложения и блок вычитания, причем выход первого блока вычитания соединен с первым входом первого блока сложения, управляемый делитель напряжения 2.

Однако это устройство недостаточно точно..

Цель изобретения - повышение точности .

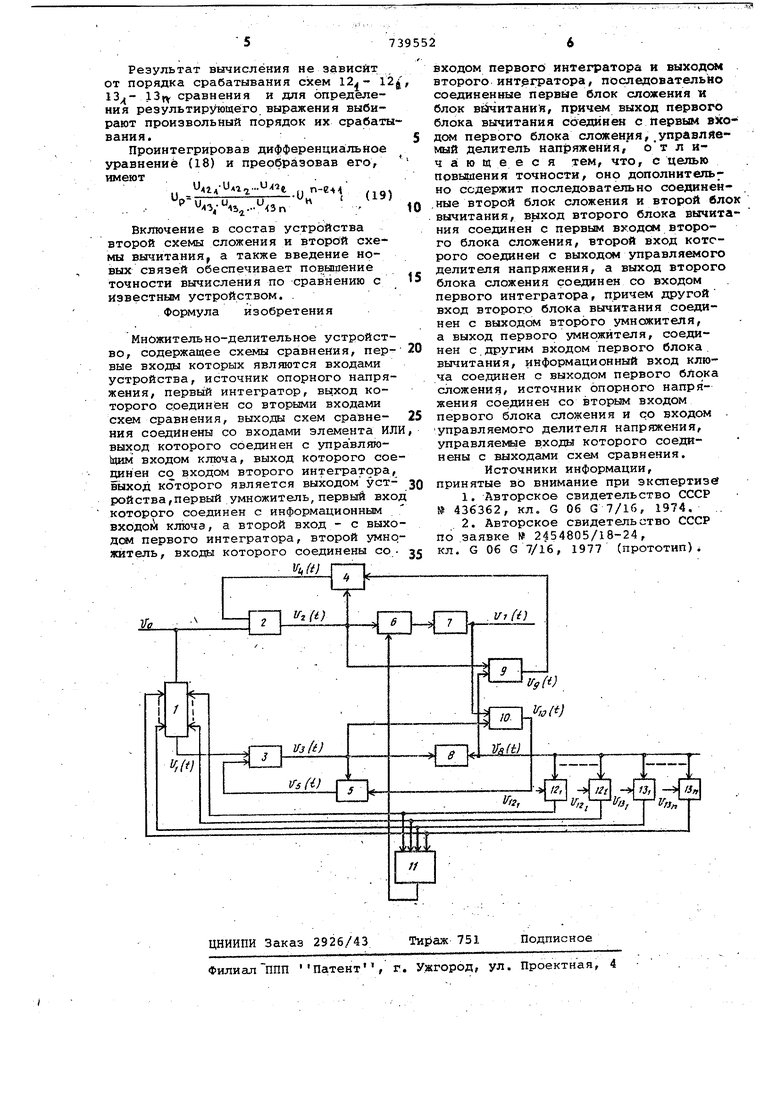

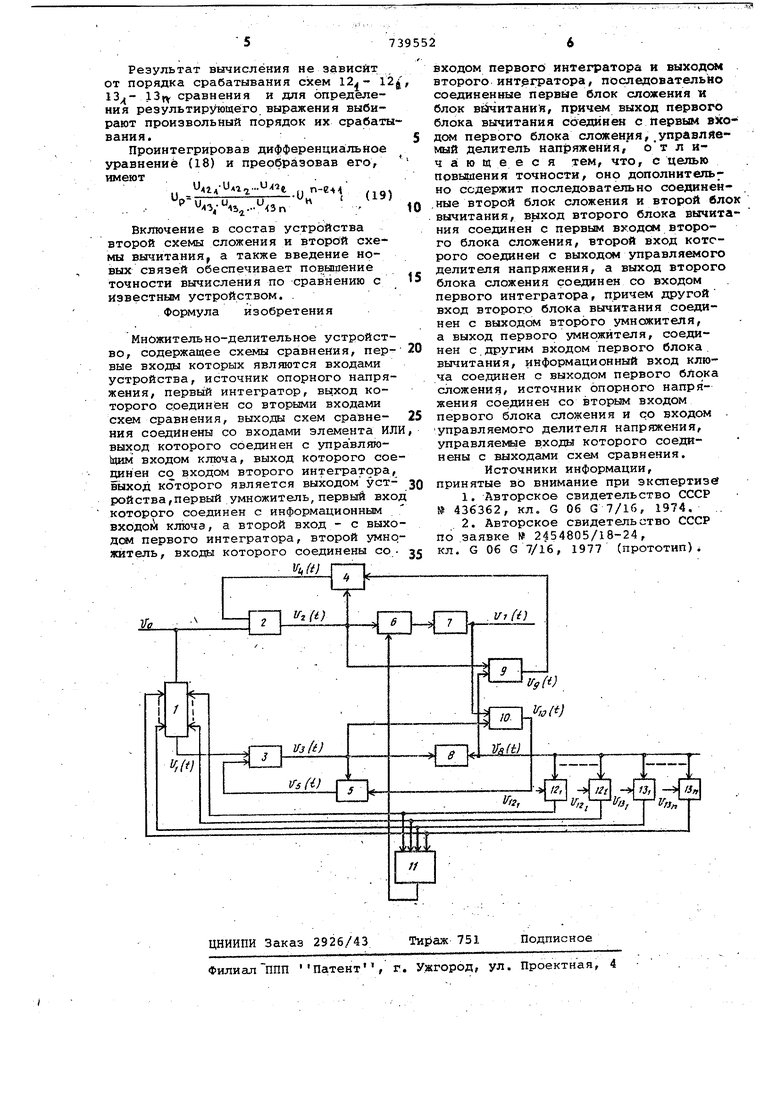

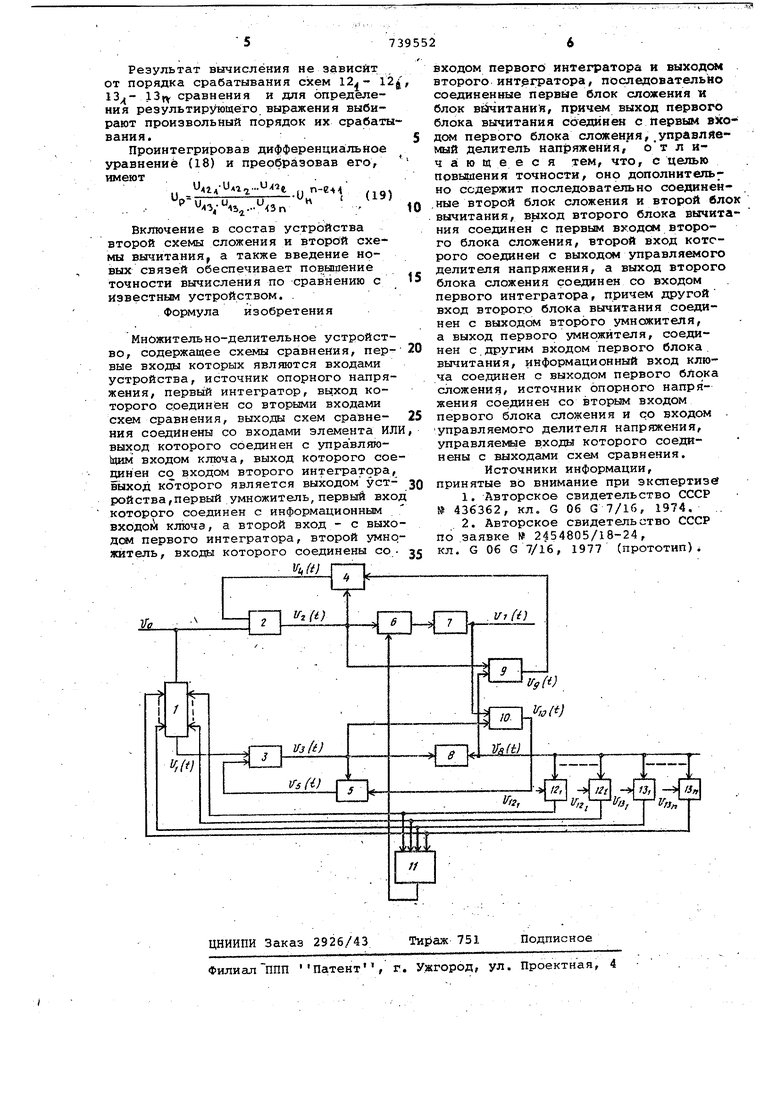

Это достигается тем, что устройство дополнительно содержит последовательно соединенные второй блок сложения и второй блок вычитания, выход второго блока вычитания соединен с первым входом второго блока сложения, второй вход которого соединен с выходом управляемого делителя напр.яжения, а выход второго блока сложения соединен со входом первого интегратора, причем другой вход второго блока ВЕЛЧИТ ШИЯ соединен с выходом BTOpqfo умножителя, а выход первого умножителя соединен с входом первого блока вычи.тания, инфоЁ)мационный вход кЗгоча соединен с выходом первого блика сложения, источник опорного напряжения соединен с6,вто1Ж1м входом ;первогй блока сложения и со входом управляемого делителя напряжени управляеьие входе которого соединены с выходами сравнения. ::,;--. . ...... V . На чертеже представлена структурная схема предложенного устройст ,--,- . . Устройствр состоит из управляемо делителя 1 напряжения, первого и вт рого блоков 2 и 3 сложения, первого и второго блоков 4 и 5 вычитания, ключа б, второго и первого интеграт ров 7 и 8/первого и второго умножителей 9 и 10, элемента ИЛИ 11, схем 12д-12 и 13д- 13п сравнения, Работает устройство следующим образом.. На второй вход блока 2 сложения И на вход управляемого делителя 1 подается постоянное напряжение U. На вторые входы схем 12g сравнения подаются постоянные уровни напряжений , значения которых равны множителям. На вторае ВХОДЫ схем I3;j- 13 сравнения подаются постоянные уровни напряжений и, , значения которых равны делителям. ПерЕовачально в управляемом депителе 1 напряжения устанавливается коэффициент деления, равный -ri где 6 - количество множителей,, а п количество делителей. При срабатывании каждой из схем 12,- 12 коэффициент деления управляемого делителя 1 напряжения уменьшается на единицу, а при срабатывании каждой схемы 13f, коэффициент деления увеличивается на единицу. Коэффициент управляемого делителя 1 напряжения может принимать как положительные, так и отрицательные эна чения. При отрицательных значениях коэффициента деления управляемый делитель 1 напряжения, кроме делеНИН входного напряжения, производит его ннвертирование. Напряжение на выходе управляемого, делителя . 1 напряжения, определ ся выражегшем: - .. ( U где Kj - переменный коэффициент деления управляемого делителя 1 напр жения. Напряжения DO и и (1 } поступают на входы блоков 2 и 3 сложения, на другие входы которых поступают напряжения Uy (t) и UjCi) с выходЬв блоков 4 -Н5 вычитания. Напряжения на выходе блоков 2 и 3 определяются выражением: U(t),(tX (2) ) .S(- (3) Напряжения на выходах блоков 4 и 5 определяются разностью напряжений, поступающих на их входы; 44(iW-Ug(i),(4) ,(tbU,(C), .(5) тде iJq (1 ) и ( t ) - напряжения, пос;Тупающие с выходов умножителей 9 и 10 соответственно, Подставляя равенство (1) в,равенство (3), а затем полученное равенртво в равенство (5), после чего равенство (2) в равенство (4), получают : . U4()-Ug(t),(б) . «5(i)(t) (7) Ug(t)Uo, .. Напряжения на выходах умножителей 9 и 10 определяются.произведением напряжений, посТ5шающих на их входы: M) U,()U.(t), (10) U-lo(tV-U( (11) гдеи, (i ) и Ug ( i ) - напряжения на выходах интеграторов 7 и 8. Подставляя выражения (10) в (8) и (11) в (9) , получают: из(1)-и(1)и (12) J7i)(t -Uo/Ki (13) Напряжения на входах интеграторов . 7 и 8 связаны с напряжениями на их выходах выражениями: . dU8(t) u,{t)-dtПодставляя равенства (14) в (12) и (15) в (13) , получают: ,; . Разделив уравнение . (16) на уравнение (17) и произведя очеред 1ые преобразования, получают: (t) olUftlt)(18) , . ) В момент преобразования в устройстве на выходах интеграторов 7 и 8 устанавливается начальное напряжение UH . В момент срабатывания последней схемы I2i , 13п сравнения (зрабатнвает элемент ИЛИ 11 и закрывается ключ б. Процесс вычисления в уст;ройстве заканчивается, и на выходе интегратора 7 фиксируется результат 0р.. Результат вычисления не зависит от порядка срабатывания схем 12 13д- 13jY сравнения и для определения результирующего выражения выбирают произвольный порядок их срабаты вания.. Проинтегрировав дифференциальное уравнение (18) и преобразовав его, имеют „ .vV Включение в состав устройства второй схемы сложения и второй схемы вычитания, а также введение новых связей обеспечивает повышение точности вычисления по сравнению с известным устройством. . Формула изобретения Множителвно-делительное устройство, содержащее схемы сравнения, первые входы которых являются входами устройства, источник опорного напряжения, первый интегратор, выход которого соединён со вторыми входами схем сравнения, выходы схем сравнения соединены со входами элемента ИЛ выход которого соединен с управляюЬчим входом ключа, выход которого сое динен со входом второго интегратора выход которого является выходом устройства,первый умножитель, первый вхо которого соединен с информационным входог ключа, а второй вход - с выхо де первого интегратора, второй умно житель, входы которого соединены со входом первого интегратора и выходсм второго интегратора, последовательно соединенные первые блок сложения и блок в 1читания, причем выход первого блока вычитания соединен с Первым входом первого блока сложения,,управлйвмый делитель напряжения/ от л ичающееся тем, что, с целью повышения точности, оно дополнительт но содержит последовательно соединенные второй блок сложения и второй блок вычитания, выход второго блока вычитания соединен с первым входом второго блока сложения, второй вход которого соединен с выходом управляемого делителя напряжения, а выход второго блока сложения соединен со входом первого интегратора, причем другой вход второго блока вычитания соединен с выходом второго умножителя, а выход первого умножителя, соединен с другим входом первого блока. вычитания, информационный вход ключа соединен с выходом первого блока сложения, источник опорного напряжения соединен со вторым входом первого блока сложения и со входом . управляемого делителя напряжения, управляемые входы которого соединены с выходами схем сравнения. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 436362, кл. G 06 G 7/16, 1974. . 2.Авторское свидетельство СССР по заявке 2454805/18-24, кл. G 06 G 7/16, 1977 (прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1977 |

|

SU674043A1 |

| Устройство для возведения в степень | 1976 |

|

SU604009A1 |

| Устройство для возведения в степень | 1977 |

|

SU736125A1 |

| Устройство для возведения в степень | 1977 |

|

SU608176A1 |

| Устройство для извлечения корня из суммы квадратов | 1981 |

|

SU955108A1 |

| Антилогарифмический преобразователь | 1977 |

|

SU643908A1 |

| Детектор квазиравновесия | 1980 |

|

SU938163A1 |

| Устройство для регулирования угла запаса ведомого сетью инвертора | 1983 |

|

SU1270852A1 |

| Устройство для управления циклоконвертором | 1982 |

|

SU1072237A1 |

| Цифровой измерительный неуравновешанный мост | 1978 |

|

SU789767A1 |

Авторы

Даты

1980-06-05—Публикация

1977-07-25—Подача