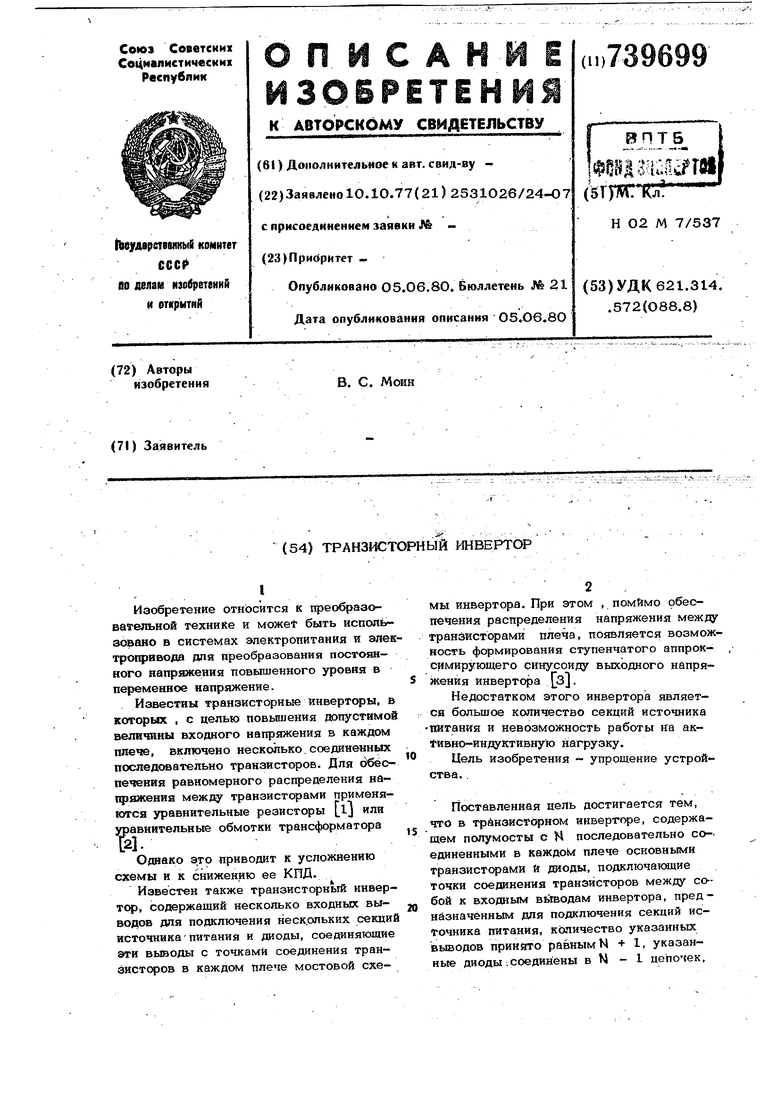

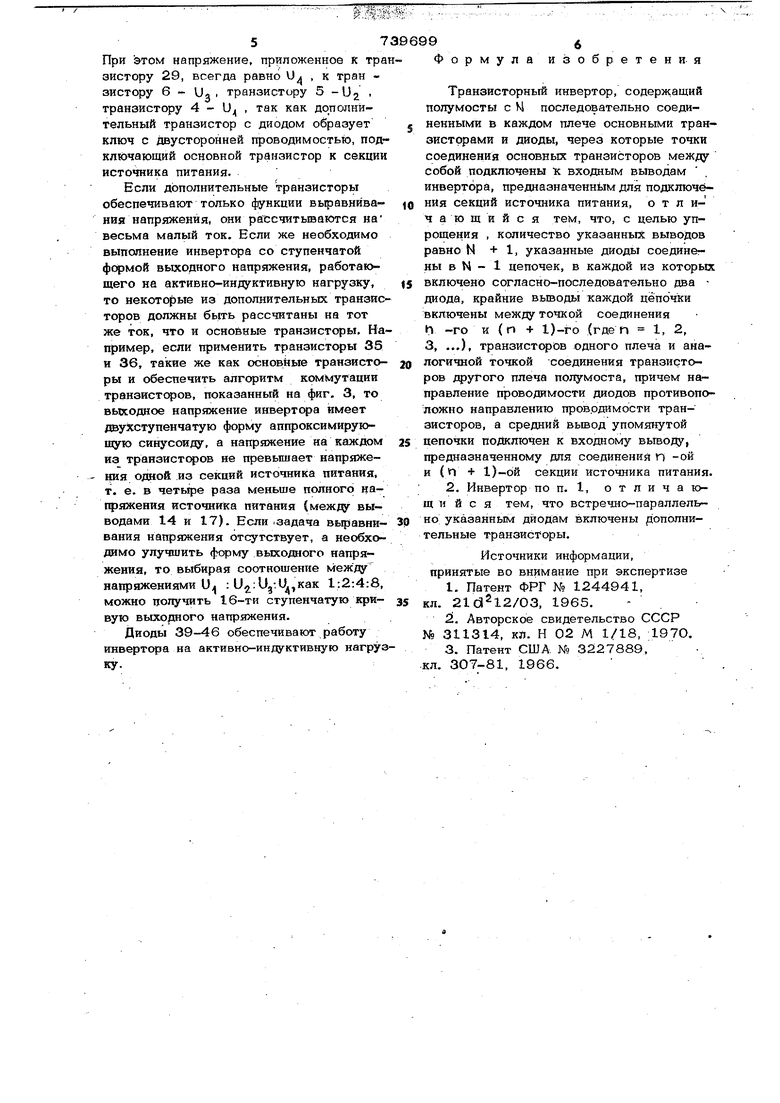

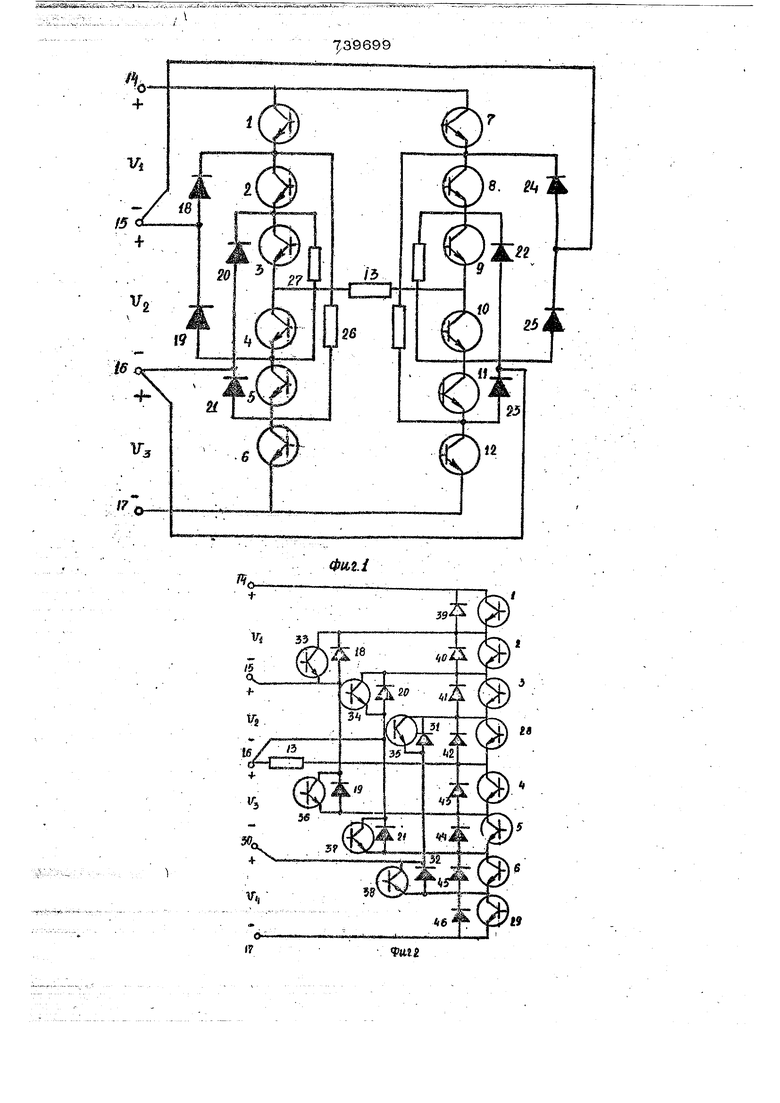

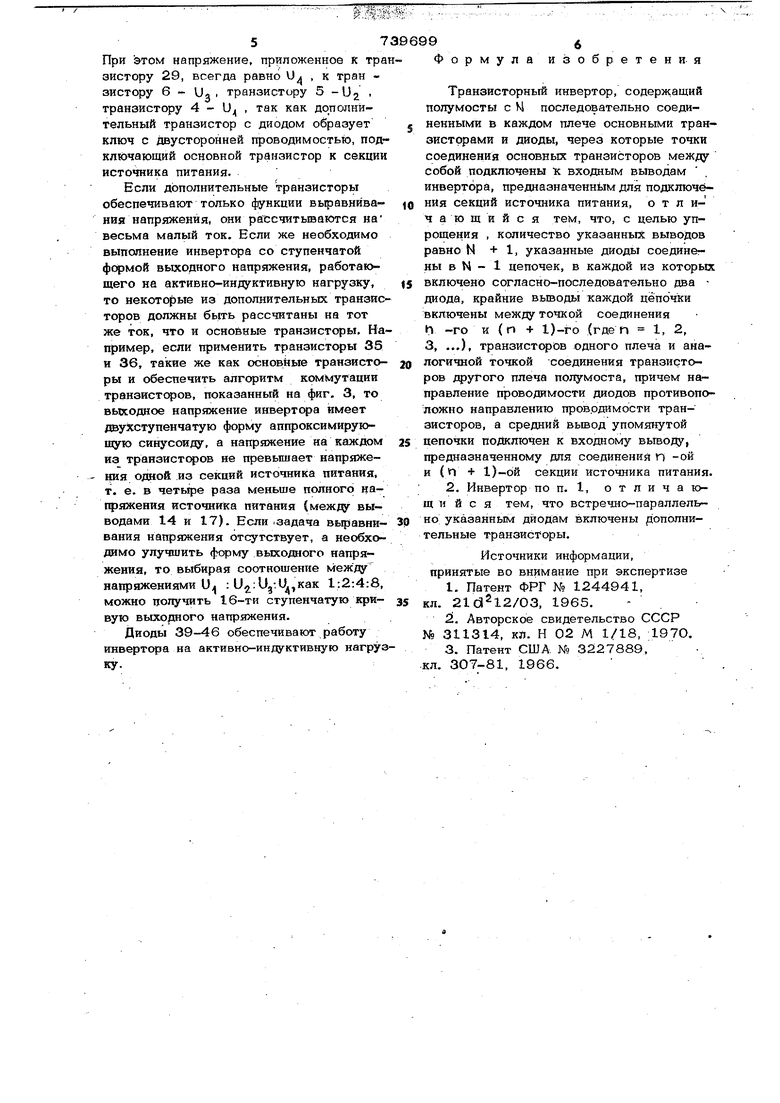

(54) ТРАН31«:ТОРНЫЙ ИНВЕРТС« , Изобретение относится к преобразовательной технике и може быть ИСПОЛЁУ в системах электропитания и элек тропрввода для преобразования постоянного напряжения повышенного уровня в переменное напряжение. Известны транзисторные инвертеры, в которых , с целью повышения допустимой величины входного напряжения в каждом ппече, включено несколько.соединенных последовательно транзисторов. Для обеспечения равномерного распределения на1фяжения межод- транзисторами применяются уравнительные резисторы ij или Зфавнительные обмотки трансформатора 2. Однако это приводит к усложнению схемы и к снижению ее КПД. Известен также транзисторный инвертор, содержащий несколько входных выводов для подключения нескольких секций источникапитания и диоды, соединяющие эти выводы с точками соединения транзисторов в каждом плече мостовой схеМЫ инвертора. При этом , помимо обеспечения распределения напряжения между транзисторами плеча, появляется возможность формирования ступенчатого аппроксимирующего синусоиду выходного напряжения инвертора з. Недостатком этого инвертора является большое количество секций источника датания и невозможность работы на активно-индуктивную нагрузку. Цель изобретения - упрощение устройства. . Поставленная цель достигается тем, что в транзистсфном инверторе, содержащем полумосты с М последовательно со-единенными в каждом плече основными транзисторами и диоды, подключакидие точки соединения транзисторов между собой к входным вьшодам инвертора, предназначенным для подключения секций источника питания, количество указанных выводов принято равным Ы + 1, указанные диоды .соединены в N - 1 цепочек. 373 состоящих из даух согласно-последователь но соединенных диодов, крайние выводы цепочек подключены между точками соединения h -го и (п )-го транзистора смежных плеч полумоста, а средний вывод этой цепочки подключен к входному выводу, предназначенному для соединения п -ой и (п + 1)-ой секции источника питания. Для улучшения вьфавнивания напряжения на транзисторах встредао-параллельно диодам включаются дополнительные транзисторы. . На фиг. 1 показан вариант предла аемой мостовой схемы при Н 3; на фиг. 2 - варТиант полумостовой схемы при Н 4; на. фиг. 3 - диаграммы коммутации транзисторов. Инвертор (фиг. 1) содержит транзисторы 1-12, включенные по мостовой схеме с тремя последовательно соединенными транзисторами в каждом плече. Вь1ход моста соединен с нагрузкой 13, а вход моста подключен кисточнику питания, состоящему из трех секций с напряжениями 1), , и,, , и . Секции источника It , -З И1 1и1пила питания подключены к входным выводам 14-17 инвертора. Между точкой соединения первого и второго транзистора (1 и 2) верхнего плеча полумоста и точкой соединения первого и второго транзистора (4 и 5) нижнего плеча этого полумоста включена первая цепочка из согласно-посл довательно соединенных диодов 18 и 19. Между точкой соединения второго и треть го транзистора (2 и 3) верхнего плеча полумоста и точкой соединения второго и третьего транзистора (5 и 6) нижнего плеча полумоста включена вторая цепочка из согласно-последовательно соединенных диодов 20 и 21. Аналогично включены де почки диодов 22 и 23, 24 и 25 в другом полумосте инвертора. Средний вывод первой цепочки диодов каждого полумоста подключен к входному вьшоду 15, предназначенному для соединения первой и вта рой секции источника питания, а средний вывод второй цепочки диодов каждого полумоста подключен к входному вьшоду 16, предназначейному для соединения вто рой и третьей секции источника питания. При увеличении числа транзисторов в плече соответственно увеличивается таслр цепочек диодов и число секций источника питания, а соединения между ними производятся аналогично описанному. Устройство работает.еледующим об разом. 9 В один полупериод, например, открьгоаютются транзисторы 1-3, 10-12, а в другой 4-9. Напряжения, приложенные к закрытым транзисторам, фиксируются с помощью диодов на уровне напряжений секций источника. Например, при открытых транзисторах 1-3 напряжение на транзисторе 6 не может быть больще , чем Uq , так как открывается диод 21, а напряжение на транзисторах 6 и 5 не может быть больше U2 + -з .так как открьюается диод 19. Если U;( и УЗ и необходимо выровнять напряжение на всех транзисторах плеча, то для того, чтобы на транзисторе 5 не было перенапряжения , при токе утечки транзистора 6, большем чем транзистфа 5 или 4, необходимо включить резистор 26, обеспечивающий прохождение тока несколько большего, чем разность между токами утечки транзисторов 6 и 5 (или 4). Из аналогичных соображений выбирается резистор 27. В отличие от схемы с обычными выравнивающими резисторами, через которые необходимо пропустить ток, на порядок превышающий максимальный ток утечки транзистора, в предлагаемой схеме через транзистор достаточно пропустить ток, равный макримальному току утечки транзистора, т. е. мощность, рассеиваемая в резисторах, уменьшается в 5-10 раз. Кроме того, резко уменьшается количество резисторов {в инверторе по фиг. I втрое), Для обеспечения выравнивания напряжения на транзисторах без использования резисторов предлагается схема инвертора по фиг. 2. Инвертор для примера выполнен по полумостовой схеме с четырьмя последовательно соединенными транзисторами в каждом плече (1-3, 28 и 4-6, 29), Точки соединения транзисторов подключены к входным выходам 15, 16 и 30 инвертора с помощью диодов 18-21, 31 и32, соединенныхвтрицепочки по схеме, описанной в инверторе по фиг. 1. Встречно-параллельно каждому диоду включены .пополнительные трайзисторы 33-38. Инвертор (фиг. 2) работает аналогично инвертору по фиг. I. Однако для лучшего выравнивания напряжения между транзисторами одаовременно с основными транзисторами одного плеча полумоста, (например, 1-3 и 28) открььваются дополнительные транзисторы, сс единенные с основными транзисторами (4-6 и 29) другого плеча полумоста. При этом напряжение, приложенное К тран зистору 29, всегда равно Од , к тран зистору 6 - и, , транзистору 5 -U2 транзистору 4 - и , так как дополнительный транзистор с диодом образует ключ с двусторонней проводимостью, подключающий основной транзистор к секции источника питания. Если дополнительные транзисторы обеспечивают только функции выравнива- Q ния ния напряжения, они ра ссчитьгоаются на весьма малый ток. Если же необходимо выполнение инвертора со ступенчатой формой выходного напряжения, работающего на активно-индуктивную нагрузку, то некоторые из дополнительных транзисторов должны быть рассчитаны на тот же ток, что и основные транзисторы. Например, если применить транзисторы 35 н 36, такие же как основные транзисторы и обеспечить алгоритм коммутации транзисторов, показанный на фиг. 3, то вькодное напряжение инвертора имеет двухступенчатую форму аппроксимирующую синусоиду, а напряжение на каждом25 цепочки подключен к входному выводу, из транзисторов не превышает nanpsoKe-предназначенному для соединения п -ой ния одной из секций источника питания,и {П + 1)-Ьй секции источника питания. т. е. в четьфе раза меньше полного на- 2. Инвертор по п. 1, отлича юпряжения источника питания (между вы- щ и и с я тем, что ветречно-параллельводами 14 и 17). Если .задача выравни-30 но указанным диодам включены дополнивания напряжения отсутствует, а необхо- тельные транзисторы. димо улучшить форму выходного напряжения, то выбирая соотношение кгежду напряжениями и;| ):( 1:2:4:8, можно получить 16-ти ступенчатую кри- 35 вую выходного напряжения. Диоды 39-46 обеспечивают работу инвертора на активно-индуктивную нагрузку73

ров другого плеча полумоста, причем направление проводимости диодов противоположно направлению проводимости транзисторов, а средний вьюод упомянутой 9 Формула изобретения Транзисторный инвертор, содержащий полумосты с Ы последовательно соединенными в каждом плече основными транзисторами и диоды, через которые точки соединения основных транзисторов между собой подключены к входным выводам инвертора, предназначенным для подключёсекций источника питания, о т л ичающийся тем, что, с целью упрощения , количество указанных выводов равно N +1, указанные диоды соединегны в N - 1 цепочек, в каждой из которых включено согласно-последовательно два диода, крайние вьшоды каждой цепочки включены между точкой соединения h -го и (п -f 1)-го (где П 1, 2, 3, ...), транзисторов одного плеча и аналогичной точкой соединения транзистоИсточники информации, принятые во внимание при экспертизе I. Патент ФРГ № 1244941, кл. 21(3 12/03, 1965. Si. Авторское свидетельство СССР j 311314, кл. Н 02 М 1/18, 1970. з. Патент США № 3227889, кл. 307-81, 1966.

739699

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь постоянного напряжения | 1990 |

|

SU1757070A1 |

| Транзисторный инвертор | 1979 |

|

SU873362A1 |

| Бестрансформаторный инвертор | 1975 |

|

SU577626A1 |

| Транзисторный инвертор тока | 1984 |

|

SU1182615A1 |

| Транзисторный инвертор | 1985 |

|

SU1297199A1 |

| Инвертор со ступенчатой формой кривой @ -фазного выходного напряжения | 1972 |

|

SU957387A1 |

| Инвертор | 1978 |

|

SU764073A1 |

| Двухтактный инвертор | 1978 |

|

SU748747A1 |

| Инвертор | 1985 |

|

SU1275716A1 |

| Устройство для искрозащиты | 1988 |

|

SU1511436A1 |

VH

Г л

шн/ш//м///мт////т

ЗС, 3 , (

///////////.

I

LS

w/iniffiaifk

&8.8

7/111шш1Ш11т11111тн/гщ1Г1гт

a.2g

r

J

ш1ШийП 1

mf/m//m///m

:l/////////// ////////W/jr/ft

.giiiSiZ

ii/fiff/f/fWf///fMMff///AWMm

/yjife

iiiiiii/i/fffffff

mM/t/H/

Фй«.3

Авторы

Даты

1980-06-05—Публикация

1977-10-10—Подача