(54) ТРАНЗИСТОРНЫЙ ИНВЕРТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухпозиционный транзисторный переключатель | 1985 |

|

SU1298885A1 |

| ДВУХТАКТНЫЙ ИНВЕРТОР | 1992 |

|

RU2009609C1 |

| Стабилизированный преобразователь напряжения с защитой от перегрузок | 1985 |

|

SU1295490A1 |

| Двухтактный транзисторный инвертор | 1988 |

|

SU1603511A1 |

| Транзисторный инвертор тока | 1984 |

|

SU1182615A1 |

| РЕКУПЕРИРУЮЩИЙ ЭЛЕКТРОПРИВОД ПЕРЕМЕННОГО ТОКА С ДВУХЗВЕННЫМ ПРЕОБРАЗОВАТЕЛЕМ ЧАСТОТЫ | 2014 |

|

RU2584002C1 |

| Устройство дифференциальной защиты | 1985 |

|

SU1272392A1 |

| Транзисторный инвертор | 1985 |

|

SU1297199A1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ СЕТЕВОГО ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ТОК СВАРКИ | 1995 |

|

RU2076026C1 |

| Преобразователь выпрямленного напряжения сети | 1981 |

|

SU951600A1 |

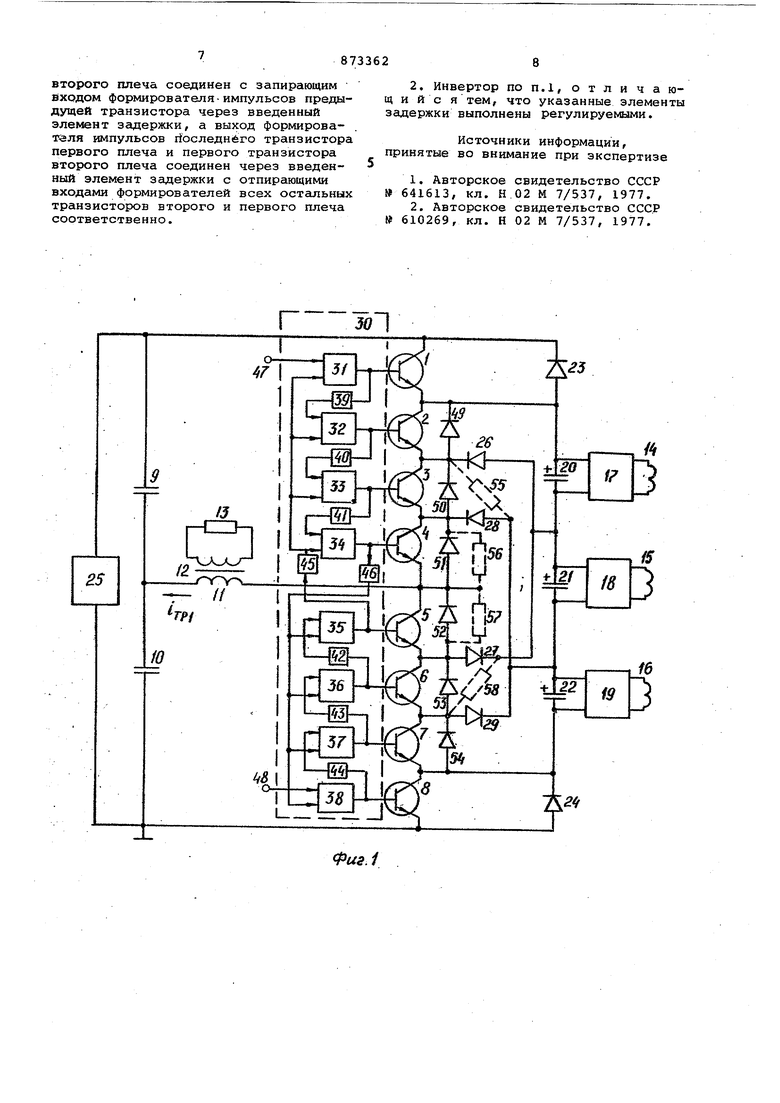

Изрбретелие относится к электрртехнике и может быть использовано для преобразования постояйнО17О напряжения высокого уровня в Переменное или -постоянное напряжение другого уровня. Известны инверторы и транзисторные ключи с последовательным соединением транзисторов, в которых для равномерного распределения напряжений между последовательно соединенными транзис торами используются выравнивакяцие цепи 1. Эти инверторы имеют понижен ную надежность из-за того, что указанные выравнивающие цепи не устраняют перенапряжений и сверхтоков в транзисторах в процессах переключения Наиболее близким к предлагаемому. по технической сущности является ин-, вертор, содержащий две цепочки из Nпоследовательно включенных транзисторов , присоединенных к выходному в|Лводу, выравнивающие цепочки, выполнены в виде выпрямителей, причем входы выпрямителей подключен к дополнительным обмоткам выходного трансформатора, а выходы зашунтированы конденсатором и включены между сим метричными относительно выходного вывода точками соединения транзисторов в одной и другой цепочках 2. Из-за разброса времени рассасывания отдельных транзисторов в таком инверторе наблюдаются перенапряжения на отдельных транзисторах и броски тока через них в процессах переключения. Это приводит к снижению надежности инвертора, увеличению динамических потерь (уменьшению КПД), препятствует повышению рабочей частоты инвертора. Целью изобретения является повышение надежности инвертора. Цель достигается тем, что в транзисторном инверторе, содержащем по ме.ньшей мере один полумост с -N-последовательно соединенными транзисторами, шунтирова 1ными встречно включенными диодами в каждом плече, выходной трансформатор,- дополнительные обмотки которого соединены со входом N-1, выпрямителей, выходы которых шунтированы конденсаторами и связаны с точками соединения транзисторов в плечах полумоста, и формирователи управляющих импульсов, включенные во входную цепь каждого транзистора, выходы указанных выпрямителей- соединены согласно последовательно, образуя цепочку с двумя крайними и N-2 промежуточными выводами, причем первый вывод цепочки выпрямителей соединен с точкой соедине1 ия первого и второго транзисторов в Первом плече полумоста, последний вывод этой цепочки соединен с точкой соединения последнего и предпоследнег транзисторов во втором плече полумоста, каждый промежуточный К-ый вывод этой цепочки соединен через диоды с точкой соединения транзисторов с номером К+1 и К+2 первого плеча и точкой соединения транзисторов с номером К и К+1 второго плеча, причем выход формирователя импульсов каждого, кроме последнего, транзистора первого плеча соединен с запирающим входом формирователя импульсов последующего транзистора через введенный элемент задержки, при этом выход формирователя импульсов каждого, кроме первого, транзистора второго плеча, соединен с запирающим входом формирователя импульсов предцдущего транзистора через введенный элемент задер жки, а выход формирователя импульсов последнего транзистора первого плеча и первого транзистора второго плеча соединен через введенный элемент задержки .с отпирающими входами формирователей всех остальных транзисто-. ров второго и первого плеча соответственно. Указанные элементы задержки могут быть выполнены регулируемыми. На фиг.1 приведена принципиальная электрическая схема предлагаемого инвертора в случае последовательного соединения четырех транзисторов в це почке; на фиг.2 диаграммы напряжений токов, пбяснякяцие .его работу. Инвертор содержит первое и второе плечо полумоста с последовательно включенными транзисторами Ы и 5-8, емкостный делитель напряжения на конденсаторах 9 и 10. В диагональ моста включена первичная обмотка 11 силового трансформатора 12. Ко вторичной обмотке трансформатора подключена нагрузка 13. Трансформатор 12 имеет дополнительные обмотки 14-16, к которвым подключены входы выпрямителей 17-19 с конденсаторами 20-22 на выходах. Выходы выпряг штелей 17-18 соединены последовательно согласно и образуют последовательную цепь, крайние выводы которой подключены к общим точ кам транзисторов 1, 2 и 7,, 8 и через диоды 23 и 24 - к полюсам основного источника питания 25. Первый промежуточный вывод цепи выпрямителей через диоды 26 и 27 подключен к общим точкам транзисторов 2, Зи5, б. Второй промежуточный вывод цепи выпрямителей через диоды 28 и 29 подключен к общи точкам транзисторов 3, 4 и 6, 7. При этом между общими точками транзисторов , связанными с одним выводом цепи выпрямителей оказываются включенными всегда три транзистора, например транзисторы 3, 4, 5 и 4, 5, 6. Блок управления 30 содержит формирователи управляющих импульсов -31-38 для каждого транзистора. Формирователи имеют входы для сигнала запирания и сигнала отпирания транзисторов. В каждой цепочке транзисторов выход каждого формирователя , начиная с формирователя, ближайшего к полюсу источника питания (с формирователей 31 и 38 соответственно) , соединен с запиракядим входом следующего формировталея через элемент задержки 39-44. Выход последнего формирователя одного плеча (формирователи 34 и 35) через элемент задержки 45 или 46 соединен со всеми отпирающими входами формирователей дру-, гого плеча. Запирающий вход 47 формирователя 31 является входом для сигнала запирания цепочки транзисторов 1-4. Запирающий вход 48 формирователя является входом для сигнала запирания цепочки транзисторов 5-8. Диоды 4954 включены встречно параллельно транзисторам для обеспечения работы на активно-индуктивную нагрузку. Резисторы 55-58 улучшают распределение на1пряжения между транзисторами. Инвертор работает следующим образом. Количество витков дополнительных обмоток 14-16 выбирается таким образом, чтобы напряжения на выходе каж-. дого выпрямителя иgj,,f,p равнялись Un 14, где Ufi - напряжение источника питания 25. Пусть в исходном состоянии транзисторы 1-4 открыты, а транзисторы 5-8 закрыты, что соответствует интервалу (t(j, ц) на фиг. 2. На этом интервале потенциал Up выходного вывода (общей точки соединения двух транзисторных цепочек) близок к Un/ ток первичной обмотки -frp трансформатора нарастает, напряжения Ц-Уд. на транзисторах 1-4 близки к нулю. Диоды 26, 28, 24 закрыты, так как к первому приложено напряжение с конденсатора 20, ко второму - с конденсаторов 20 и 21, а к третьему приложению напряжение УП - 3Uej,inp. На коллектор транзистора 6 через диод 27 подается потенциал Ufj -Ug(,inp , на коллектор транзисгтора 7 через диод 20 - потенциал l)f, - ,, , на коллектор транзистора 8 - потенциал Urj- 3Ue,t, . Таким образом на данном интервале напряжения коллектор эмиттер УЗ -и транзисторов 5-8 определяются напряжениями на выходе вспомогательного выпрямителей и равны В некоторалй момент подается сигнал запирания на вход 47 формирователя 31, затем через элемент задержки на запирающий вход формирователя 32 и т. д. При этом запирающие сигналы на базы транзисторов 1-4 подаются поочередно, начиная с транзистора 1. Величина задержки подачи запирающего сигнала для очередного транзистора выбирается больше, чем время рассасывания предыдущего транзистора. Через некоторое время после подачи сигнала на вход 47 (по истечении времени рассасывания) в момент i происходит запираете транзистора I. На следующем интервале (Ц t4 ) открыты транзисто1ял 2-4, остальные транзисторы закрыты. Ток на чинает заьшкаться по цепи:транзисторы 2-4, конденсаторы 20-22, диод 24. Выходной вывод имеет потенциал Up -3Ug{,ffl К выключенному транзистору 1 при этом прикладывается напряжение Un - , напряжение на транзисторе 8 падает до нуля, так как диод 24 открывается. Диоды 26 и 28 по-прежнему закрыты. На коллекторы транзисторов 5, б и 7 через открытые диоды 27 и 29 подаются потенциалы выводов цепи выпрямителей. Потенциал коллектора транзистора- 5 равен 3Uef,,np , транзистора 6 - 2Ug,np , транзистора 7 -Ug{,inp . Таким образ.ом, на этом интервале напря жения на всех транзисторах равны Ufj /4.

В момент ij происходит запирание транзистора 2. На следующем интервале ( trj/ Э остаются открытыми транзисторы 3 и 4. Дисзд 26 открывается, диод 27 закрывается замыкается по цепи: транзистора 3 и 4, диод 26, конденсаторы 21 и 22, диод 24. Выходной вывод имеет потенциал Up ивыпр к выключенному транзистору 1 приложено напряжение ип - %binf. к транзистору 2 - напряжение ,(пр с конденсатора 20. Напряжение на коллекторе транзистора 8 по-прежнему близко к нулю, потенциал коллектора транзистора 7 равениб(,щр , поэтому напряжение коллектор-эмиттер транзистора 7 равно Uq/4. , .суммарное напряжение на транзисторах 5 и 6 Uj + и также рашно Ир/д. , и в целом напряжения на закрытых транзисторах не превышает 1/„/4 . В момент t запирается транзистор

В кривой TOKa-f p на фиг. 2 имеются колебательные импульсы тока заряда конденсаторов 20-22..

Элементы задержки 39-41 и 42-44 могут быть выполнены регулируемыми. При этом появляется возможность регулирования выходного напряжения инвертора.

В соответствии с изложенными принципами могут быть построены другие инверторные схемы. Например, однофазная гvк cтoвaя схема инвертора будет иметь четыре попарно соединенные цепочки, каждая из N-последовательно соединенных транзисторов, и соответственнЬ две последовательные цепи выпрямителе

Предлагаемый инвертор по сравнению с известным имеет более высокую надежность, так как в нем устранены перенапряжения на отдельных транзистора и броски тока через них в процессах переключения. Кроме того, новое построение схемы уменьшает динамические потери в транзисторах, увеличивает при прочих равных КПД инвертора и позволяет увеличить рабочую частоту.

Формула изобретения

второго плеча соединен с запирающим входом формирователя-импульсов предыдущей транзистора через введенный элемент задержки, а выход формирова- . т-аля импульсов йоследнбго транзистора первого плеча и первого транзистора второго плеча соединен через введенный элемент задержки с отпирающими входами формирователей всех остальных транзисторов второго и первого плеча соответственно.

Источники информации, принятые во внимание при экспертизе

2,Авторское свидетельство СССР № 610269, кл. Н 02 М 7/537, 1977,

Фиг.2

Авторы

Даты

1981-10-15—Публикация

1979-11-13—Подача