1

Изобретение относится к вычислительной технике, в частности к устройствам обработки сигналов информации в реальном масштабе времени и может быть использовано для фильтрации сигналов, распознавания стилизованных образов и т.п.

Известно устройство для получения свертки сигналов содержащее пьезоэлектрический элемент, пару входных преобразователей и выходной преобразователь 1.

Наиболее близким по технической сущности к предложенному является устройство, содержащее моделиветвей,каждая из которых моделирует дугу графа.временным интервалом,генератор импульсов и блок формирования топологии, выход элемента ИЛИ которого соединен с первыми входами первого и через инвертор второго элементов И, второй вход последнего соединен с первым выходом генератора импульсов, первый вход формирователя временного интервала каждой модели ветви соединен с выходом вгорого элемента И блока формирования топологии, а выход формирователя временного интервала подключен к первому входу первого триггера, выход второго триггера соединен с первым входом элемента И 2.

Недостатком этого устройства является низкая точность и быстродействие ,

Цель изобретения - повышение точности и быстродействия выполнения операции свертки.

Поставленная цель достигается

10 тем, что в устройство, содержащее генератор импульсов, первый и второй вь1ходы которого подключены соответственно к первому и второму входу блока формирования топологии, группа

15 входов которого соединена с выходами .моделей ветвей, первый вход каждой из которых подключен к первому выходу блока формирования топологии, введены модели узлов и счетчик,

20 вход которого соединен с первым вы- ходом блока формирования топологии, третий вход которого соединен с третьим выходом генератора импульсов, второй и третий выходы блоки форми25рования топологии подключены соответственно к первым и вторым входам моделей узлов, третий вход каждой из которых соединен с выходом соот ветствующей моделей ветви, второй вход каждой модели ветви подключен

30

к выходу соответствующей модели узла, группа входов каждой модели узла подключена к выходам счетчика, кроме того модель ветви содержит элементы И, триггеры, задатчик частоты и счетчик импульсов, вход которого через задатчик частоты соединен ,с выходом первого элемента И, первый вход которого является перВЕдм ВХОДОМ- модели, а второй вход первого элемента И соединен с первым выходом- первого триггера, вход которого подключен к выходу счетчика импульсов, вход второго триггера является вторым входом модели ветви, второй выход первого и выход второго триггеров подключены соответственно к первому и второму входам второго элемента И, выход которого является выходом модели ветви, а также модель узла содержит распределителиэлемент ИЛИ и сумматор, входы которого являются группой входов модели, первым и вторым входом которой являются соответственно первый и второй входы распределителей,выходы которых являются выходами моделей и соединены со входами элемента ИЛИ, выход которого подключен к соответствующему входу сумматора, кроме того, блок формирования топологии содержит элементы И, НЕ и элемент ИЛИ, входы которого являютс группой входов блока, выход элемент ИЛИ через элемент НЕ соединен с первым входом первого элемента И и непосредственно подключен к первым входам второго и третьего элементов И, вторые входы первого второго и третьего элементов И являютс соответственно первым, вторым ,и третьим входами блока формирования топологии.

Операцию свертки двух дискретных функций можно представить как сумму попарных произведений

,®.,etHv И)

где F - дискрет функции свертJ fi ки;

- дискрет функции fCxj-t); g,) - дискрет функции д ()

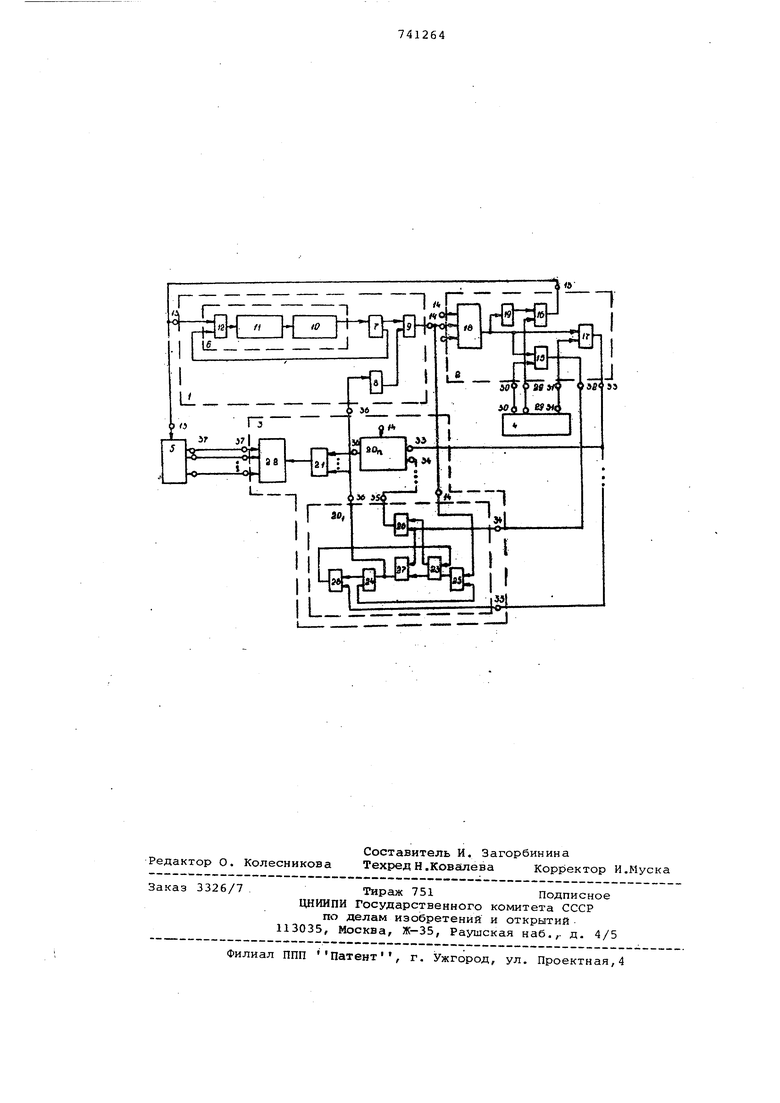

На чертеже представлена схема устройства.

Схема устройства содержит модель ветви 1, блок 2 формирования топологии, модель узла 3, генератор 4 импульсов, счетчик 5, имеющий поразрядные параллельные выходы.

Каждая модель ветви 1, число которых равно квадрату точек дискретизации функции свертки, состоит из формирователя 6 временного интервала, триггеров 7, 8 и элемента 9 И; формирователь б временного интервала включает счетчик 10 импульсов, задатчики 11 частоты и элемент 12.

Задатчик 11 частоты представляет собой элемент, в котором опорная частота, подаваемая на вход, делитс на частоты кратные 1,2...(п-1),п. На вход элемента пропускается тольк одна частота,которая обратно пропорциональна задаваемой величине.

Модель ветви 1 предназначена для формирования временного интервала, величина которого пропорциональна произведению дискретов двух функций (j-) идСх.,-)- Если предварительно занести в счетчик 10 импульсов число импульсов, дополняющее величину дискрета {(x.j-r) до полной емкости счетчика, а в задатчик 11 частоты установить частоту, обратно пропорциональную значению дискрета функции g(,), то же при подаче серии импульсов на вход 13 (при наличии разрешения с нулевого выхода триггера 7), модель ветви сформирует временной интервал Т пропорциональный произведению дискретов двух функцийg(Xi- и l()

т -.т 1с п к -о

где tl

- период следования опорных импульсов;

f - опорная частота генератора импульсов;

п - величина пропорциональная дискрету функции ) (задаваемая числом импульсов в счетчике

10) ;

f - величина обратно пропорциональная дискрету функции ) (задаваемая частотой в задатчике 11). Каждая модель ветви 1 соединяется через полюс 14 со входом модели узла 3 таким образ.ом, что если имеется п моделей узлов 3, то моделей ветвей должно быть nj и каждая модель узла соединена с п моделями ветвей (т.е. в каждый узел входит п ветвей). Кроме того, выход каждой модели ветви соединен со входом блока 2 формирования топологии.

Блок 2 формирования топологии, в состав которого входят элементы 1.5, 16, 17 И Элементы 18 ИЛИ и элемент 19 НЕ, предназначен для разделения серий импульсов, поступающих из генератора 4 импульсов на входы моделей ветвей и узлов.

Модель узла 3, число которых равно числу точек дискретизации функции свертки, состоит из ячеек управляемого распределителя ,, элемента 21 ИЛИ и сумматора 22, который может быть выполнен как сумматор накапливающего типа, имеющий синхронизирующий и суммирующие параллельны поразрядные входы, и с емкостью, достаточной для хранения величины одного дискрета функции свертки FjКаждая ячейка управляемого распред лителя состоит из триггеров 23, 24 и элементов 25-28И, Каждая модель узла 3 предназнач на для последовательного накоплени в сумматоре 22 величин попарных произведений двух дискретных функц (Х-|-с-) идСх О формируемых в |Моделях ветвей, связанных с данной моделью узла, а в конце вычисления для хранения в су иматоре 22 величины, пропорциональной дискрету функции свертки F.J. Управляемый распределитель, состоящий из идентичных ячеек , чи ло которых равно числу моделей ветвей, соединенных с моделями узлов, предназначен для организации последовательного опроса моделей ветвей 1, которые сформировали свой временной ин арвал, при вычислении дис крета функции -свертки Fj . Рассмотрим работу устройства на конкретном примере. Пусть необходимо найти функцию свертки F{x) f(x-C)®g(x) при У jf 2 Oj Решение задачи заключается в получении трех значений f((,(,-i, FtX --tlV g i f -VC8 -V VC«(.ъ FLXjV-(X2-C).g(x,V f )(XiV(42.C)g(X,, - f4-C e(,H (,(г (( Для решения этой задачи устройство содержит девять моделей ветвей и три модели узла. После занесения исходной информации на выходе элемента 18 ИЛИ, разделяющего выходы моделей ветвей 1, будет низкий потенциал. Это объясняется тем, что ни одна модель ветви не сформировала свой временной интервал. С появлением пускового сигнала генератор импульсов вырабатывает н своих выходах импульсы ГИ 1, ГИ 2 и ГИ 3, сдвинутые относительно друг друга. Эти импульсы соответственно через полюса 29, 30 и 31 поступают на вход блока.2 формирования топологии. -Так как на,.выходе элемента 1 ИЛИ действует низкий потенциал,то он запрещает прохождение импульсов серии ГИ 2 и ГИ 3 через элементы 15 17 И и,инвертируясь на элементе 19 дает разрешение пройти импульсам се рии ГИ 1 через элемент 16 И на выхо блока 2 формирования топологии - по люс 13. Серия импульсов ГИ 1, являясь опорной частотой, поступает на входы всей моделей ветвей 1. Так как триггеры 7 и 8 предварительно установлены в нулевое состоя |ние, формирователи 6 всех моделей ветвей 1 начинают отсчитывать свой временной интервал. Серия импульсов iTH 1 с полюса 13 поступает также на вход счетчика 5 общего интервала, который считает число опорных импульсов . Блок 9 формирования топологии разрешает поступление на полюс 13 импульсов ГИ 1 до тех пор, пока хотя бы одна модель ветви 1 не сформирует свой временной интервал, величина которого пропорциональна произведению двух дискретов f(xj-T) и д(х). Когда это произойдет, формирователь 6 вьщает сигнал переполнения, который .устанавливает триггер 7 в единичное состояние и на выходе модели ветви-появится высокий потенциал. Сигнал переполнения поступает через полюс 14 на ВХОД блока 2 формирования топологии, проходит ч:ерез элемент 18 ИЛИ, запрещает поступление импульсов ГИ 1 на полюс 13 и разрешает прохождению импульсов ГИ 2 и ГИ 3 через элементы 15 и 17 И на полюсы 32 и 33 соответственно. С этих полюсов серии ГИ 2 поступают на вход 34 первого управляемого распределителя 20, а импульсы серии ГИ 3 поступают на входы 33 всех распределителей 20 . Распределитель 20 организует последовательный опрос моделей ветвей 1, которые сформировали свой временной интервал. Это происходит следующим образом. Предварительно триггеры 23 и-24 установлены s нулевое состояние. При сигнале формирования временного интервала из элемента 9 И через полюсы 14 на входы 25 И подаются разрешающие сигналы, которые пройдя их установят в единичное состояние триггеры 23. На нулевых выходах триггеров 23,соединённых со входами элементов 26 И, появляются запрещенные потенциалы, а на единичных выходах, соединенных со входами элементов 27 И, разрешающие потенциалы. Импульс ГИ 2, поступающий на полюс 34, пройдя элемент 27 И, через полюс 36 установит триггер 8 соответствующей модели ветви 1 и триггер 24 в единичном состоянии (если триггер 23 находился в единичном состоянии) , снимая тем сагиым разрешаюший потенциал со входа элемента 25 И и подавая разрешающий потенциал на элемент 28 И. Импульс ГИ 2 с полюса 36 поступает также через элемент 21 ИЛИ на синхронизирующий вход сумматора 22. По этому сигналу происходит сложение содержимого сумматора с параллельным кодом величины временного интервала, накопленного счетчика 5, который соединен параллельно со всеми сумматорами 22 (полюс 37), т.е. в сумматоре 22 каждой модели узла будет накапливаться величина, пропорциональная дискрету функции свер ки F;J. Затем импульс серии ГИ 3, сдвину тый относительно импульса ГИ 2, с полюса 33 и через элемент 28 И, уст навливает триггер 23 в нулевое состояние, разрешая прохождение следую щего импульса ГИ 2 со входа распределителя 20 на его выход через элемент 26 И. Импульсы с полюса 35 первого рас пределителя 20 будут передаваться от ячейки к ячейке, пропуская те ячейки, на вход элементов 25 И кото рых не были поданы разрешающие потенциалы из моделей ветвей. Это соответствует прибавлению к содержимому сумматора 22 величин временных интервалов моделей ветвей, которые окончились в данный момент. Когда все триггеры 8, моделей ветвей 1, сформировавших свой временной интервал, будут установлены в единичное состояние, т.е. на полю сах 14 не будет ни одного разрешаю щего потенциала, то блок 2 запретит серии импульсов ГИ 2 и ГИ 3 и разре шит поступление импульсов ГИ 1 в мо дели ветвей. Процесс вычислений будет продолжаться до тех пор, пока все модели ветвей не закончат свою работуг Когда процесс вычислений окончится, то в каждом сумматоре 22 будет храниться величина , пропорциональна сумме всех временных интервалов, сформированных моделями ветвей,соединенных с данной моделью узла (ди крет функции свертки). (ГГ)Г(УО- (3) Применение всех блоков устройств дискретных по принципу действия, позволяет производить вычисление оп рации свертки быстрее и точнее по сравнению с известными устройствами Результаты вычислений можно исполь вать без сложных преобразователей аналоговых сигналов в коды. Кроме того, это дает возможность автоматизировать процесс сбора информаци и передачи ее в ЦВМ. Формула изобретения 1.. Устройство для определения свертки дискретных функций, содерж щее генератор импульсов, первый и второй выходы которого подключены соответственно к первому и второму входу блока формирования топологии группа входов которого соединена с выходами моделей ветвей, первый вх каждой из которой подключен к паевому выходу блока формирования ологии, отлича. ющеес я ем, что с целью повышения точности, устройство введены модели узлов счетчик, вход которого соединен первым ;ыходом блока формирования топологии,третий вход которого соединен с третьим выходом генератора импульсов, второй и третий выходы блока формирования топологии подключены соответственно к первым и вторым входам моделей узлов, третий вход каждой из которых соединен с выходом соответствующей модели ветви,второй вход каждой модели ветви подключен к выходу соответствующей модели узла,группа входов каждой модели узла подключена к выходам счетчика. 2. Устройство по п.1 о т л и- . чающееся тем, что модель ветви содержит элементы И, триггеры задатчик частоты и счетчик импульсов, вход которого через задатчик частоты соединен с выходом первого элемента И, первый вход которого является первым входом модели, а второй вход первого элемента И соединен с первым выходом первого триггера, вход которого подключен к выходу счетчика импульсов, вход второго триггера являетсявходом модели ветви, второй выход первого и выход второго триггеров подключены соответственно к первому и второму входам второго элемента И,выход которого является выходом модели ветви. . 3. Устройство по п.1 о т л ичающееся тем, что модель содержит распределители, элемент ИЛИ, сумматор, входы которого являются группой входов модели, первым и вторьил входом которой являются соответственно первый и второй входы распределителей, выходы которых являются выходами модели и соединены с входами элемента ИЛИ, выход которого подключен к соответствующему входу сумматора. 4. Устройство по П.1, о т л ичающееся тем, что блок фэрмиров.ания топологии содержит элементы И, НЕ и элемент ИЛИ, Входы которого ЯВЛЯЮТСЯ группой входов блока, выход элемента ИЛИ. через элемент НЕ соединен с первым входом первого элемента И и непосредственно подключен к первым входам второго и третьего элементов И, вторые входы первого, второго и третьего элементов И являются соответственно первым, вторым и третьим входами блока Формирования топологии. Источники .информации. принятые во внимание при экспертизе 1.Патент США № 3931509, кл. G 06 G 7/19, 1976. 2.Авторское свидетельство СССР .422002, кл. G 06 G 7/48, 1972 (прототип).

«

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исследования сетей | 1971 |

|

SU486330A1 |

| Вычислительное устройство для решения задач сетевого планирования | 1978 |

|

SU750503A1 |

| Устройство для моделирования экстремальных путей на графе | 1980 |

|

SU926670A1 |

| Устройство для исследования графа | 1978 |

|

SU744593A1 |

| Устройство для расчета сетевыхгРАфиКОВ | 1979 |

|

SU851417A1 |

| Устройство для вычисления текущих ресурсов | 1978 |

|

SU746589A1 |

| Устройство для моделирования кратчайших путей на графе | 1971 |

|

SU485451A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1986 |

|

SU1374239A2 |

| Устройство для моделирования сетей в реальном времени | 1987 |

|

SU1509926A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1983 |

|

SU1161951A1 |

50

L

Авторы

Даты

1980-06-15—Публикация

1978-02-14—Подача