(Л

31509926

управления, блок 2 формирования топо.- логии, блок 3 моделей ветвей и генератор 4 импульсов, дополнительно введен блок связи с объектом контроля, . а в блок управления введены два узла памяти 9 и 10, триггеры внешнего прерывания 13 и фиксации опоздания операций 14, сумматор 15 величины опоздания операций, регистр-накопитель 16 сумматора, второй блок. 20 элементов Ч И, второй блок 29 элементов ИЛИ, с первого по седьмой элементы И 17-19 21-24, с первого по восьмой элементы .ИЛИ 26-28, 30, 32-35, с четвертого по девятый элементы задержки 36-39, 41 44, элементы НЕ 45 и 46. 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования сетей в реальном времени | 1990 |

|

SU1751782A1 |

| Устройство для моделирования направленных графов | 1986 |

|

SU1322304A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1986 |

|

SU1374239A2 |

| Устройство для анализа параметров сети | 1986 |

|

SU1548793A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1987 |

|

SU1509925A2 |

| Устройство для решения сетевых задач | 1988 |

|

SU1564643A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1983 |

|

SU1161951A1 |

| Устройство для определения длиннейшего пути в сетях | 1986 |

|

SU1339581A1 |

| Устройство для определения характеристик сетей | 1984 |

|

SU1282151A1 |

| Устройство для определения характеристик сетей | 1984 |

|

SU1242980A1 |

Изобретение относится к вычислительной технике и может быть использовано для решения задач управления и теории графов, а также при построении специализированных вычислительных машин для моделирования сетевых задач и сопряжения их с объектом в реальном масштабе времени. Цель изобретения - расширение функциональных возможностей - достигается тем, что в устройство, содержащее блок 1 управления, блок 2 формирования топологии, блок 3 моделей ветвей и генератор 4 импульсов, дополнительно введен блок связи с объектом контроля, а в блок управления введены два узла памяти 9 и 10, триггеры внешнего прерывания 13 и фиксации опоздания операций 14, сумматор 15 величины опоздания операций, регистр -накопитель 16 сумматора, второй блок 20 элементов И, второй блок 29 элементов ИЛИ, с первого по седьмой элементы И 17-19, 21-24, с первого по восьмой элементы ИЛИ 26-28,30,32-35, с четвертого по девятый элементы задержки 36-39, 41,44, элементы НЕ 45 и 46. 3 ил.

Изобретение относится к вычисли- тельной технике, в частности к спе- циализированньот вычислительным устройствам для решения задач управления и теории графов, и может быть использовано при построении специализиро- ванных машин для моделирования сетевых задач и сопряжения их с объектом в реальном масштабе времени.

Цель изобретения - расширение функциональных возможностей устройства путем обеспечения оперативного контроля выполнения работ по сетевому проекту в реальном времени.

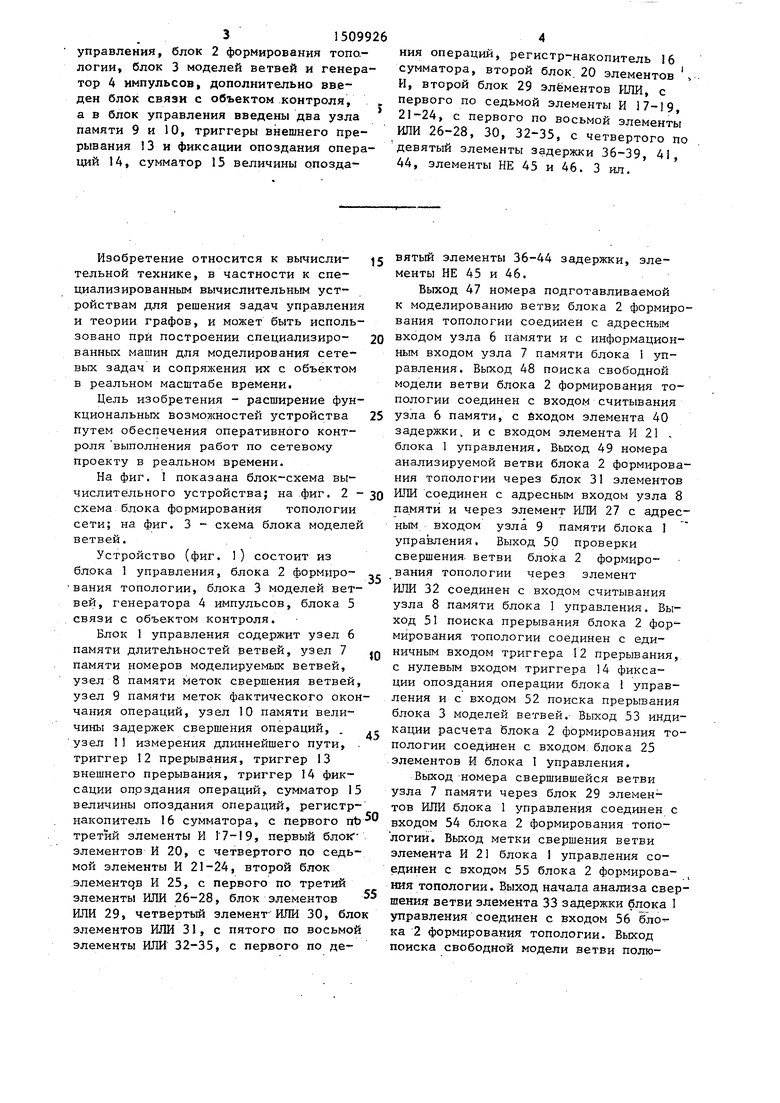

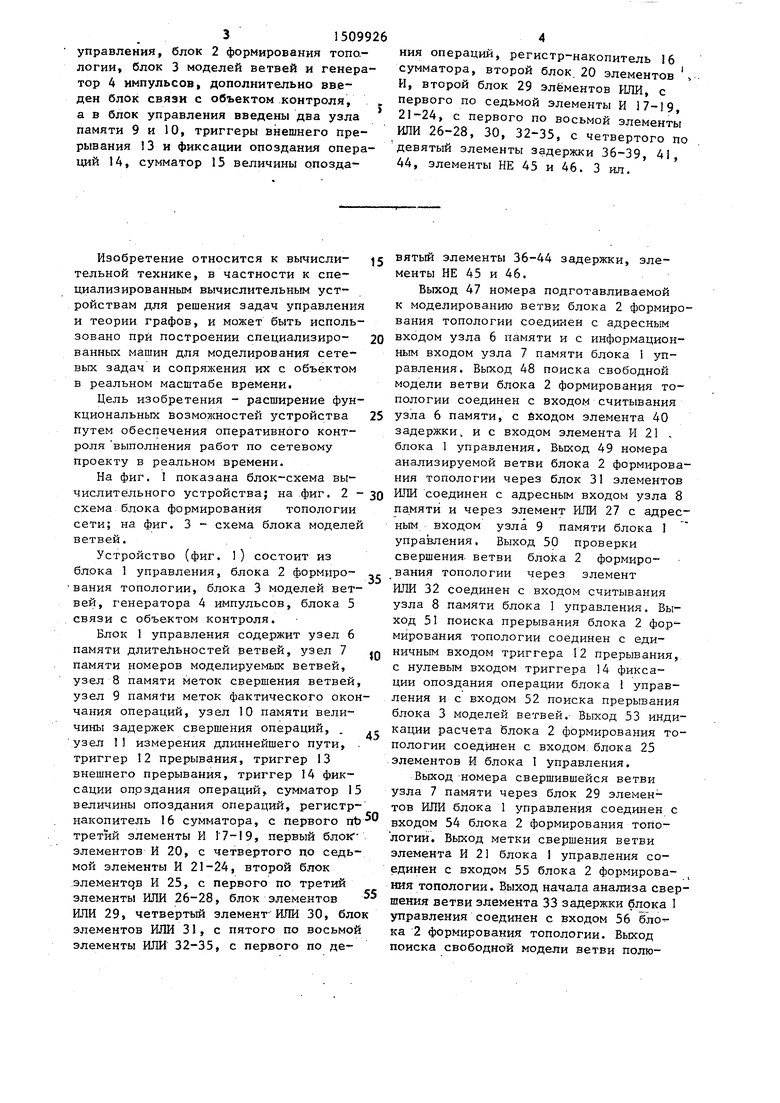

На фиг. 1 показана блок-схема вычислительного устройства; на фиг. 2 - схема блока формирования топологии сети; на фиг. 3 - схема блока моделей ветвей.

Устройство (фиг. 1) состоит из

блока 1 управления, блока 2 формиро35

вания топологии, блока 3 моделей ветвей, генератора 4 импульсов, блока 5 связи с объектом контроля.

Блок 1 управления содержит узел 6 памяти длительностей ветвей, узел 7 ,Q памяти номеров моделируемых ветвей, узел 8 памяти меток свершения ветвей, узел 9 памяти меток фактического окончания операций, узел 10 памяти величины задержек свершения операций, . . узел 11 измерения длиннейшего пути, . триггер 12 прерывания, триггер 13 внешнего прерывания, триггер 14 фиксации опрздания операций, сумматор 15 величины опоздания операций, регистр- накопитель 16 сумматора, с первого пЬ третий элементы И 7-19, первый элементов И 20, с четвертого до седьмой элементы И 21-24, второй блок элeмeнтqв И 25, с первого по третий элементы ИЛИ 26-28, блок элементов ИЛИ 29 четвертый элемент-ИЛИ 30, блок элементов ИЛИ 31, с пятого по восьмой элементы ИЛИ 32-35, с первого по де50

5 0

5

О

5

Q

0

вятый элементы 36-44 задержки, элементы НЕ 45 и 46.

Выход 47 номера подготавливаемой к моделированию ветвк блока 2 формирования топологии соединен с адресным входом узла 6 памяти и с информационным входом узла 7 памяти блока 1 управления. Выход 48 поиска свободной модели ветви блока 2 формирования топологии соединен с входом считывания узла 6 памяти, с Входом элемента 40 задержки, и с входом элемента И 21 . блока 1 управления. Выход 49 номера анализируемой ветви блока 2 формирования топологии через блок 31 элементов ИЛИ соединен с адресным входом узла 8 памяти и через элемент ИЛИ 27 с адресным входом узла 9 памяти блока 1 управления. Выход 50 проверки свершения, ветви блока 2 формирования топологии через элемент ИЛИ 32 соединен с входом считывания узла 8 памяти блока управления. Выход 51 поиска прерывания блока 2 формирования топологии соединен с единичным входом триггера 12 прерывания, с нулевым входом триггера 14 фиксации опоздания операции блока 1 управления и с входом 52 поиска прерывания блока 3 моделей ветвей. Выход 53 индикации расчета блока 2 формирования топологии соединен с входом, блока 25 элементов И блока 1 управления.

Выход номера свершившейся ветви узла 7 памяти через блок 29 элементов ИЛИ блока 1 управления соединен с входом 54 блока 2 формирования топологии. Выход метки свершения ветви элемента И 21 блока 1 управления соединен с входом 55 блока 2 формирования топологии. Выход начала анализа свершения ветви элемента 33 задержки блока 1 управления соединен с входом 56 блока 2 формирования топологии. Выход поиска свободной модели ветви полюсоединен с входом 57 блока 3 моделей ветвей.Выход измерительной серии элемента ИЛИ 34 блока 1 управления соединен с входом 58 блока 3 моделей ветвей. Выход кода длительности ветви узла 6 памяти блока 1 управления соединен с входом 59 блока 3 моделей ветвей.

Выход 60 номера модели ветви блока 3 моделей ветвей соединен с адресным входом узла 7 памяти блока 1 управления. Выход 6 прерывания блока 3

10

сети с целью определения величины длиннейшего пути контролируемого п цесса, а также с целью определения личины задержек операций контролиру мого процесса. Блок 2 формирования пологий предназначен для коммутаци моделей ветвей по заданной топологии сети, которая заключается в определении номеров ветвей, входящ в исследуемый узел сети, и номеров ветвей, выходящих из исследуемого ла сети, а также для определения с

моделей ветвей соединен с входом счи- 15 шения конечного узла сети. Блок 3

тывания узла 7 памяти, с входом элемента 42 задержки и через элемент ИЛИ 35 с нулевым входом триггера 2 прерывания бло ка 1 управления.

Выход сигнала ответа элемента ИЛИ 26 блока 1 управления соединен с входом 62 блока 5 связи с объектом контроля. Выход 63 сигнала фактического окончания операции в контролируемом объекте блока 5 связи с объектом контроля соединен с единичным входом триггера 13 внешнего прерьшания и с входом записи узла 9 памяти блока 1 управления. Выход 64 номера фактически окончившейся операции в контролируемом объекте блока 5 связи с объектом контроля соединен с входом блока 20 элементов И блока 1 управления.

Входной полюс 65 блока 2 формирования топологии предназначен для приема импульсов серии ГИ1, поступающих с генератора 4 импульсов. Входной полюс 66 блока I управления и входной полюс 67 блока 2 формирования топологии предназначен для приема импульсов серии ГИ2, поступающих с генератора 4 импульсов. Входной полюс 68 блока 1. управления предназначен для приема импульсов измерительной серии поступающих с генератора 4 импульсов с установленной дискретностью контроля за реально протекающим технологическим процессом. Входными полюсами устройства являются полюса 69 и 70 блока 1 управления и полюс 71 генератора 4 импульсов. Выходным полюсом устройства является полюс 72 блока 1 управления, соединенный с выходом блока 25 элементов И..

В устройстве (фиг. 1) блок 1 управления предназначен для организации взаимодействия между блоком 2 формирования топологии, блоком 3 моделей ветвей и блоком 5 связи с контролиру20

25

30

35

40

45

50

моделей ветвей предназначен для о ганизации процесса временного моделирования длительностей ветвей сети. Генератор 4 импульсов предназначен для формирования сери импульсов ГИ1 и ГИ2, сдвинутых оди относительно другого, а также для мирования импульсов измерительной рии с дискретностью, обеспечивающе необходимый контроль протекания ре ного процесса с требуемой точностью Причем импульсы ГИ1 и ГИ2 вырабаты ются с частотой, большей частоты им пульсов измерительной серии на стол ко, чтобы между импульсами измерите ной серии были выполнены все вычисл тельные процессы, связанные с форми ванием топологии сети. Блок 5 связи с контролируемым объектом предназна чен для организации связи предлагае мого устройства с контролируемым об ектом с целью получения информации факте и номере свершившейся на объе те операции.

В блоке 1 управления (фиг.1) узел памяти длительностей ветвей предназ начен, для хранения информации о величинах длительностей ветвей сети, именно для хранения по адресу номер ветви кода длительности данной вет ви. Узел 7 памяти номеров моделируемых ветвей предназначен для хранен информации о соответствии номера мо дели ветви из блока 3 моделей ветве

номеру .ветви сети, моделируемой в т кущий момент времени данной моделью ветви. Узел 8 памяти меток свершени ветвей сети предназначен для хранен информации о завершении процесса вр менного моделирования длительностей ветвей сети. Узел 9 памяти меток фа тического окончания операций предна начен для хранения информации об ок чании операций HI контролируемом об

сети с целью определения величины длиннейшего пути контролируемого процесса, а также с целью определения величины задержек операций контролируемого процесса. Блок 2 формирования тот пологий предназначен для коммутации моделей ветвей по заданной топологии сети, которая заключается в определении номеров ветвей, входящих в исследуемый узел сети, и номеров ветвей, выходящих из исследуемого узла сети, а также для определения свершения конечного узла сети. Блок 3

5 шения конечного узла сети. Блок 3

0

5

0

5

0

5

0

моделей ветвей предназначен для организации процесса временного моделирования длительностей ветвей сети. Генератор 4 импульсов предназначен для формирования серий импульсов ГИ1 и ГИ2, сдвинутых один относительно другого, а также для формирования импульсов измерительной серии с дискретностью, обеспечивающей необходимый контроль протекания реального процесса с требуемой точностью. Причем импульсы ГИ1 и ГИ2 вырабатываются с частотой, большей частоты импульсов измерительной серии на столько, чтобы между импульсами измерительной серии были выполнены все вычислительные процессы, связанные с формированием топологии сети. Блок 5 связи с контролируемым объектом предназначен для организации связи предлагаемого устройства с контролируемым объектом с целью получения информации о факте и номере свершившейся на объекте операции.

В блоке 1 управления (фиг.1) узел 6 памяти длительностей ветвей предназначен, для хранения информации о величинах длительностей ветвей сети, а именно для хранения по адресу номера ветви кода длительности данной ветви. Узел 7 памяти номеров моделируемых ветвей предназначен для хранения информации о соответствии номера модели ветви из блока 3 моделей ветвей .

номеру .ветви сети, моделируемой в текущий момент времени данной моделью ветви. Узел 8 памяти меток свершения ветвей сети предназначен для хранения информации о завершении процесса временного моделирования длительностей ветвей сети. Узел 9 памяти меток фактического окончания операций предназначен для хранения информации об окончании операций HI контролируемом объекте. Узел 10 памяти величины задер-, жек операций предназначен для хранения информации о величине отклонения времени фактического окончания операций контролируемого объекта по сравнению с расчетным временем. Узел 11 измерения длиннейшего пути предназначен для формирования величины длительности длиннейшего пути сети в относитель ных единицах и может быть выполнен в виде, счетчика со счетным входом и параллельной выдачей информации.

Триггер 12 прерывания предназначен для организации временного разделения между процессом временного моделирования длительностей ветвей сети и процессом анализа топологии моделируемой сети. Триггер 13 внешнего прерывания предназначен для организации обработ- ки внешнего прерывания при окончании операций в контролируемом объекте. Триггер 14 фиксации опознания операций предназначен для организации процесса вычисления величины фактическо- го опоздания выполнения операций на контролируемом объекте. Сумматор 15 величины опоздания операций служит для получения разности двух кодов,поступающих на его входы, которая опре- деляет величину опоздания выполнения операций на контролируемом объекте. Регистр-накопитель 16 сумматора предназначен для промежуточного хранения величины опоздания операций и может быть выполнен по схеме регистра хранения с параллельным приемом и вьща- чей информации.

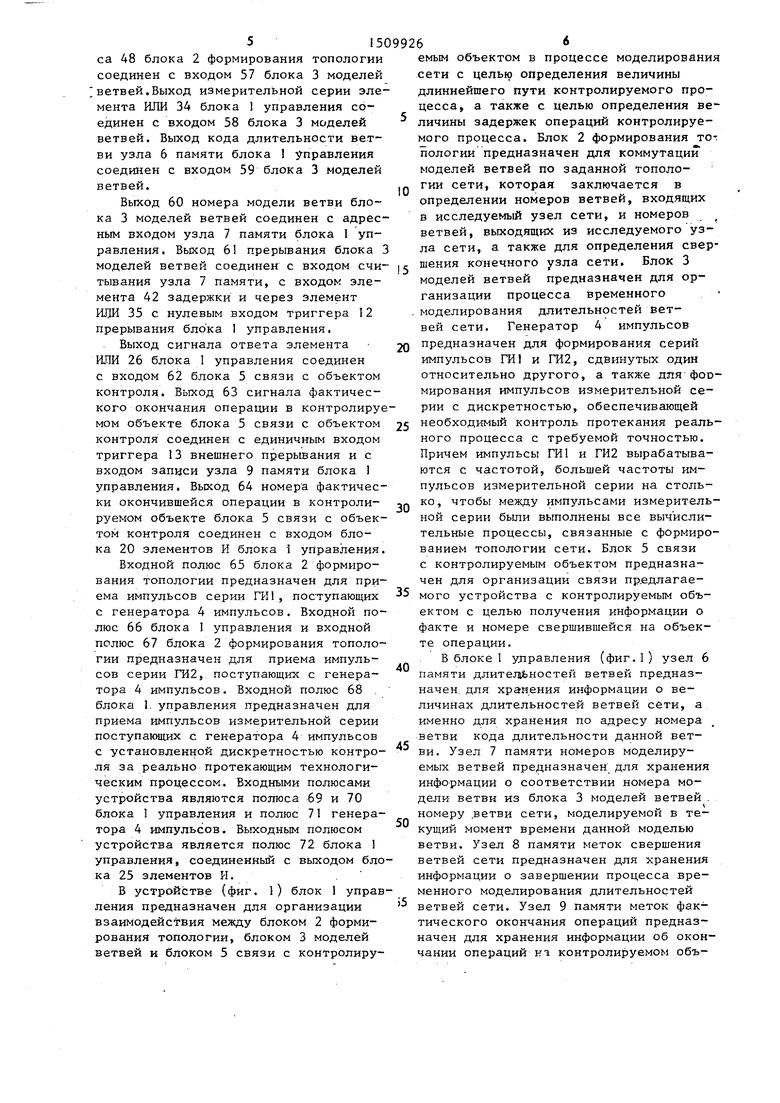

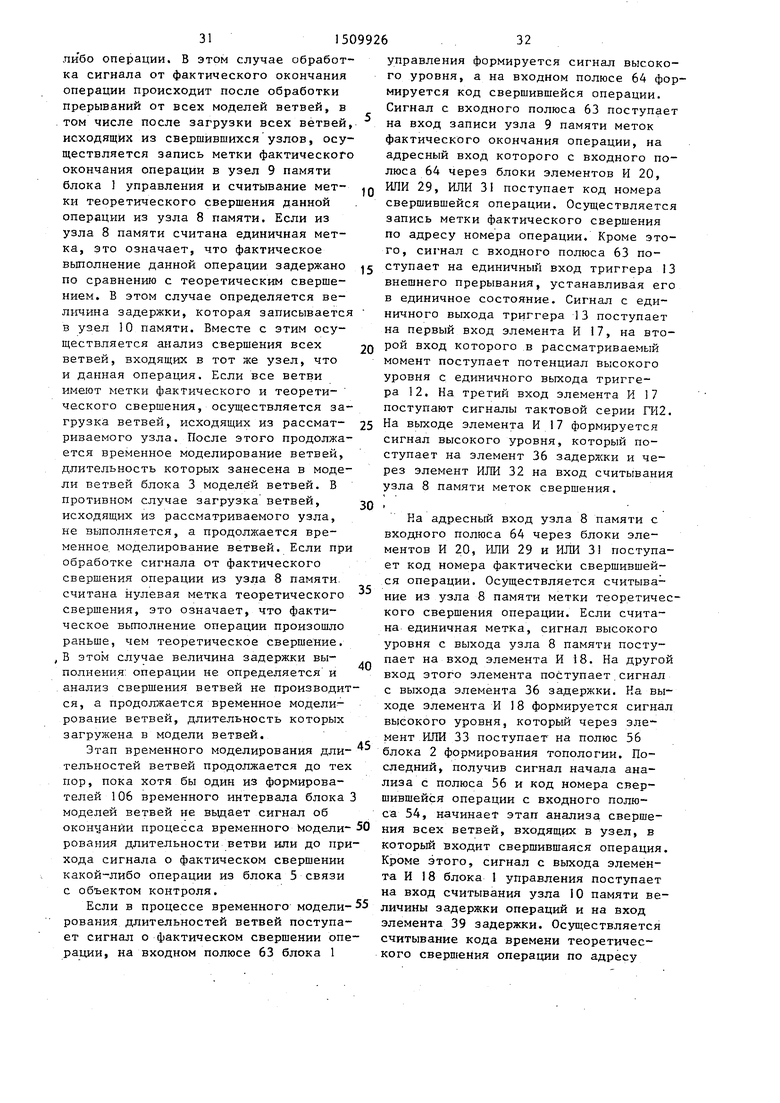

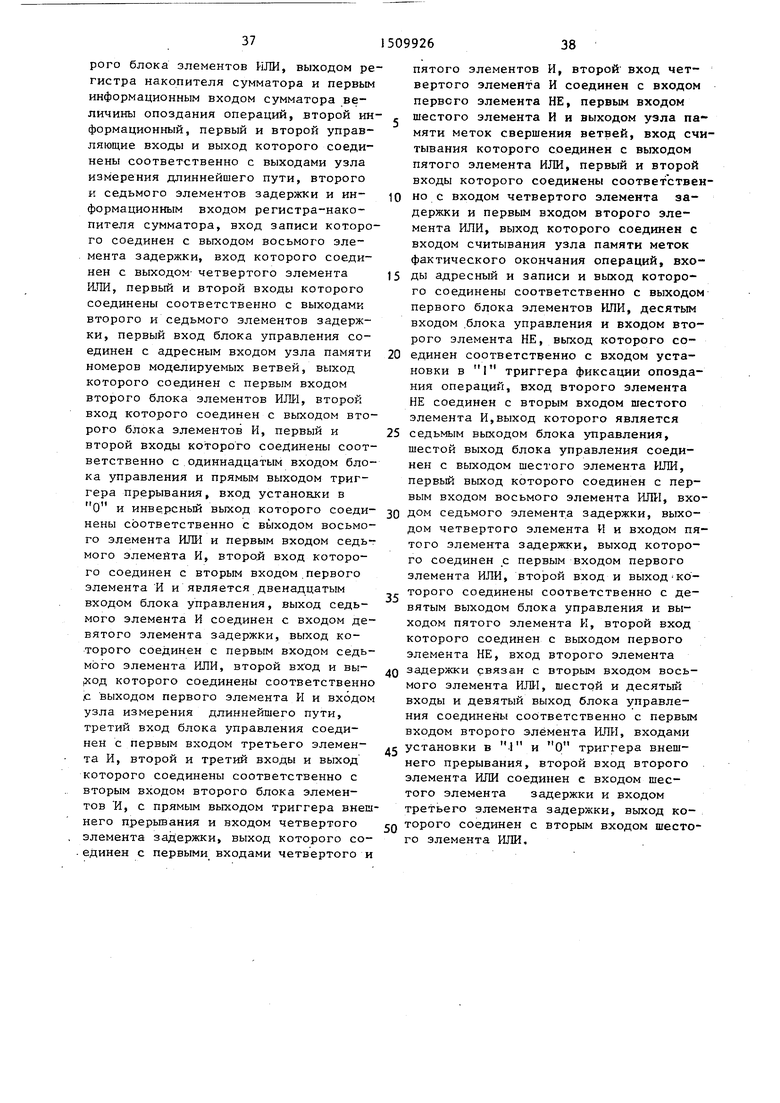

Блок 2 формирования топологии (фиг. 2) содержит узел 73 памяти номеров начальных узлов ветвей сети, узел 74 памяти номеров конечных узлов ветвей сети, узел 75 памяти номеров выходящих ветвей узлов сети, узел 76 памяти Номеров входящих ветвей узлов сети, узел 77 памяти номеров первой выходящей ветви узлов сети, узел 78 памяти номеров первой входящей- ветви узлов сети, регистр 79 номера выходящей ветви, регистр 80 номера входящей ветви, регистр 81 но- мера конечного узла ветви, регистр 82 номера конечного узла сети, триггеры 83 и 84, дешифраторы 85 и 86, схему 87 сравнения кодов, элементы И 88- 93, элементы ИЛИ 94-100, элементы 101 и 102 задержки, элемент НЕ 103.

Входами блока являются полюса 69 и 70, соединенные соответственно с

Q

д 0 5 о

5

5

0

5

адресным входом и входом считывания узла 73 памяти номеров начальных узлов ветвей сети. Вход 54 номера свершившейся ветви сети соединен с адресным входом узла 74 памяти номеров конечных узлов ветвей сети. Вход 56 начала анализа свершения ветви соединен с входом считывания узла 74 памяти номеров конечных узлов ветвей сети. Вкод 55 метки свершения ветви через элемент НЕ 103 и элемент ИЛИ 99 соединен с нулевым входом триггера 83.

Выход 51 поиска прерывания блока 2 формирования топологии соединен с выходом элемента ИЛИ 96. Выход 47 номера подготавливаемой к моделированию ветви соединен с выходом регистра 79 адреса выходящей ветви. Выход 49 номера анализируемой ветви соединен с выходом регистра 80 адреса входящей ветви. Выход 48 поиска свободной модели ветви соединен с выходом элемента И 91. Выход 50 проверки свершения ветви соединен с выходом элемента И 89. Выход 53 индикации расчета соединен с выходом элемента И 93.

. Узлы 73-78 памяти блока 2 формирования топологии предназначены для хранения информации о топологии моделируемой сети: узел 73 памяти - для хранения, по адресу номера каждой ветви сети номера ее начального узла, узел.74 памяти - для хранения по адресу номера каждой ветви сети номера ее конечного узла, узел 77 памяти - для хранения по адресу номера узла номера первой выходящей из этого узла ветви, узел 78 памяти - для хранения по. адресу номера узла номера первой входящей в данный узел ветви, узел 75 памяти - для хранения в виде списков номеров ветвей,.выходящих из узлов сети, узел 76 памяти предназначен для хранения в виде списков номеров ветвей, входящих в узлы сети.

Регистр 79 предназначен для промежуточного хранения номера ветви при определении ветвей, выходящих из узла. Регистр 79 может быть выполнен в виде регистра хранения с установкой и выдачей параллельного кода. Регистр 80 предназначен для промежуточного хранения номеров ветвей при определении ветвей, входящих в узел, и может быть вьтолнен аналогично регистру 79. Регистры 81 и 82 вьтолнены аналогичным образом и предназначены для хранения номера анализируемого узла и конечного

узла сети соответственно. Схема 87 сравнения кодов предназначена Для поразрядного сравнения кодов и выдает сигнал в случае равенства кодов, подаваемых на ее входы. Дешифраторы 85 и 86 состояния X предназначены для сравнения поступающих на них кодов с кодовой комбинацией состояния X, заданного постоянно в схеме.

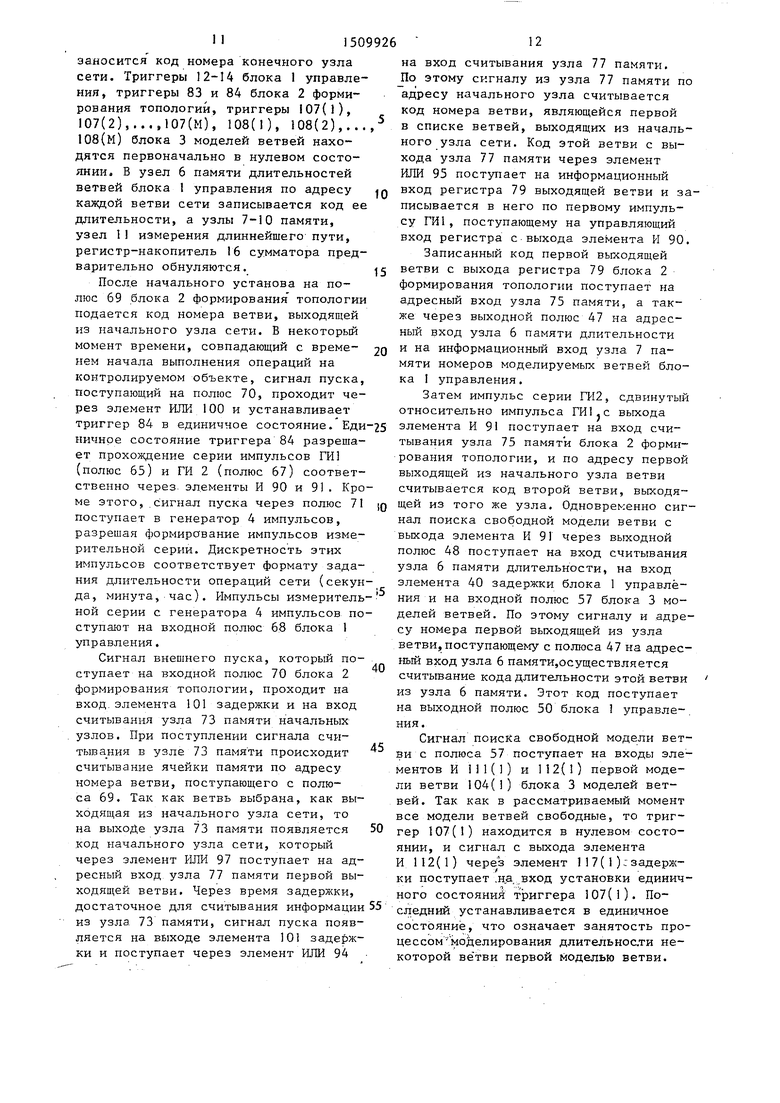

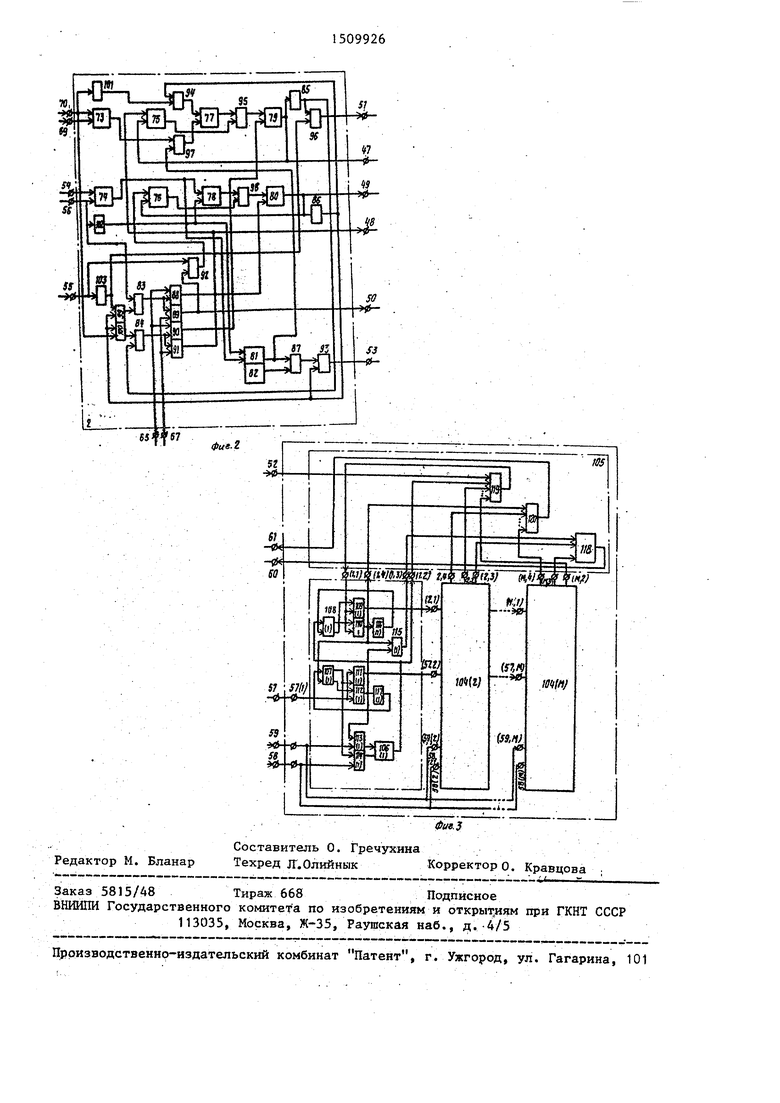

Блок 3 моделей ветвей (фиг. З) содержит М моделей ветвей 104 (l), , 104 (2),...,104(М) и узла 105 поиска моделей ветвей.(цифрами в скобках обозначены порядковые номера совершенно одинаковых по своему конструктивному исполнению и функциональному назначению блоков, узлов, элементов и полюсов).

Каждая модель ветви 104 (фиг. З) состоит из формирователя 106 временных интервалов, триггеров 107 и 108, элементов И 109-114, элемента И 115, элементов 116 и 117 задержки.

Схема узла поиска моделей ветвей (фиг. 3) содержит шифратор 1 1-8 адреса и элементы ИЛИ 119 и 120.

Входы 59 (1), 59 (2)59 (м)

кода длительности ветви блока моделей ветвей соединены с входами элементов И 113 (1), 113(2),...,113(М). Входы 58(1), 58(2),...,58(М) измерительной серии импульсов соединены с входами элементов И 114 (l), 1 14( 2),.. . , 1 14(М Вход 57 (1) поиска свободной модели ветви соединён с входом элемента И 112 (1) первой модели ветви 104 (1) Выход элемента И 111 (1) первой модели ветви 104 () соединен с входом 57 (2) поиска свободной модели ветви второй модели ветви 104 (2), выход элемента И 1 Г1 (2) второй модели ветви 104 (2) соединен с входом 57 (З поиска свободной модели ветви третьей модели ветви 104 (З) и т.д. Вход 5 поиска прерывания соединен с входом элемента ИЛИ 119 узла 105 поиска моделей ветвей блока 3 моделей ветвей. Выход элемента ИЛИ 119 узла 105 поиска моделей ветвей соединен с входом поиска прерывания (1,1) первой модели ветви 104 (1) (первая цифра в скобках обозначает более высокий в иерархии порядковый номер, т.е. номер

модели ветви, а вторая - более низкий в иерархии, т.е. порядковый номер вхо да или выхода этой модели).

Входы (1,1),. (2, ),..., (y ) поиска прерывания моделей ветвей 104 (1),

.

10

104 (2),...,104(М) соединены с входами элементов 109(1), 109(2),...,109(М) и 110(1), 110(2),...,110(М). Выход элемента 109(1) первой модели ветви 104(1) соединен с входом (2,1) поиска прерывания второй модели ветви 104(2), выход элемента И 109(2) второй модели ветви 104(2) соединен с входом СЗ.1) поиска прерывания третьей модели ветви 104(3) и т.д. Выходы (1,2),(2,2), ,...,(М2) переполнения формирователей 106(0, 106(2),..., 106(М) временных интервалов моделей ветвей 104(1), J5 104(2),...,104(М) соединены с входами элемента ИЛИ 119 узла 105 поиска моделей ветвей. Выходы ( 1,4),(2,4),..., (М) сигналов прерывания с выходов элементов И 110 (I), 110(2),...,110(М) 20 соединены с входами элемента ИЛИ 120 узла 105 поиска моделей ветвей. Выходы (I,3),(2,3),...,(М,3) сигнала моделей ветвей с выходов элементов ИЛИ 115(1), 115(2),...,115(М) моделей 25 ветвей 104(1), 104(2),...,104(М) соединены с входами шифратора 118 адреса узла 105 поиска моделей ветвей. Выход 61 прерывания блока 3 моделей ветвей соединен с выходом элемента 30 ИЛИ 120 узла 105 поиска моделей ветвей. Выход 60 номера модели ветви блока 3 моделей ветвей соединен с выходом шифратора 118 адреса узла 105 поиска моделей ветвей.

Формирователи 1рб(1),106(2),..., 106(М) временного интервала моделей ветвей 104(1), 04(2),...,104(М) предназначены для временного моделирования длительностей ветвей сети и могут быть выполнены в виде двоичного счетчика с параллельным входом исходной информации.

Шифратор 118 адреса узла 105 поиска моделей ветвей предназначен для формирования кода номера каждой модели ветви.

Работа устройства рассматривается на примере вычисления длиннейшего пути с одновременным контролем выполнения операций на реальном объекте и определением величины задержки выполнения операций.

Устройство работает следующим образом.

В узлы 73-78 памяти блока 2 формирования топологии в виде списков заносится информация о топологии моде- лируембй сети. Регистры 79-81 предварительно обнуляются, а в регистр 82

Ю

45

;о

5

1

заносится код номера конечного узла сети. Триггеры 12-14 блока 1 управления, триггеры 83 и 84 блока 2 формирования топологии, триггеры 107(1), 107(2),..,,107(М), 108(1), 108(2),... 108(М) блока 3 моделей ветвей находятся первоначально в нулевом состоянии. В узел 6 памяти длительностей ветвей блока 1 управления по адресу каждой ветви сети записывается код ее длительности, а узлы 7-10 памяти, узел 1 измерения длиннейшего пути, регистр-накопитель 16 сумматора предварительно обнуляются.

После начального установа на полюс 69 блока 2 формирования топологии подается код номера ветви, выходящей из начального узла сети. В некоторьш момент времени, совпадающий с време- нем начала выполнения операций на контролируемом объекте, сигнал пуска, поступающий на полюс 70, проходит через элемент ИЛИ 100 и устанавливает триггер 84 в единичное состояние. Еди ничнре состояние триггера 84 разрешает прохождение серии импульсов П-П (полюс 65) и ГИ 2 (полюс 67) соответственно через элементы И 90 и 91. Кроме этого,.сигнал пуска через полюс 71 поступает в генератор 4 импульсов, разрешая формирование импульсов измерительной серии. Дискретность этих импульсов соответствует формату задания длительности операций сети (секунда, минута, час). Импульсы измерительной серии с генератора 4 импульсов поступают на входной полюс 68 блока 1 управления.

Сигнал внешнего пуска, который поступает на входной полюс 70 блока 2 формирования топологии, проходит на вход.элемента 101 задержки и на вход считывания узла 73 памяти начальных узлов. При поступлении сигнала считывания в узле 73 памяти происходит считывание ячейки памяти по адресу номера ветви, поступающего с полюса 69. Taic как ветвь выбрана, как выходящая из начального узла сети, то на выходе узла 73 памяти появляется код начального узла сети, который через элемент РШИ 97 поступает на адресный вход узла 77 памяти первой выходящей ветви. Через время задержки, достаточное для считывания информации из узла 73 памяти, сигнал пуска появляется на выходе элемента 101 задержки и поступает через элемент ИЛИ 94

926

, п5

20 -25 JQ

50 55

40

12

на вход считывания узла 77 памяти. JIo этому сигналу из узла 77 памяти по адресу начального узла считывается код номера ветви, являющейся первой в списке ветвей, выходящих из начального узла сети. Код этой ветви с выхода узла 77 памяти через элемент ИЛИ 95 поступает на информационный вход регистра 79 выходящей ветви и записывается в него по первому импульсу ГИ1, поступающему на управляющий вход регистра с-выхода элемента И 90.

Записанный код первой выходящей ветви с выхода регистра 79 блока 2 формирования топологии поступает на адресный вход узла 75 памяти, а также через выходной полюс 47 на адресный вход узла 6 памяти длительности и на информационный вход узла 7 памяти номеров моделируемых ветвей блока I управления.

Затем импульс серии ГТ12, сдвинутый относительно импульса ГИ1.с выхода элемента И 91 поступает на вход считывания узла 75 памяти блока 2 формирования топологии, и по адресу первой выходящей из начального узла ветви считывается код второй ветви, выходящей из того же узла. Одновременно сигнал поиска свободной модели ветви с выхода элемента И 9 через выходной полюс 48 поступает на вход считывания узла 6 памяти длительности, на вход элемента 40 задержки блока 1 управления и на входной полюс 57 блока 3 моделей ветвей. По этому сигналу и адресу номера первой выходящей из узла ветви, поступающему с полюса 47 на адресный вход узла 6 памяти,осуществляется считывание кода длительности этой ветви из узла 6 памяти. Этот код поступает на выходной полюс 50 блока 1 управле-. ния.

Сигнал поиска свободной модели ветви с полюса 57 поступает на входы элементов И 111(1) и 112(1) первой модели ветви 104(1) блока 3 моделей ветвей. Так как в рассматриваемый момент все модели ветвей свободные, то триггер 107(1) находится в нулевом состоянии, и сигнал с выхода элемента И 112(1) через элемент 117(1):задержки поступает на, .вход установки единичного состояния триггера 107(1). Последний устанавливается в единичное состояние, что означает занятость процессом мойелирования длительности некоторой ве тви первой моделью ветви.

13

Кроме этого, сигнал с выхода элемента И 112(1) поступает на первый вход элемента И 113() и через элемент ИЛИ 115(1) на вход шифратора 118 адреса узла 105 поиска моделей ветвей. На второй вход элемента И 113(1) первой модели ветви 104(1) через полюс 59 поступает код длительности ветви, который заносится в качестве исходной Q информации в формирователь 106(1) временного интервала. По сигналу, который с выхода элемента И 112(1) через элемент ИЛИ 115(1) и полюс (1,3) по509926. 14

импульса ГИ2 на входном полюсе 48 блока 1 управления появится сигнал иска свободной модели, по которому осуществляется считывание длительно ти ветви из .узла 6 памяти. Код длительности ветви с выхода узла 6 пам ти через полюс 59 поступает на вход элементов И П3(1), 1 13(2),. .. , f 13( всех моделей ветвей блока 3 моделей ветвей.

Кроме этого, сигнал поиска свобо ной модели ветви с входного полюса блока 1 .управления через полюс 57 п

ступает на вход шифратора 118 адреса, ступает на входы элементов И lll(l)

и 112(1) первой модели ветви 104(1) блока 3 моделей ветвей. Так как три гер 107(1)первой модели ветви наход ся в единичном состоянии, означающе занятость первой модели ветви, то с нал с выхода элемента I1 1 (1 ) через полюс 57(2) поступает на входы элем тов И 111(2) и 112(2) второй модели 104(2) ветви. Так как триггер 107(2 второй модели ветви находится в нуле вом состоянии, то сигнал с выхода эл мента И 112(2) поступает на вход эле мента И 113 (2) ив формирователь 106(2) временных интервалов второй модели ветви 104(2) вводится информа ция о коде длительности подготавлива емой к моделированию ветви. Одновременно сигнал с выхода элемента И 112(2) через элемент 117(2) задержки устанавливает триггер 107(2) в единичное состояние. Кроме этого, сигна с выхода элемента И 112(2) через эле мент ИЛИ 115 (2) и полюс (2,3) посту пает на вход щифратора 118 адреса уз ла 105 поиска моделей ветвей. По это му сигналу формируется код номера второй модели ветви, который через полюс 60 поступает на адресный вход узла 7 памяти номеров моделируемых ветвей блока 1 управления. На вход з писи узла 7 па.мятй поступает сигнал с выхода элемента 40 задержки. Проис ходит запись кода номера второй ветви, выходящей из начального узла сет по адресу найденной свободной модели

формируется код номера модели ветви, Этот код через полюс 60 поступает на адресный вход узла 7 памяти номеров моделируемых ветвей блока 1 управления .

На вход записи узла 7 .памяти поступает сигнал поиска свободной модели ветви с выхода элемента 40 задержки. Осуществляется запись по адресу номера выбранной модели ветви (в данном случае первой ), номера ветви, длительность которой уже внесена в формирователь 06(l) временного интервала данной модели ветви 104(1 ) блока 3 моделей ветвей. На этом заканчивается подготовка первой ветви, выходящей из начального узла сети, к процессу временного моделирования длительности При подготовке к моделированию ветви осуществляется, считывание номера данной ветви, считывание ее длительности, поиск свободной от вычислений модели ветви, запись кода длительнос- ти ветви в формирователь временного- интервала найденной свободной модели ветви, формирование кода найденной свободной модели ветви и запись номера подготавливаемой ветви сети по адресу номера модели в узел памяти номеров моделируемых ветвей.

Считанный по адресу номера первой выходящей ветви из узла 75 памяти выходящих ветвей блока 2 формирования топологии номер следующей ветви из

и 112(1) первой модели ветви 104(1) блока 3 моделей ветвей. Так как триг гер 107(1)первой модели ветви находи ся в единичном состоянии, означающем занятость первой модели ветви, то си нал с выхода элемента I1 1 (1 ) через полюс 57(2) поступает на входы элемен тов И 111(2) и 112(2) второй модели 104(2) ветви. Так как триггер 107(2) второй модели ветви находится в нулевом состоянии, то сигнал с выхода эле мента И 112(2) поступает на вход элемента И 113 (2) ив формирователь 106(2) временных интервалов второй модели ветви 104(2) вводится информация о коде длительности подготавливаемой к моделированию ветви. Одновременно сигнал с выхода элемента И 112(2) через элемент 117(2) задержки устанавливает триггер 107(2) в единичное состояние. Кроме этого, сигнал с выхода элемента И 112(2) через элемент ИЛИ 115 (2) и полюс (2,3) поступает на вход щифратора 118 адреса узла 105 поиска моделей ветвей. По этому сигналу формируется код номера второй модели ветви, который через полюс 60 поступает на адресный вход узла 7 памяти номеров моделируемых ветвей блока 1 управления. На вход за писи узла 7 па.мятй поступает сигнал с выхода элемента 40 задержки. Происходит запись кода номера второй вет ви, выходящей из начального узла сети по адресу найденной свободной модели

списка выходящих из узла ветвей поступает на информационный вход регист-50 ветви, ра 79 и записывается в него с приходом на установочный вход второго импульса ГИ. Записанный в регистр 79 код вновь поступает на адресный вход узла 75 памяти, а также через полюс 4755 вания их длительности. Это происходи- на адресный вход узла 6 памяти и на ло до тех пор, пока не считана по- . информационный вход узла 7 памяти блока 1 управления. С приходом второго

Так осуществляется подготовка ветвей, выходящих из начального узла сети, к процессу временного моделироследняя ветвь из списка выходящих из начального узла ветвей. При этом по

Q926. 14

импульса ГИ2 на входном полюсе 48 блока 1 управления появится сигнал поиска свободной модели, по которому осуществляется считывание длительное ти ветви из .узла 6 памяти. Код длительности ветви с выхода узла 6 памяти через полюс 59 поступает на входы элементов И П3(1), 1 13(2),. .. , f 13(М) всех моделей ветвей блока 3 моделей ветвей.

Кроме этого, сигнал поиска свободной модели ветви с входного полюса 48 блока 1 .управления через полюс 57 по ступает на входы элементов И lll(l)

0

0

5

5

0

и 112(1) первой модели ветви 104(1) блока 3 моделей ветвей. Так как триггер 107(1)первой модели ветви находится в единичном состоянии, означающем занятость первой модели ветви, то сигнал с выхода элемента I1 1 (1 ) через полюс 57(2) поступает на входы элементов И 111(2) и 112(2) второй модели 104(2) ветви. Так как триггер 107(2) второй модели ветви находится в нулевом состоянии, то сигнал с выхода элемента И 112(2) поступает на вход элемента И 113 (2) ив формирователь 106(2) временных интервалов второй модели ветви 104(2) вводится информация о коде длительности подготавливаемой к моделированию ветви. Одновременно сигнал с выхода элемента И 112(2) через элемент 117(2) задержки устанавливает триггер 107(2) в единичное состояние. Кроме этого, сигнал с выхода элемента И 112(2) через элемент ИЛИ 115 (2) и полюс (2,3) поступает на вход щифратора 118 адреса узла 105 поиска моделей ветвей. По этому сигналу формируется код номера второй модели ветви, который через полюс 60 поступает на адресный вход узла 7 памяти номеров моделируемых ветвей блока 1 управления. На вход записи узла 7 па.мятй поступает сигнал с выхода элемента 40 задержки. Происходит запись кода номера второй вет - ви, выходящей из начального узла сети, по адресу найденной свободной модели

0 ветви, 5 вания их длительности. Это происходи- ло до тех пор, пока не считана по-

ветви, вания их длительности. Это происходи- о до тех пор, пока не считана по-

Так осуществляется подготовка ветвей, выходящих из начального узла сети, к процессу временного моделироветви, вания их длительности. Это происходи- ло до тех пор, пока не считана по-

следняя ветвь из списка выходящих из начального узла ветвей. При этом по

адресу, который определяется номером последней вькодящей ветви, из узла 75 памяти блока 2 формирования тополо- гии считывается код X, который записывается в регистр 79. Выход последнего подключен к дешифратору 85 состояния X, поэтому в результате сравнения кодов на выходе дешифратора 85 формируется сигнал, означающий конец списка выходящих из узла ветвей. Сигнал с выхода дешифратора 85 поступает на нулевой вход триггера 84, устанавливая его в нулевое состояние. Кроме этого, сигнал поиска прерывания с выхода дешифратора 85 через элемент ИЛИ 96 поступает на выходной полюс 51

С полюса 5 сигнал поиска прерывания поступает на единичный вход триггера 12 прерьгоания блока 1 управления, устанавливая его в единичное состояние, и на нулевой вход триггера 14 фиксации опоздания операции, устанавливая его в нулевое состояние. Кроме этого, сигнал поиска прерывания с полюса 51 через полюс 52 поступает в блок 3 моделей ветвей. С полюса 52 сигнал поиска прерывания через элемент ИЛИ 119 узла 105 поиска моделей ветвей и полюс (1,1) поступает на вход элементов И I09(l) и llO(l) первой модели ветви 104(1). Так как в рассматриваемый момент подготовлены к моделированию все ветви, выходящие из начального узла сети, и моделей ветвей, закончивших процесс ноделиро- вания нет, то триггеры 108 всех моделей ветвей находятся в нулевом состоянии. Поэтому на выходе элементов И МО всех моделей ветвей присутствует потенциал низкого уровня, что дает потенциал низкого уровня на выходе элемента ИЛИ.120 узла 105 поиска моделей ветвей. Этот потенциал через полюс 61 поступает в блок 1 управления.

Ё блоке 1 управления потенциал низкого уровня, что означает отсутствие . моделей ветвей, окончивших моделирование, с полюса 61 через элемент ИЛИ 35 поступает на нулевой вход триггера 12 подтверждая его единичное состояние. Потенциал высокого уровня с единично- го выхода триггера 12 поступает на- первый вход элемента И 23, разрешая прохождение импульсов измерительной серии через элемент И 23 и элемент ИЛИ 34 на вход узла 11 измерения длин нейщего пути и на входной полюс 58

5

0

Q

5

0 , 5

30

5

40

блока 3 моделей ветвей. С входного полюса 58 импульсы измерительной серии поступают на вход элементов И 114 всех моделей ветвей 104 блока 3 моделей ветвей. У тех моделей ветвей, у которых триггер 107 находится в единичном состоянии, на второй вход элементов И 114 поступает разрешающий потенциал с единичного выхода триггера 107 и импульсы измерительной серии с выхода элементов И 114 поступают на счетный вход формирователей I06 временных интервалов. Так продолжается до тех пор, пока хотя бы один из формирователей 106 временного интервала не выдаст сигнал об окончании процесса временного моделирования длительности ветви, или пока из блока связи с объектом контроля 5 не поступит сигнал о фактическом окончании как,ой-либо операции.

Рассмотрим ситуацию, когда в процессе моделирования длительности ветвей, выходящих из начального узла сети, приходит сигнал о фактическом окончании какой-либо операции. При этом на входном полюсе 63 блока I управления появляется сигнал фактического выполнения операции, а на входном полюсе 64 формируется код номера этой операции. Сигнал фактического окончания операции с-полюса 63 поступает на единичный вход триггера 13 внешнего прерывания, устанавливая его в единичное состояние. Кроме этого, сигнал с полюса 63 поступает на вход записи узла памяти меток фактического свершения операции. Код номера свершившейся операции с полюса 64 поступает на первый вход блока элементов И 20. Так как в рассматриваемый момент триггер I2 прерывания находится в единичном состоянии, то на втором входе блока элементов И 20 присутствует разрешающий потенциал с единичного выхода триггера 12. Поэтому на выходе элемента И 20 формируется код номера свершившейся операции, который через блок элементов ИЛИ 29 поступана адресный вход узла 10 памяти задержек операций, а через элемент ИЛИ 3 на адресный вход узла 9 памяти. Происходит запись метки фактического свершения операций в узле 9 памяти по адресу номера операции, который поступает с полюса 64.

Одновременно потенциал с единичного выхода триггера 13 поступает на

первый вход элемента И 17, на второй вход которого поступает разрешающий потенциал с единичного выхода триггера 12. На третий вход элемента И 17 поступают сигналы серии ГИ2, Сигнал, сформированный на выходе элемента И 17, поступает на вход элемента 36 задержки и через элемент ИЛИ 32 на вход считывания узла 8 памяти, с полюса 64 через блоки элементов И 20, ИЛИ 29, ИЛИ 31 в это время поступает код номера фактически свершившейся операции. Осуществляется проверка теоретического свершения ветви путем считывания метки свершения с узла 8 памяти. Так как в рассматриваемый момент (моделируются длительности ветвей, выходящих из начального узла сети) ни одна из ветвей сети не имеет теоретического свершения, то на выходе узла 8 памяти присутствует потенциал низкого уровня. Этот потенциал подается на вход элемента И 18, запрещая прохождение сигнала с выхода элемента 36 задержки через- элемент И 18, и через элемент НЕ 45 на вход элемента И 19, разрешая прохождение сигнала через этот элемент. Сигнал с выхода элемента И 19 через элемент ИЛИ 26 поступает на нулевой вход триггера 13, устанавливая его в нулевое состояние. Кроме этого, -сигнал с выхода элемента ИЛИ 26 поступает на выходной полюс 62, сигнализируя об окончании обработки внешнего прерывания. При обработке внешнего прерывания осуществляется запись метки фактического свершения операции в узел 9 памяти и проверка метки теоретического свер- шения ветви в узле 8 памяти. Если метка теоретического свершения- ветви равна О, процесс обработки внешнего прерывания оканчивается и выдается сигнал об окончании обработки.

При временном моделировании длительности ветвей, выходящих из начального узла .сети, сигналы измерительной серии поступают на входы формирователей 106 временных интервалов тех моделей ветвей 104 блока 3 моделей ветвей, триггеры 107 которых находятся в единичном состоянии. Так продолжается до тех пор, пока хотя бы один из формирователей 106 временного интервала не выдаст сигнал об окончании процесса временного моделирования длительности ветви. Сигналы с выхода формирователей 106(1), 1 06(2),...,

5

0

(

106(М) временных интервалов поступают на единичные йходы триггеров 108(1), 108(2),..., 108(М), устанавливая их в единичное состояние. Одновременно сигналы с выходов формирователей 106(1), 106(2),...,106(М) временных интервалов через полюса (1,2),(2,2),...,(М,2) поступают на входы элемента ИЛИ 119 Q узла 105 поиска моделей ветвей.

С выхода элемента ИЛИ 119 сигнал прерывания через полюс (1,1) поступает на входы элементов И 109(1) и 110(1) первой модели ветви 04(l). Если триггер 108(1) первой модели ветви 104(1) находится в единичном состоянии, сигнал прерывания с выхода элемента И 110(1) через полюс (1,4) и элемент ИЛИ 120 поступает на входной полюс 62 блока 1 управления. Кроме Зтого, сигнал с выхода элемента llO(l) первой модели ветви 104(1) поступает на ну-. левой вход триггера 107(1), устанавливая его в нулевое состояние, а 5 также через элемент ИЛИ 115(1) и полюс (1,3) на вход шифратора 118 адреса узла 105 поиска моделей ветвей, а также через элемент 11б(1 ) задержки на нулевой вход триггера 108 (Г), 0 устанавливая его в нулевое состояние. По сигналу, который поступает на вход шифратора 118 адреса, формируется код номера данной модели ветви, Этот код с выхода шифратора 118 адреса через полюс 60 поступает в блок 1 управления.

;( Q

В блоке 1 управления код номера модели ветви с полюса 60 поступает на адресный вход узла 7 памяти номеров моделируемых ветвей. На вход считьша- ния узла 7 памяти поступает сигнал прерывания с входного полюса 61. Происходит считывание номера ветви сети по адресу номера модели ветви из узла 7 памяти. Этот код с выхода узла 7 памяти поступает через блок элементов ИЛИ 29 на адресный вход узла 10 памяти величины задержек операций и на выходной полюс 54, через блоки элементов ИЛИ 29 и элементов ИЛИ 31 на адресный вход узла памяти меток фактического окончания операции 9 и на адресный вход узла 8 памяти меток свершения ветвей. Сигнал прерывания с полюса 61, кроме входа считывания узла 7 памяти, поступает также на вход элемента 42 задержки и через элемент ИЛИ 35 на нулевой вход тригге5

19

1509926

pa 12, сбрасывая его в нулевое состояние .

По истечении времени, достаточного для считывания информации с узла 7 памяти, на выходе элемента 42 задержки формируется сигнал, который поступает на вход записи узла 8 памяти. Происходит запись метки свершения ветви в узел 8 памяти по адресу номера этой ветви. Кроме этого, сигнал прерывания с выхода элемента задержки 42 через элемент ИЛИ 27 поступает на вход считывания узла 9 памяти меток

фактического окончания операций. Про- ная метка, триггер 14 фиксации опоздаисходит считывание метки фактического свершения , и, если считана .нулевая метка (нет подтверждения фактического выполнения операции, операция задерживается), на выходе узла 9 . памяти формируется сигнал низкого уровня, который через элемент НЕ 46 устанавливает триггер 14 фиксации опоздания операции в единичное состояние. Кроме этого, сигнал с выхода элемента 42. задержки поступает на установочный вход сумматора 15 опоздания операций. На один из информационных входов- сумматора 15 поступает код

ния операций в единичное состояние не установлен, на входе элемента И 22 имеется запрещающий потенциал и запись в узел 10 памяти не происходит.

20 Кроме этого, сигнал прерывания с выхода элемента 42 задержки поступает на вход элемента 43 задержки. По истечении времени, достаточного для выполнения описанных операций, на вы25 ходе элемента 43 задержки формирует- ся сигнал начала анализа, который через элемент ИЛИ 33 поступает на выходной полюс 56. На выходной полюс 54 поступает код номера свершившейся ветиз узла 1 1 измерения длиннейшего пути.о ви с выхода элемента ИЛИ 29.

Сигнал на установочном входе сумматора устанавливает функцию сумматора 15 такой, когда на выходе сумматора формируется код, поступающий на сумматор из узла 1 1 измерения) длиннейшего пути. В этом случае сумма- тор 15 выполняет функцию передачи информации с одного входа на выход.Этот код поступает на информационный вход регистра 16 накопителя-сумматора. На установочный вход последнего поступает сигнал с установочного входа сумматора 15 через элемент ИЛИ 30 и элемент 41 задержки. Осуществляется запись кода с выхода сумматора 15 в .регистр-накопитель 16, с выхода которо го код поступает на информационный вход узла 10 памяти величины задержек операций. Кроме этого, сигнал прерывания с выхода элемента 42 задержки

35

40

- 45

При анализе прерьшания от теоретического свершения ветви в блоке 1 управления осуществляются запись метки свершения по адресу номера данной ветви в узел 8 .памяти, считывание метки фактического свершения из узла 9 Памяти, установка в единичное состояние триггера 14 опоздания в случае считывания нулевой метки фактического свершения, запись кода узла I1 измерения длиннейшего пути в узел 10 памяти величины опоздания операции по адресу теоретически свершившейся ветви. узла 9 памяти считана единичная метка, триггер 14 опоздания в единичное состояние не устанавливается и запись в узел 10 памяти не производится.

В блоке 2 формирования топологии код номера теоретически свершившейся

поступает на вход элемента 38 задерж- 50 ветви с полюра 54 поступает на адрески. По истечении времени, достаточного для считывания информации из узла 9 памяти и установки триггера 14 фиксации опоздания операции, а также времени,, достаточного для получения ко- 55 да на выходе сумматора 15 и установки регистра 16, на выходе элемента задершси 38 сформируется сигнал, коньй вход узла 74 памяти номеров конеч ных узлов ветвей сети. На вход считывания узла 74 памяти поступает сигнал начала анализа с входного полюса 56. Кроме этого, сигнал начала анализа с входного полюса 56 поступает на единичный вход триггера 83, устана,вливая его в единичное состояние, и на вход

20

торый поступает на вход элемента И 22. На второй вход этого элемента поступает разрешающий потенциал с триггера 14.

На выходе элемента И 22 формируется сигнал, который через элемент ИЛИ 28 поступает на вход записи узла 10 памяти. Осуществляется запись кода с выхода регистра 16 (код узла 11 измерения длиннейшего пути) в узел 10 памяти по адресу номера ветви, которая не имеет фактического окончания, из узла 9 памяти считывается единичния операций в единичное состояние не установлен, на входе элемента И 22 имеется запрещающий потенциал и запись в узел 10 памяти не происходит.

Кроме этого, сигнал прерывания с выхода элемента 42 задержки поступает на вход элемента 43 задержки. По истечении времени, достаточного для выполнения описанных операций, на выходе элемента 43 задержки формирует- ся сигнал начала анализа, который через элемент ИЛИ 33 поступает на выходной полюс 56. На выходной полюс 54 поступает код номера свершившейся вет

35

40

45

При анализе прерьшания от теоретического свершения ветви в блоке 1 управления осуществляются запись метки свершения по адресу номера данной ветви в узел 8 .памяти, считывание метки фактического свершения из узла 9 Памяти, установка в единичное состояние триггера 14 опоздания в случае считывания нулевой метки фактического свершения, запись кода узла I1 измерения длиннейшего пути в узел 10 памяти величины опоздания операции по адресу теоретически свершившейся ветви. узла 9 памяти считана единичная метка, триггер 14 опоздания в единичное состояние не устанавливается и запись в узел 10 памяти не производится.

В блоке 2 формирования топологии код номера теоретически свершившейся

50 ветви с полюра 54 поступает на адресньй вход узла 74 памяти номеров конечных узлов ветвей сети. На вход считывания узла 74 памяти поступает сигнал начала анализа с входного полюса 56. Кроме этого, сигнал начала анализа с входного полюса 56 поступает на единичный вход триггера 83, устана,вливая его в единичное состояние, и на вход

элемента 102 задержки. Единичное состояние триггера 83 разрешает прохождение импульсов серии ГИ1 и серии ГИ2 через элементы И 88 и 89 соответственно. По сигналу начала анализа, который поступает на вход считывания узла 74 памяти, происходит считывание ячейки памяти, где записан номер конечного узла свершившейся ветви. Код считанного номера узла с выхода узла 74 памяти поступает на адресньгй вход узла 78 памяти первой входящей ветви и на информационный вход регистра 81 конечного узла.

Через время задержки, достаточное для считывания информации из узла 74 памяти, сигнал начала анализа с выхода элемента 102 задержки поступает на управляющий вход регистра 81 конечного узла и на вход считывания узла 78 памяти. По этому сигналу происходит запись кода номера конечного узций. На вход считывания узла 9 памя ти с полюса 50 через элемент ИЛИ 27 поступает сигнал проверки свершения ветви. Если из узла 9 памяти считыва ется нулевая метка свершения, сигнал низкого уровня с выхода узла 9 памят через элемент НЕ 46 устанавливает триггер 14 фиксации опоздания операции в единичное состояние. В противном случае на выходе узла 9 памяти присутствует потенциал высокого уров ня и триггер 14 в единичное состояни не устанавливается. Кроме этого, сиг нал с выхода узлэ 9 памяти поступает на вход элемента И 21, на другой вхо которого поступает сигнал метки теоретического свершения ветви с выхода узла 8 памяти. Если с обоих узлов 8 и 9 памяти считана единичная метка, что означает как теоретическое, так фактическое свершение данной ветви, на выходе элемента И 21 формируется сигнал высокого уровня, который чере

ла ветви в регистр 81 и считывание . первой ветви, входящей в этот узел, 25 полюс 55 поступает в блок 2 формиро- из узла 78 памяти. Код номера первой вания топологии. В противном случае входящей ветви с выхода узла 78 памяти через элемент ИЛИ 98 поступает на информационный вход регистра 80 входящей ветви и записывается в него по ,,, первому импульсу серии ГИ1, поступающему на управляющий вход регистра с выхода элемента И 88. С выхода регистра 80 код номера первой входящей ветви поступает на адресный вход узла 76

на выходе элемента И 21 формируется сигнал низкого уровня.

В блоке 2 формирования топологии сигнал считанных меток свершения ветви с полюса 55 поступает на вход элемента И 92 и через элемент НЕ 103 и элемент ИЛИ 99 на нулевой вход триг гера 83. Если считана хотя бы одна нулевая метка, что означает теоретипамяти номеров входящих ветвей. Кроме ческое или фактическое несвершение

этого, код номера первой входящей ветви через полюс 49 поступает в блок .управления. Через полюс 50 в блок 1 управления по первому импульсу .ГИ2, поступающему с выхода элемента И 89 блока 2 формирования топологии, поступает сигнал проверки свершения ветви.

В блоке 1 управления код номера первой входящей ветви с входного по- люса 49 через блок элементов ИЛИ 31 поступает на -адресный вход узла 8 па мяти меток свершения ветвей. На вход считывания узла 8 памяти поступает сигнал проверки свершения ветви с входного полюса 50 через элемент ИЛИ 32. Сигнал считанной метки с выхода узла 8 памяти поступает на вход элемента И 21. Кроме эфого, код номера первой входящей ветви с входного полюса 49 через элемент ИЛИ 3 поступает на адресный вход узла 9 памяти меток фактического окончания опера

ций. На вход считывания узла 9 памяти с полюса 50 через элемент ИЛИ 27 поступает сигнал проверки свершения ветви. Если из узла 9 памяти считывается нулевая метка свершения, сигнал низкого уровня с выхода узла 9 памяти через элемент НЕ 46 устанавливает триггер 14 фиксации опоздания операции в единичное состояние. В противном случае на выходе узла 9 памяти присутствует потенциал высокого уровня и триггер 14 в единичное состояние не устанавливается. Кроме этого, сигнал с выхода узлэ 9 памяти поступает на вход элемента И 21, на другой вход которого поступает сигнал метки теоретического свершения ветви с выхода узла 8 памяти. Если с обоих узлов 8 и 9 памяти считана единичная метка, что означает как теоретическое, так и фактическое свершение данной ветви, на выходе элемента И 21 формируется сигнал высокого уровня, который через

полюс 55 поступает в блок 2 формиро- вания топологии. В противном случае

полюс 55 поступает в блок 2 формиро- вания топологии. В противном случае

на выходе элемента И 21 формируется сигнал низкого уровня.

В блоке 2 формирования топологии сигнал считанных меток свершения ветви с полюса 55 поступает на вход элемента И 92 и через элемент НЕ 103 и элемент ИЛИ 99 на нулевой вход триггера 83. Если считана хотя бы одна нулевая метка, что означает теоретическое или фактическое несвершение

0

5

ветви с данным номером, то этот сигнал устанавливает триггер 83 в нулевое состояние. Кроме этого, сигнал с выхода элемента НЕ 103 поступает через элемент ИЛИ 96 на полюс 51 поиска прерывания. Наличие нулевого сигнала меток свершения ветви означает, что хотя бы одна из ветвей, входящих в рассматриваемый узел, не свершилась, а . следовательно, в данном узле не сформировалась функция и для всех входящих в него ветвей. В зтом случае сигнал с полюса 51 поступает на единичный вход триггера 12 прерывания блока 1 управления, устанавливая его в единичное состояние, на нулевой вход триггера 14 фиксации опоздания, устанавливая его в нулевое состояние, а также на входной полюс 52 блока 3 моделей ветвей. В по.следнем сигнал поиска прерывания с полюса 52 посту- , пает на вход элемента ИЛИ 119 узла 105 поиска моделей ветвей.

23

С выхода элемента ШШ I 19 сигнал поступает на входы элементов И 109(1) и 110(1) первой модели ветви 104(1). Если триггер 108(1) прерывания первой модели ветви 104(1) находится в нулевом состоянии, то на выходе элемента И 109(0 формируется сигнал высокого уровня, который через полюс (2,1)

150992624

узла 76 памяти входящих ветвей. На адресный вход узла 76 памяти в это время поступает код номера первой входящей ветви с выхода регистра 80. По адресу первой входящей ветви из узла 76 памяти считан код номера второй входящей в рассматриваемы ; узел ветви. Считанный код через элепоступает на в ходы элементов И 109(2) Q мент ИЛИ 98 поступает на информации 10( 2) второй модели ветви 104(2). Если, триггер 108(2) прерывания второй модели ветви 104(2) находится в нулевом состоянии, сигнал высокого уровня с выхода элемента 109(2) через полюс (3,1) поступает на входы элементов И 109(3) и 110(3) третьей модели ветви и т.д. Если в блоке 3 моделей ветвей имеется еще модель ветви, которая окончила процесс моделирования длительности, то триггер 108 такой модели ветви находится в единичном состоянии, и тогда сигнал с выхода элемента И -1 10 такой модели ветви через элемент ИЛИ 1 5 вновь поступает на вход шифратора 118 адреса для формирования кода номера данной модели ветви. Кроме этого, сигнал с выхода элемента И 110 устаонный вход регистра 80 и записывается в него с приходом второго импульса ГИ1 с выхода элемента И 88. Далее осуществляется считывание метки ретического свершения ветви из узла 8 памяти блока управления 1 и метки фактического свершения ветви из узла 9 памяти и переход к следующей ветЁи из списка входящих в .рассматри20 ваемый узел ветвей.

Процесс анализа входящих в рассмат риваемый узел ветвей-продолжается до тех пор, пока для какой-либо ветви не считана нулевая метка теоретичес25 кого или фактического свершения, или пока не опрошены все ветви, входящие в рассматриваемый узел. Последнее соответствует выполнению функции конъюнкции относительно входящих ветвей

35

40

навливает в нулевое состояние тригге- Q рассматриваемого узла.- В этом случае

по адресу номера последней ветви в списке из узла 76 памяти блока 2 фор-- мирования топологии-считан код X, определяющий конец списка. Код X записывается в регистр 80 входящей ветви и с него поступает на вход дешифратора 86 состояния X, который путем сравнения кодов вырабатывает сигнал конца списка. Полученный сигнал с выхода дешифратора 86 состояния X Проходит через элементы РШИ 99 и 100 и устанавливает триггеры 83 и 84 соответственно, в нулевое и единичное состояние.

Кроме этого, сигнал с выхода дешифратора 86 поступает на вход элемента И 93, второй вход которого связан с выходом схемы 87 сравнения кодов. Последняя сравнивает коды, хранящиеся в регистре 82 конечного узла сети и в регистре 81 конечного узла ветви..Регистр 82 хранит код конечного узла сети, а регистр 81 - код рассматриваемого узда сети, сформировавшего функцию конъюнкции в данный момент времени. Если значения этих кодов совпадают (сформирована логическая функция конъюнкции для ко,- нечного узла сети), то схема 87 сравры 107 и 108, а также через элемент ИЛИ 120 выдает сигнал прерывания в блок 1. управления,. Последний, получив номер модели, ветви и сигнал прерывания, повторяет все описанные операции, связанные с анализом свершения ветви. Если в блоке 3 ветвей не имеется моделей ветвей, у которых триггер 108 находится в единичном состоянии, то процесс анализа заканчивается, триггер 12 остается в единичном состоянии и импульсы измерительной серии поступают через элемент Е 23 и элемент РШИ 34 блока 1 управления в узел 11 измерения длиннейшего пути и в блок 3 моделей ветвей.

Если при ашализе первой входящей в рассматриваемы узел ветви из узлов памяти меток свершения ветвей блока I управления считаны единичные метки, т.е.процесс формирования длитель-, ности данной ветви закончился и есть фактическое свершение данной ветви, то на входном полюсе 55 блока 2 формирования топологии формируется сигнал высокого уровня, который дает разрешение на прохождение импульсов серии ГИ2 с выхода элемента И 89 через элемент И 92 на вход считывания

45

50

55

мент ИЛИ 98 поступает на информационный вход регистра 80 и записывается в него с приходом второго импульса ГИ1 с выхода элемента И 88. Далее осуществляется считывание метки теоретического свершения ветви из узла 8 памяти блока управления 1 и метки фактического свершения ветви из узла 9 памяти и переход к следующей ветЁи из списка входящих в .рассматриваемый узел ветвей.

Процесс анализа входящих в рассматриваемый узел ветвей-продолжается до тех пор, пока для какой-либо ветви не считана нулевая метка теоретического или фактического свершения, или пока не опрошены все ветви, входящие в рассматриваемый узел. Последнее соответствует выполнению функции конъюнкции относительно входящих ветвей

нения кодов выдает разрешение на прохождение сигнала конца списка с входа дешифратора 86 через элемент И на выходной полюс 53 блока 2 формирования топологии, что.соответствует окончанию моделирования заданной сети. В блоке 1 управления сигнал разрешения индикации расчета с полюса 5 поступает на вход элемента И 25. На второй вход элемента И 25 поступает код величины длиннейшего пути сети с узла 11 измерения длиннейшего пути, С выхода элемента И 25 код длиннейшего пути сети поступает на выходной полюс 72.

В случае, если конечный узел сети не сформирован, сигнал с выхода дешифратора 86 блока 2 формирования топологии через элемент ИЛИ 94 поступает на вход считывания узла 77 памяти первой выходящей ветви. На адресный вход узла 77 памяти в этот момент поступает код номера сформированного узла сети. Происходит считывание кода номера первой ветви, выходящей из сформированного узла сети. Этот код через элемент ИЛИ .95 поступает на информационный вход регистра 79 и записывается в него по первому импульсу ГИ1, поступающему на управляющий вход регистра с выхода элемента И 90. Записанный код номера первой вьгходящей ветви с выхода регистра 79 поступает на адресный вход узла 75 памяти номеров выходящих ветвей и через выходной полюс 47 в блок 1 управления. Далее импульс ГИ2 с выхода элемента И 9 блока 2. формирования топологии поступает на вход считывания узла 75 памяти. Происходит считывание второй ветви, выходящей из сформированного узла. Кроме этого, импульс ГИ2 с выхода элемента И 91 через выходной полюс 48 поступает в блок 1 управления .

В блоке 1 управления сигнал поиска свободной модели ветви с полюса 48 поступает на вход считывания узла 6 памяти длительностей ветвей. На адресный вход узла 6 памяти в этот мо- мент поступает код номера первой выходящей из узла ветви с полюса 49. Осуществляется считывание кода длительности этой ветви, который через полюс 59 поступает в блок 3 моделей ветвей. Кроме этого, сигнап поиска свободной модели ветви с входного по- лю.са 48 через полюс 57 поступает в

10

15

20

5 g

0

5

0

5

блок 3 моделей ветвей. По этому сигналу осуществляется поиск свободной модели ветви, формирование ее кода и запись длительности ветви в формирователь временного интервала этой модели ветви. Код свободной модели ветви через полюс 60 поступает в блок управления. Осуществляется запись номера подготавливаемой ветви в узел 7 памяти по адресу номера выбранной свободной модели ветви. На этом заканчивается подготовка к временному . моделированию первой ветви, выходящей из сфо рмированного узла сети. Аналогичным образом осуществляется подготовка остальных ветвей, выходящих из данного узла.

После подготовки к процессу моделирования всех ветвей, выходящих из свершившегося узла, на выходе дешифратора 85 блока 2 формирования топологии формируется сигнал поиска прерывания, которьш через элемент 1-1ЛИ 96 и выходной полюс 51 поступает в блок 1 управления. В блоке 1 управления сигнал поиска прерывания поступает на единичный вход триггера 12 прерывания, устанавливая его в единичное состояние, и на нулевой вход триггера 14 фиксации внешнего прерывания, устанавливая его в нулевое состояние. Кроме этого, сигнал поиска прерывания с полюса 5 через полюс 52 поступает в блок 3 моделей вевтвей. По этому сигналу осуществляется поиск очередной модели ветви, окончившей процесс моделирования. Если такая модель обнаруживается, то сигнал прерывания с выхода элемента ИЛИ 120 узла 105 поиска моделей ветвей через полюс 61 поступает в блок 1 управления. Производится обработка очередного прерывания описанным образом. Это происходит до тех пор, пока не обработаются прерывания от всех моделей ветвей, окончивших в настоящий момент процесс моделирования.

После этого сигнал поиска прерывания с выхода дешифратора 85 блока 2 формирования топологии через выходной полюс 51 поступает в блок 1 управления и устанавливает триггер 12 прерывания в единичное состояние. Кроме этого, сигнал поиска прерывания с полюса 51 через полюс 52 поступает в бло.к 3 моделей ветвей. Так как в рассматриваемый момент в блоке 3 моделей ветвей нет необработанных моделей ветвей, которые окончили моделирование, то сигнал низкого уровня с выхода элемента ИЛИ 120 узла 105 поиска моделей ветвей через полюс 61 поступает на нулевой вход триггера 12 прерывания блока 1 управления, под- тверлсдая его единичное состояние. Потенциал высокого уровня с единичного выхода триггера 12 поступает на вход элемента И 23, разрешая прохождение HMnyjjbcoB измерительной серий через элементы И 23 и ИЛИ 34 на вход узла 1 1 измерения длиннейш.его пути и на вход 58 блока 3 моделей ветвей. На .чинается этап временного моделирова- :ния длительности.

Рассмотрим ситуацию, когда во время обработки сигнала прерывания от окончившей моделирования модели нет- ви или во время подготовки к моделированию ветвей поступает сигнал об фактическом окончании какой-либо операции. При этом на входном полюсе 63

блока J управления формируется сигнал 25 сматриваемый момент нет моделей вет- фактического окончания операции, а вей, которые закончили процесс моде- на входном полюсе 64 присутствует код лирования, сигнал прерывания не выра- номера окончившейся операции. Сигнал с полюса 63 поступает на единичный

30

вход триггера 13 внешнего прерывания, устанавливая его в единичное состояние. Сигнал с единичного выхода триггера 13 поступает на первый вход эле- мента И 17. Так как в рассматриваемый момент триггер 12 прерьгоания находится в нулевом состоянии, потенциал низкого уровня с единичного выхода поступает на второй вход элемента И 17, запрещая прохолсдение сигнала с единичного выхода триггера 13 через элемент И 17. С входного полю- . са 64 код номера фактически окончившейся операции поступает на первый вход блока элементов И 20, на второй вход которого также поступает запрещающий потенциал с единичного выхода триггера 12. В таком состоянии эле- 1 менты И 17 и блок 20 находятся до тех пор, -пока на входном полюсе 51 не сформируется сигнал поиска преры- вания.

Сигнал поиска прерывания вырабатывается в блоке 2 формирования топологии . по импульсу ГИ1 , если при анализе свершения ветвей, входящих в рассматриваемый узел, из узла-8 или 9 памяти меток свершения блока 1 управления по какому-либо адресу считана нулевая метка, а также после за35

40

45

50

55

батывается и триггер 12 блока управления остается в единичном состоянии. Потенциал высокого уровня с единичного вькода триггера 12 поступает на второй, вход элемента И 17, на третий вход которого поступают импульсы серии ГИ2 с входного полюса 66. На выходе элемента И 17 формируется сигнал высокого уровня, которьй поступает на элеме:нт 36 задержки и через элемент ИЛИ 32 на вход считывания узла 8 памяти меток свершения. Кроме этого, потенциал высокого уровня с единичного выхода триггера 12 поступает на вход блока элементов И 20, на второй вход которого поступает код фактически свершившейся операции с входного полюса 64.

На-выходе блока элементов И 20 формируется код номера операции, который через блок .элементов ИЛИ 29 поступает на адресный вход узла 10 памяти, и на выходной полюс 54 а далее через элемент ИЛИ 31 на адресный вход узла 8 памяти меток свершения ветвей и на адрес.ный вход узла 9 памяти меток фактического окончания операций. На вход записи узла 9 памяти поступает сигнал фактического окончания операции с полюса 63. Осуществляется запись метки фактического окончания операции в узел 9 памяти по адресу

грузки всех ветвей, выходящих из свершившегося узла. С входного полюса 51 блока 1 управления сигнал поиска прерывания поступает на единичный вход триггера 12, устанавливая его в единичное состояние. Кроме этого, сигнал поиска прерывания через полюс 52 поступает в блок 3 моделей ветвей. Если в блоке моделей ветвей в рассматриваемый момент есть модели ветвей, которые закончили процесс моделирования, на выходном полюсе 61 блока 3 моделей ветвей формируется сигнал прерывания. Этот сигнал с входного полюса 61 блока I управления через элемент ШШ 35 поступает на нулевой вход триггера 12, устанавливая его в нулевое состояние. Начинается этап обработки нового прерывания. Состояние схемы в части обработки сигнала о фактическом окончании операции остается неизменным.

Если в блоке -моделей ветвей в рас5 сматриваемый момент нет моделей вет- вей, которые закончили процесс моде- лирования, сигнал прерывания не выра-

0

5

0

5

0

5

батывается и триггер 12 блока управления остается в единичном состоянии. Потенциал высокого уровня с единичного вькода триггера 12 поступает на второй, вход элемента И 17, на третий вход которого поступают импульсы серии ГИ2 с входного полюса 66. На выходе элемента И 17 формируется сигнал высокого уровня, которьй поступает на элеме:нт 36 задержки и через элемент ИЛИ 32 на вход считывания узла 8 памяти меток свершения. Кроме этого, потенциал высокого уровня с единичного выхода триггера 12 поступает на вход блока элементов И 20, на второй вход которого поступает код фактически свершившейся операции с входного полюса 64.

На-выходе блока элементов И 20 формируется код номера операции, который через блок .элементов ИЛИ 29 поступает на адресный вход узла 10 памяти, и на выходной полюс 54 а далее через элемент ИЛИ 31 на адресный вход узла 8 памяти меток свершения ветвей и на адрес.ный вход узла 9 памяти меток фактического окончания операций. На вход записи узла 9 памяти поступает сигнал фактического окончания операции с полюса 63. Осуществляется запись метки фактического окончания операции в узел 9 памяти по адресу

29

номера операции. Из узла 8 памяти считывается метка теоретического снер шения ветви с данным номером. Если из узла 8 памяти считана единичная метка, сигнал высокого уровня с выхода узла 8 памяти поступает на вход элемента И 18. На другой вход этого элемента поступает сигнал с выхода элемента 36 задержки. На выходе элемента И 1 8 формируется сигнал высокого уровня, который через элемент ШШ 33 поступает на входной полюс 56 блока 2 топологии. Последний, получив сигнал начала анализа с полюса 56 и код номера свершившейся операции с входного полюса 54, начинает этап анализа свершения всех ветвей входя- щих в узел, в который входит свершившаяся операция. Процесс анализа св.ершения ветви осуществляется аналогично описанному.

150

Кроме этого, сигнал с выхода элемента И 18 блока 1 управления посту- пает на вход считывания узла 0 памяти величины задержки операций и на вход элемента 39 задержки. Осуществляется считывание кода из узла 10 памяти (код времени теоретического свершения операции) по адресу номера фактически свершившейся операции. С выхода узла 10 памяти код поступает на первый информационный вход сумматора 15. На другой информационный вход сумматора 15 постоянно поступает код с узла 11 измерения длиннейшего пути. Через время, достаточное для считывания информации из узла 10 памяти, на выходе элемента 39 задержки формируется сигнал, который поступает на вход установки режима вычитания сумматора 15 и через элемент ИЛИ 30 на вход элемента 41 задержки. По этому сигналу на выходе сумматора устанавливается код разности (код величины задержки операции) между кодом узла измерения длиннейшего пути (код времени фактического окончания операции) и кодом, считанным из узла 0 памяти (код теоретического свершения операции). С выхода сумматора 15 код величины задержки операции поступает на информаьщонный вход регистра-накопителя 16. На установочный вход ре

гистра 16 поступает сигнал, сформиро ванный на выходе элемента 41 задержки. Происходит запись кода величины задержки операции в регистр 16.

5

р з 10

35

С выхода регистра 16 код задержки операции поступает на информационный вход узла 10 памяти. Через время, достаточное для считывания информации с узла 10 памяти, вычитания кодов на сумматоре 15 и записи кода разницы в регистр-накопитель 16, на входе записи узла 10 памяти появится сигнал, который сформировался на выходе элемента 37 задержки. Происходит запись кода величины задержки выполнения операции в узел 10 памяти по адресу этой операции. Кроме этого, сигнал с выхо- да элемента 37 задержки через элемент ИЛИ 26 поступает на нулевой вход Триггера 13 внешнего прерывания, устанавливая его в нулевое состояние, и на выходной полюс 62 сигнала ответа. На этом заканчивается процесс обработки сигнала от фактического окончания операции.

Если в процессе обработки сигнала от фактического свершения операция из узла 8 памяти меток свершения вет20

вей считана нулевая метка (фактическое свершение операции произошло рань-

40

.

юе, чем теоретическое), сигнал низкого уровня с выхода узла 8 памяти по- Q ступает на вход элемента И 18, запрещая прохождение сигнала с элемента 36 задержки. В этой ситуации код величины задержки операции не формируется и запись в узел 10 памяти не производится. Кроме этого, не формируется сигнал начала анализа на выходном полюсе 56, и блок 2 формирования топологии не производит анализ свершения ветвей, входящих в тот же узел, что и фактически свершившаяся операция. В этой ситуации нулевой сигнал метки свершения с выхода узла 8 памяти через элемент НЕ 45 поступает на вход элемента И 19, на второй вход которого поступает сиг- нал с элемента 36 задержки. С выхода элемента И 19 сигнал окончания обработки фактического свершения через элемент ИЛИ 26 поступает на нулевой вход триггера J3 внешнего прерывания, устанавливая его в нулевое состояние, и на выходной полюс 62 сигнала ответа. На этом заканчивается этап обработки прерывания от фактического окончания операции.

Рассмотрена ситуация, когда во время обработки прерывания от теоретического свершения ветви поступает сигнал фактического окончания какой45

55 либо операции. В этом случае обработка сигнала от фактического окончания операции происходит после обработки прерываний от всех моделей ветвей, в том числе после загрузки всех ветвей, исходящих из свершившихся узлов, осуществляется запись метки фактического окончания операции в узел 9 памяти блока 1 управления и считывание метки теоретического свершения данной операции из узла 8 памяти. Если из узла 8 памяти считана единичная метка, это означает, что фактическое выполнение данной операции задержано по сравнению с теоретическим свершением. В этом случае определяется величина задержки, которая записывается в узел 10 памяти. Вместе с этим осуществляется анализ свершения всех ветвей, входящих в тот же узел, что и данная операция. Если все ветви имеют метки фактического и теоретического свершения, осуществляется загрузка ветвей, исходящих из рассматриваемого узла. После этого продолжается временное моделирование ветвей, длительность которых занесена в модели ветвей блока 3 моделей ветвей. В противном случае загрузка ветвей, исходящих из рассматриваемого узла, не выполняется, а продолжается временное, моделирование ветвей. Если при обработке сигнала от фактического свершения операции из узла 8 памяти, считана нулевая метка теоретического свершения, это означает, что фактическое выполнение операции произошло раньше, чем теоретическое свершение. , В этом случае величина задержки выполнения: операции не определяется и .анализ свершения ветвей не производится, а продолжается временное моделирование ветвей, длительность которых загружена в модели ветвей.

Этап временного моделирования дли тельностей ветвей продолжается до тех пор, пока хотя бы один из формирователей 106 временного интервала блока 3 моделей ветвей не выдает сигнал об

управления формируется сигнал высоко го уровня, а на входном полюсе 64 ф мируется код свершившейся операции. Сигнал с входного полюса 63 поступа на вход записи узла 9 памяти меток фактического окончания операции, на адресный вход которого с входного по люса 64 через блоки элементов И 20,

.л ИЛИ 29, ИЛИ 31 поступает код номера свершившейся операции. Осуществляетс запись метки фактического свершения по адресу номера операции. Кроме это го, сигнал с входного полюса 63 ступает на единичный вход триггера внешнего прерывания, устанавливая ег в единичное состояние. Сигнал с единичного выхода триггера 13 поступает на первый вход элемента И 17, на вто

2Q рой вход которого в рассматриваемый момент поступает потенциал высокого уровня с единичного выхода триггера 12. На третий вход элемента И 17 поступают сигналы тактовой серии ГИ2

25 На выходе элемента И 17 формируется сигнал высокого уровня, который поступает на элемент 36 задержки и через элемент ИЛИ 32 на вход считывани узла 8 памяти меток свершения.

30

35

40

45

Ка адресный вход узла 8 памяти с входного полюса 64 через блоки элементов И 20, ИЛИ 29 и ИЛИ 31 поступа ет код номера фактически свершившейся операции. Осуществляется считывание из узла 8 памяти метки теоретиче кого свершения операции. Если считана единичная метка, сигнал высокого уровня с выхода узла 8 памяти поступает на вход элемента И i8. На друго вход этого элемента поступает.сигнал с выхода элемента 36 задержки. Ка вы ходе элемента И 18 формируется сигна высокого уровня, который через элемент ИЛИ 33 поступает на полюс 56 блока 2 формирования топологии. Последний, получив сигнал начала анализа с полюса 56 и код номера свершившейся операции с входного полюса 54, начинает этап анализа свершеокон 1анйи процесса временного Модели-50 ния всех ветвей, входящих в узел, в

рования длительности ветви или до прихода сигнала о фактическом свершении какой-либо операции из блока 5 связи с объектом контроля.

который Входит свершившаяся операци Кроме этого, сигнал с выхода элемен та И 18 блока 1 управления поступае на вход считывания узла iO памяти в

Если в процессе временного модели- 5 личины задержки операций и на вход

рования длительностей ветвей поступает сигнал о фактическом свершении операции, на входном полюсе 63 блока 1

управления формируется сигнал высокого уровня, а на входном полюсе 64 формируется код свершившейся операции. Сигнал с входного полюса 63 поступает на вход записи узла 9 памяти меток фактического окончания операции, на адресный вход которого с входного полюса 64 через блоки элементов И 20,

л ИЛИ 29, ИЛИ 31 поступает код номера свершившейся операции. Осуществляется запись метки фактического свершения по адресу номера операции. Кроме этого, сигнал с входного полюса 63 по5 ступает на единичный вход триггера 13 внешнего прерывания, устанавливая его в единичное состояние. Сигнал с единичного выхода триггера 13 поступает на первый вход элемента И 17, на втоQ рой вход которого в рассматриваемый момент поступает потенциал высокого уровня с единичного выхода триггера 12. На третий вход элемента И 17 поступают сигналы тактовой серии ГИ2.

5 На выходе элемента И 17 формируется сигнал высокого уровня, который поступает на элемент 36 задержки и через элемент ИЛИ 32 на вход считывания узла 8 памяти меток свершения.

30

35

40

45

Ка адресный вход узла 8 памяти с входного полюса 64 через блоки элементов И 20, ИЛИ 29 и ИЛИ 31 поступает код номера фактически свершившейся операции. Осуществляется считывание из узла 8 памяти метки теоретического свершения операции. Если считана единичная метка, сигнал высокого уровня с выхода узла 8 памяти поступает на вход элемента И i8. На другой вход этого элемента поступает.сигнал с выхода элемента 36 задержки. Ка выходе элемента И 18 формируется сигнал высокого уровня, который через элемент ИЛИ 33 поступает на полюс 56 блока 2 формирования топологии. Последний, получив сигнал начала анализа с полюса 56 и код номера свершившейся операции с входного полюса 54, начинает этап анализа сверше50 ния всех ветвей, входящих в узел, в

который Входит свершившаяся операция. Кроме этого, сигнал с выхода элемента И 18 блока 1 управления поступает на вход считывания узла iO памяти величины задержки операций и на вход

элемента 39 задержки. Осуществляется считывание кода времени теоретического свершения операции по адресу

33

номера фактически свершившейся оперции из узла 10 памяти.

С выхода узла 10 памяти код постпает на первый информационный вход сумматора 15, На другой информационный вход сумматора поступает код с узла 1i измерения длиннейшего пути. Через -время, достаточное для считывния информации из узла 10 памяти, на выходе элемента 39 задержки формируется сигнал, который поступает вход установки режима вычитания сумматора 15. По этому сигналу на выходе сумматора формируется код величины задержки выполнения операции. Эт код поступает на информационный вход регистра-накопителя 16 и записывается в него по сигналу, который поступает на установочный вход регистра с выхода элемента 41 задержки. С выхода регистра 16 код задержки выполнения операции поступает на информационный вход узла 10 памяти. На вход записи узла - 10 памяти-поступает сигнал с выхода элемента 37 задержки через элемент ИЛИ 28. Происходит запись кода величины задержки выполнения операции в узел 10 памяти по адресу этой операции.

Кроме этого, сигнал с выхода элемента 37 задержки через элемент ИЛИ поступает на нулевой вход триггера 13 внешнего прерывания, устанавливая его в нулевое состояние. Сигнал высокого уровня с выхода элемента И 1 8 через элемент ИЛИ 35 поступает на нулевой вход триггера 12, устанавливая его в нулевое состояние. Потенциал низкого уровня с выхода триггера 12 поступает на вход элемента И 23, запрещая прохождение сигналов измерительной серии через этот элемент на счетный вход узла 11 измерения длиннейшего пути и в блок 3 моделей ветвей. Если в рассматриваемой ситуации генератор импульсов 4 формирует сигнал измерительной серии (сигналы измерительнор серии после начального пуска вырабатываются с требуемой дискретностью генератором импульсов постоянно), указанный сигнал с входного полюса 66 блока 1 управления поступает на вход элемента И 24, на другой вход которого поступает разрешающий потенциал с нуле вого выхода триггера 12 прерывания.

На выходе элемента И 24 формируется сигнал, который поступает на вход

10

15

5

9926

0 5

. 34