1

Устройство для выделения одиночного импульса относится к импульсной технике и может быть использовано в различных устройствах преобразования, обработки и передачи информации.

Известно устройство тактовой синхронизации, содержащее два последовательно соединенныхВ-триггера, элемент И-НЕ, первый вход которого подключен к тактовому входу первого триггера, второй вход элемента И-НЕ соединен с единичным выходом ю первого триггера, нулевой выход первого триггера подключен к информационному входу второго триггера, тактовый вход которого соединен с выходом элемента И-НЕ, а единичный выход второго триггера подключен к третьему входу элемента И-НЕ 1. Устройство, имеющее повышенную помехоустойчивость, имеет существенный недостаток, заключающийся в том, что время выработки им синхронизирующего импульса может достигать значения 1,5 Т, где Т - 20 период тактовой частоты. Это ведет к значительному понижению быстродействия устройства, к тому же на его выходе выдается импульс только отрицательной полярности, что ограничивает применяемость схемы.

Из известных устройств наиболее близким по технической сущности является устройство для выделения одиночного импульса 2.

Это устройство содержитT S-триггер, Dтриггер, информационный вход которого соединен с источником управляющего сигнала с единичным входом1 5-триггера, единичный выход которого соединен с нулевым входомD-триггера, а нулевой вход - с выходом логического элемента И-НЕ, первый вход которого соединен с выходом инвертора, а второй - с единичным выходом Б-триггера, являющимся выходом устройстваСхема этого устройства проста и позволяет получить на выходе прямой и инверсный импульс, но если момент поступления входного управляющего сигнала совпадает с временем действия импульса тактовой частоты, то устройство формирует одиночный импульс на выходе только по второму импульсу тактовой частоты, что приводит к временным затратам, достигающим значения 1,5 Г и тем самым понижает быстродействие устройства.

Целью изобретения является увеличение быстродействия.

Поставленная цель достигается тем, что в устройство, содержащее RS-TpHrrep,B-триггер, информационный вход которого соединен с источником управляющего сигнала и единичным входомЯЗ-триггера, единичный выход которого соединен с нулевым входом D-триггера, а нулевой вход RS-триггера соединен с выходом элемента И-НЕ, первый вход которого соединен с выходом инвертора а второй вход - с единичным выходом В-триггера, тактовый вход которого соединен со входом инвертора, введены дополнительные D-триггер, RS-триггер, инвертор, три двухвходовых элемента И-НЕ и элемент задержки, нри этом тактовый вход первого D-триггера и вход первого инвертора соединены с выходом второго элемента И-НЕ, первый вход которого соединен с выходом третьего элемента И-НЕ, соединенного первым входом с источником тактовой частоты, входом второго инвертора, тактовым и информационным входами второго D-триггера, единичный выход которого соединен с вторым входом третьего элемента И-НЕ, а нулевой вход второго D-триггера соединен с выходом четвертого элемента И-НЕ и через элемент задержки с вторым входом второго элемента И-НЕ, первый вход четвертого элемента И-НЕ соединен с выходом второго инвертора и единичным входом второгоl Sтриггера, нулевой вход которого соединен с источником управляющего сигнала, а выход - с вторым входом четвертого элемента И-НЕ.

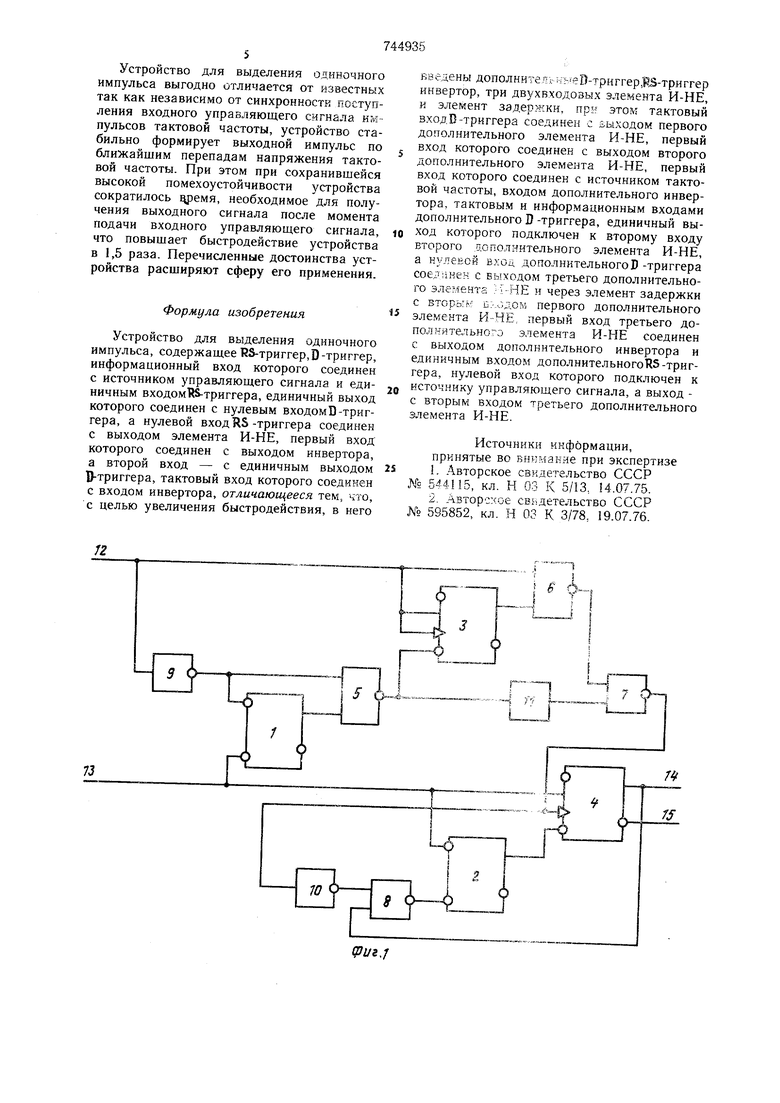

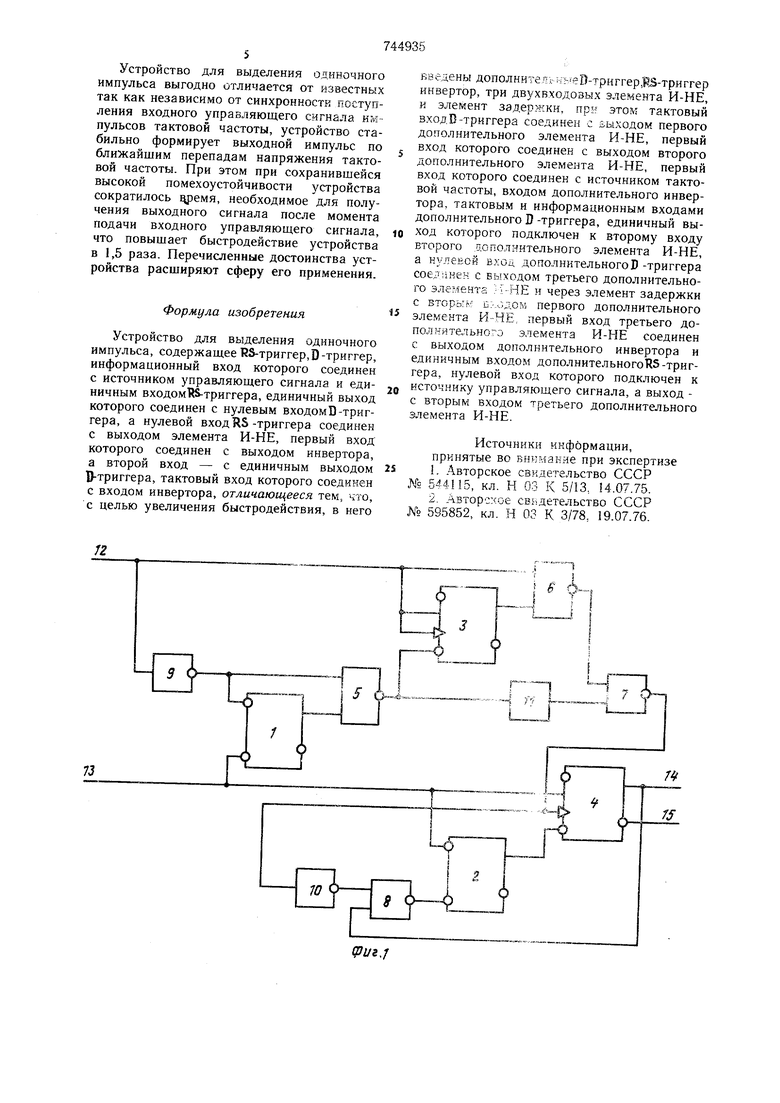

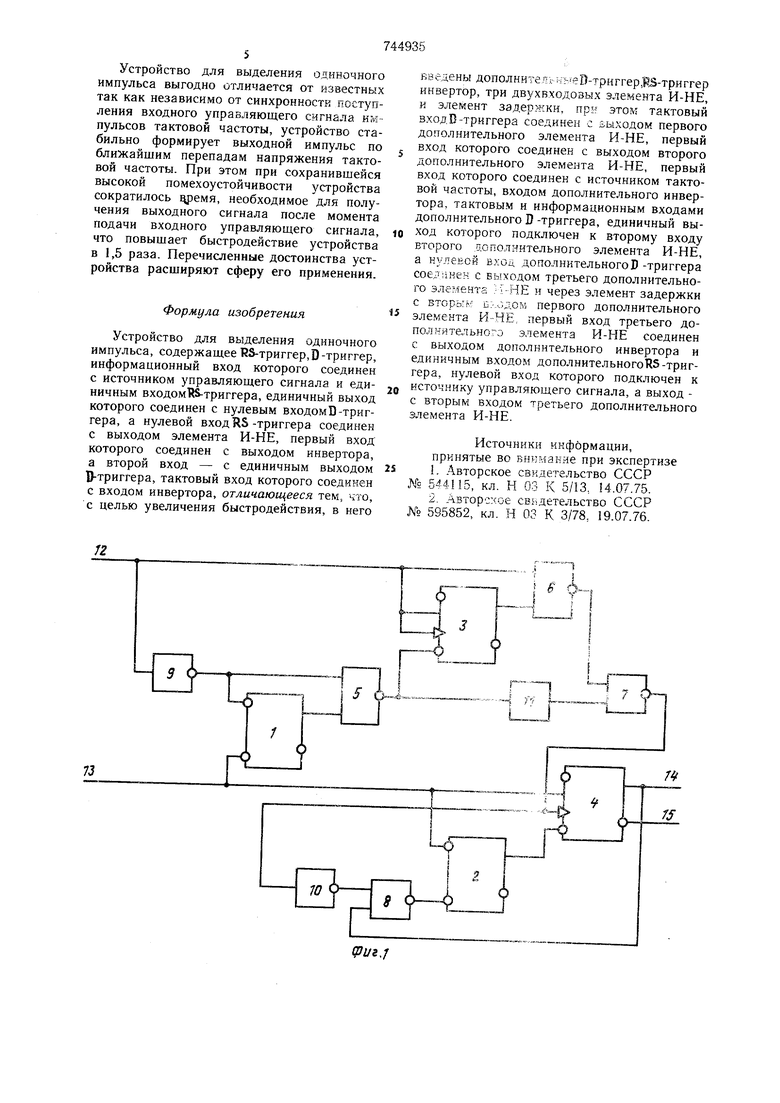

На фиг. 1 представлена схема устройства для выделения одиночного импульса; на фиг. 2 приведены диаграммы, характеризующие работу устройства.

Устройство содержитЯЗ-триггеры 1 и 2, D-триггеры 3 и 4, логические элементы И-НЕ 5, 6, 7, 8, инверторы 9 и 10, элемент задержки 11, вход 12 тактовой частоты, управляющий вход 13, пря.мой выход 14 и инверсный выход 15.

Принцип работы устройства заключается в следующем.

Устройство выделяет одиночный импульс синхронно с импу тьсом тактовой частоты или с паузой тактовой частоты в зависимости от момента поступления сигналов на входах 12 и 13. Если момент поступления входного управляющего сигнала на входе 13 не совпадает со временем действия импульса тактовой частоты на входе 12, то по переднему фронту первого тактового импульса триггер 3 установится в единичное состояние и стробирует прохождение тактового импульса через элементы И-НЕ 6 на вход элемента И-НЕ 7, выполняющего логическую функцию ИЛИ по низким уровням сигналов, и далее на тактовый вход В-триггера 4 и инвертор 10.

При этом до момента поступления входного управляющего сигнала триггер 1 установлен низким уровнем на его нулевом входе в нулевое состояние, что обеспечило наличие единичного логического сигнала на выходе

элемента И-НЕ 5, содействующего прохождению тактового импульса. Передний фронт этого импульса записывает в триггер 4 единичную информацию, подаваемую на его информационный вход входным управляющим сигналом, что соответствует появлению

® на выходе устройства одиночного импульса, задний фронт которого формируется по заднему фронту тактового импульса, устанавливающего через инвертор 10 и элемент И-НЕ 8 триггер 2 в нулевое состояние,

низкий потенциал с выхода которого сбрасывает триггер 4. Каждый последующий тактовый импульс не может изменить состояние устройства до прихода нового управляющего сигнала, так как триггер 2 остается в нулевом состоянии до момента окончания действия глервого управляющего сигнала.

В случае поступления входного управляющего сигнала во время действия импульса тактовой .частоты единичная инфорJ мация не запишется этим импульсом в триггер 4 поскольку это возможно только передним фронтом импульса. При этом триггер 1 устанавливается инвертированным через инвертор 9 импульсом тактовой частоты в единичное состояние и остается в этом

состоянии при наличии входного управляющего сигнала. После прекращения действия и у1пульса тактовой частоты на выходе инвертора 9 образуется положительный уровень, создающий низкий потенциал на вы„ ходе элемента И-НЕ 5, который устанавливает триггер 3 в нулевое состояние и поддерживает его в этом состоянии до окончания действия входного управляющего сигнала, чем обеспечивается запрещение прохождения импульсов тактовой частоты

0 через элемент И-НЕ б на элемент И-НЕ 7. В этот момент совпадение на элементе И-НЕ 7 высокого уровня напряжения, поступающего от элемента И-НЕ б и задержанного элементом задержки 11 и.мпульса тактовой частоты создает отрицательный перепад напряжения на выходе элемента И-НЕ 7 на время, равное величине задержкгт элемента И. После этого пс задержанному переднему фронту паузы тактовой частоты образуется на выходе элемента И-НЕ 7 передний фронт тактового импульса, задний фронт которого формируется по переднему фронту следующего импульса тактовой частоты. Сформированный тактовый импульс выделяется на выходе устройства аналогично описанному выще. Таким образом, максимальное время, необходимое для формирования выходного импульса, составляет величину не более одного периода тактовой частоты Т. Устройство для выделения одиночного импульса выгодно отличается от известных так как независимо от синхронностк поступления входного управляющего сигнала импульсов тактовой частоты, устройство стабильно формирует выходной импульс по ближайшим перепадам напряжения тактовой частоты. При этом при сохранившейся высокой помехоустойчивости устройства сократилось щ)емя, необходимое для получения выходного сигнала после момента подачи входного управляющего сигнала, что повышает быстродействие устройства в 1,5 раза. Перечисленные достоинства устройства расширяют сферу его применения. Формула изобретения Устройство для выделения одиночного импульса, содержащее 1 8-триггер,В-триггер, информационный вход которого соединен с источником управляющего сигнала и едияичным входомИХ-триггера, единичный выход которого соединен с нулевым входомD-триггера, а нулевой вход RS-триггера соединен с выходом элемента И-НЕ, первый вход которого соединен с выходом инвертора, а второй вход - с единичным выходом } триггера, тактовый вход которого соединен с входом инвертора, отличающееся тем, что, с целью увеличения быстродействия, в него JTV-, IHI I ILI iUJIраЛ153.ТЫДЦ.11-..:1Д МЯИГ.введены дополнитеягннеП-триггер,| 3-триггер инвертор, три двухБходовых элемента И-НЕ, и элемент задержки, пр« этом тактовый вход О-триггера соединен с выходом первого дополнительного элемента И-НЕ, первый вход которого соединен с выходом второго дополнительного элемента И-НЕ, первый вход которого соединен с источником тактовой частоты, входом дополнительного инвертора, тактовым и информационным входами дополнительного D -триггера, единичный выход которого подключен к второму входу второго .дополнительного элемента И-НЕ, а нулевой вход дополнительного -триггера соед:1нен с выходом третьего дополнительного элемента МНЕ и через элемент задержки с вторым о-одом первого дополнительного элемента И-НЕ, первый вход третьего дополнительного элемента И-НЕ соединен с выходом дополнительного инвертора и единичным входом дополнительногоRS-триггера, нулевой вход которого подключен к источнику управляющего сигнала, а выход с вторым входом третьего дополнительного элемента И-НЕ. Источники инфбрмации, принятые во Бивмакие при экспертизе 1.Авторское свидетельство СССР 544115, кл. И 03 К 5/13, 14.07.75. 2.Авторское свидетельство СССР № 595852, кл. И 03 К 3/78, 19.07.76. р---у г I 1JtJ J b-.,-.i.-..-..--..«ru

Ta moBaff частота

Управляющий сигнал

Bb/jfodHoJ сигнал

,Т

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации импульсов | 1980 |

|

SU942253A1 |

| Формирователь одиночных импульсов | 1979 |

|

SU792570A1 |

| Устройство задержки прямоугольных импульсов | 1986 |

|

SU1385278A1 |

| Устройство для выделения одиночного импульса | 1984 |

|

SU1182651A1 |

| Устройство для выделения одиночного импульса | 1976 |

|

SU595852A1 |

| Формирователь импульсов | 1982 |

|

SU1050102A1 |

| Устройство для разделения и синхронизации сигналов | 1985 |

|

SU1325676A1 |

| Преобразователь код-временной интервал | 1983 |

|

SU1164885A1 |

| Устройство тактовой синхронизации | 1978 |

|

SU748839A1 |

| Устройство задержки импульсов | 1981 |

|

SU970665A2 |

Тактовая частота

/праВляюиццй сигнал

Выходной сигнал

Авторы

Даты

1980-06-30—Публикация

1978-04-10—Подача