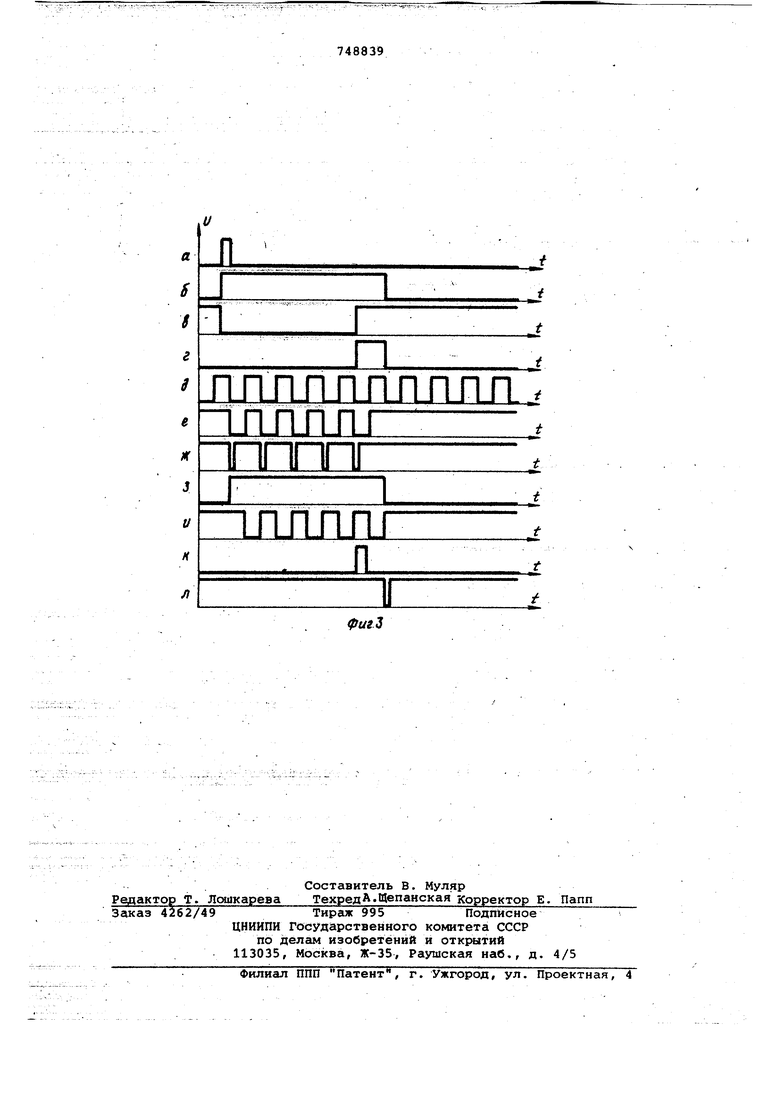

Изобретение относится к импульсно; технике и может быть использовано в цифровых вычислительных машинах, цифровых измерительных, приборах и в цифровых преобразователях, где необходимо привязать асинхронные импульсы к импульсам тактовой частоты или при поступлении управляющего импульса, асинхронного к импульсам тактовой час тоты, выделить одиночный ближайший импульс из последовательности т;актовых импульсов, а также часть последовательности тактовых импульсов. Известны устройства синхронизации, используемые в дискретной автоматике и электронной технике, содержащие три триггера., пять элементов совпащения, два инвертора, шины управляющих и та товых импульсов 1 . Эти устоойства обладают ограниченным диапазоном дли тельностей синхронизируемых импульсов, а также не позволяют выделять опрелеленную часть последовательности тактовых импульсов. Наиболее близким по своей техниче кой сущности к изобретению является устройство тактовой синхронизации, содержащее триггеры, элементы совпадения, логические формирователи импульсов, инвертор, шины тактовых и управляющих импульсов, причем первый вход первого элемента совпадения соединен с шиной уг1$ авляюшйх импульсов, а выход соединен с единичным входом первого триггера, единичный выход которого соединен с логическим входом первого логического формирователя импульсов и с ;первым входом второго элемента совпадения, второй вход которого соединен с шиной тактовых импульсов, нулевой еыход первого триггера соединен с первым входом третьего элемента совпадения, ВТОРОЙ вход которого через инвестор соединен с шиной управляющих импульсов, а выход соединен с нулевым входом второго триггера, единичный выход которого, соединен с третьим входом второго элемента совпадения, а нулевой выход - со втооым входом первого элемента совпгедения, при этом выход первого логического формирователя импульсов соединен с единичным входом второго триггера, тактовый вход SSYOpOro логического формирователя ИМПУЛЬСОВ соединен с шиной тактовых импульсов, а выход - с нулевым входом первого триггера 2. В известном устройстве асинхронные импульсы привязываются не к бли жайшему тактовому импульсу, а через Один тактовый импульс от момента поступления асинхронного импульса. Таким образом, известное устройство обладае низким быстродействием и не позволяет выделять определённую часть последова тельности тактовых импульсов. Целью настоящего изобретения яв ляется повышение быстродействия и рас ширение функциональных, возможностей устройства. Поставленная цель достигается тем что в устройство тактовой синхронизации, содержащее два триггера, три элемента совпадения, два логических формирователя импульсов, инвертор, шинь тактовых и управляющих импульсов, причем первый вход первого элемента совпадения, соединен с шиной управляющих импульсов, а выход соединен с единичным входом первого три гера, единичный выход которого соединен с логическим входом первого ло гического формирователя импульсов и с пеовым входом второго элемента совпадения, втооой вход которого соединен с шиной тактовых импульсов, нулевой вахол первого триггера соединен с первым входом третьего элемент совпадеиия, второй вход которого через инвертор соединен с шиной управляюших импульсов, а выход соединен с нулевым входом второго триггера, единичный выход которого соединен с третьим входом второго элемента совпадения, а нулевой выход подключен ко второму входу первого элемента совпа дения, при этом выход первого логичес кого форлшрователя импульсов соедине с елиничнвлм входом второго триггера, тактовый вход второго логического формирователя импульсов соединен с ши ной тактовых. ИМПУЛЬСОВ, а его вьаход подключён к нулевому входу первого триггера, дополнительно введены два элемента (говпадёния, инвертор, логический элемент И и триггер, единичный и информационный входы которого соединены между собой, а также с информационньрл входом перззого триггера и с выходом первого элемента совпадения, причем первый вход первого допол нйтельйого элемента совпадения соединен с единичном выходом первого триггера, второй вход его через дополнительный инвертор соединен с шиной так товых импульсов, а выход соединен с Тактовым входом первого логического формирователя импульсов, при этом первый вход второго дополнительного элемента совпадения соединен с синхровходом первого триггера,второй его вход соединен с нулевым выходом второго триггера, а выхол соединен с нулевым входом дополнительного тригreba, а его единичный выход соединен с первым входом логического элемента И, второй вход которого соединен с ёданйчным выходом второго триггера,а выход соединен с логическим входом второго логического формирователя импульсов. . На фиг. 1приведена структурная схема устройства тактовой синхпонизации; на фиг, 2 - эпюры напряжений, иллюстрирующие формирование выходных импульсов в режиме синхронизации; на фиг. 3 - эпюры напряжений, иллюстрирующие работу устройства при выделении части последовательности тактовых импульсов. Устройство тактовой синхронизации (фиг. 1) содержит триггеры 1, 2, дополнительный триггер 3, элементы 4, 5,6,7,8 совпадения, логические формирователи 9, 10 импульсов, инверторы 11,12, логический элемент И 13, шину 14 тактовых импульсов, шину 15 СтартИ. импульсов, шину 16 управляющих ИМПУЛЬСОВ, шину 17 Стоп -импульсов. Логический формирователь ИМПУЛЬСОВ имеет два входа: логический и тактовый (на чертеже тактовый вход отмечен за- . черненньви прямоугольником;. На выходе логического формирователя импульсов формируется отрицательный импульс из отрицательного перепада на тактовом входе, если при этом на логический вход подается высокий потенциал.Если на логический вход подается низкийпотенциал, то при любом потенциале на тактовом входе, на его выходе поддерживается высокий потенциал, а выходной импульс не формируется. Устройство работает следующим образом. В Исходном положении триггеры 1 и 2 находятсяв нулевом состоянии, а триггер 3 - в единичном состоянии. На шинах управляющих импульсов и Старт Стоп - импульсов присутствует низкий потенциал. Элементы 4, 5, 7, 8 совпадения закрыты (на их выходах поддерживается высокий потенциал). Элемент 6 совпадения открыт, а на выходе логического элемента И 13 присутствует низкий потенциал. Присутствие тактовых импульсов на шине 14 не изменяет состояния устройства тактовой синхронизации. Режим синхронизации; при поступлении первого же управляющего импульса (фиг. 2а) происходит переключение элемента 4 совпадения и инвертора 12. На выходе элемента 4 совпадения появляется низкий потенциал (фиг. 2в), вызывающий установку триггера 1 в единичное состояние (фиг. 2г), а также и триггера 3 (если он до этого находится в нулевом состоянии).На нулевом выходе триггера 1 устанавливается низкий потенци 1Л, что приводит к появлению на выходе элемента б совпадения высокого потенциала. Триггер 2 не удерживается принудительно в нулевом состоянии низким потенциалом. Высокий потенцисш с единичного выхода триггера 1 подается на входы элементов 5 и 8 совпадения, а также на логический вход формирователя 9. Поскольку поте циал на единичном выходе триггера 2 низкий, то.на выходе элемента 8 продолжает сохраняться высокий потейциал., независимо от значения сигналов на двух осталь.ных его входах. Появление сигнала (отрицательного импульса) на выходе формирователя 9 зависит от временного соотношения между моментом установки в единичное состояние триггера 1 и тактовой частоты (фиг. 26).Поскольку второй вход элемента 5 соединен с шиной так трвых импульсов через инвертор 11, т в промежутке между тактовыми импульсами элемент 5 переходит в нулевое состояние (фиг. 2д). При поступлении отрицательного перепада на тактовый вход формирователя 9 на выходе последнего формируется короткий отрииательный импульс (фиг. 2е). Этот импульс устанавливает в единичное состояние триггер 2 (фиг. 2ж). Низкий потенциал с выхода триггера 2 являет ся запрещающим для прохождения входногосигнала через элемент 4, а низкий потенциал с триггера 1 запрещает воздействие входного сигнала через элемент 6 на нулевой вход триггера 2 Следовательно, к приходу следующего положительного импульса тактовой час тоты на двух из трех входов элемента 8 уже имеются высокие уровни. Пос кольку на обоих входах логического элемента И 13 имеются уже высокие уровни, то и на его выходе появляетс также высокий потенциал, который пос тупает на логический вход формирователя 10. С появлением тактового импульса на входе элемента 8 на его выходе формируется отрицательный импульс (фиг. 2з), синхронный с импульсом тактовой частоты и длительно стью, равной длительности импульса тактовой частоты. По заднему фронту этого же тактового импульса на выходе формирователя 10 формируется отрицательный импульс (фиг. 2и), устанавливающий три гер 1 в нулевое состояние. Потенциал на его нулевом выходе становится выс КИМ. По окончании управляющего импульса потенциал на выходе инвертора 12 также становится высоким, что в свою очередь, приводит к появлению низкого потенциала на выходе элемент 6, который устанавливает триггер 2 в нулевое состояние. Таким образом, устройство синхронизации возвращается в исходное состояние. При поступлении следующего управляющего импульса цикл работы устройс ва повторяется. Режим выделения части последовательности тактовых ИМПУЛЬСОВ следующий . с поступлением Старт -импульса иг. За) триггер 1 устанавливается в единичное (фиг. Зб), а триггер 3 в нулевое состояние (фиг.Зв). При 1ЭТОМ низкий уровень выходного напряжения триггера 3 поступает на первый вход логического элемента И 13, что приводит к появлению на логическом входе формирователя 10 низкого уровня напряжения (фиг. Зг), благодаря чему при любом потенциале на тактовом входе формирователя на его выходе поддерживается высокий потенциал , а выходной импульс не формируется. На нулевом выходе триггера 1 устанавливается низкий потенциал, что приводит к появлению на выходе элемента 6 совпадения высокого потенциала. Триггер 2 не удерживается принудительно в нулевом состоянии низким потенциалом. Высокий потечцигш с единичного выхода триггера 1 подаетдя на входы элементов 5 и 8 совпадения, а также на логический вход форми.рователя 9. Поскольку второй вход эле мента 5 совпадения соединен с шиной тактовых импульсов через инвертор 11, то в промежутке между тактовыми импульсами (фиг. Зд) элемент 5 переходит в нулевое состояние (фиг. Зе). При поступлении отрицательного перепада на тактовый вход формирователя 9 ни выходе последнего Формируется короткий отрицательный ИМПУЛЬС (фиг. Зж). Этот импульс устанавливает в единичное состояние триггер 2 (фиг. Зз). Следовательно, к приходу следующего положительного импульса тактовой частоты на двух из трех входов элемента 8 уже имеются высокие уровни. С появлением тактовых импульсов на входе элемента 8 на его выходе формируются импульсы (фиг. Зи), синхронные с импульса ми тактовой частоты и длитель.ностью, равной длительности импульса тактовой частоты. Таким образом, до . прихода Стоп -импульса на выходе устройства формируется последовательность импульсов, выделяемая из входной последовательности тактовых импульсов. При поступлении Стоп -импульса (фиг. Зк) триггер 3 изменяет свое состояние, т.е. переходит в единичное состояние, так как на его информационном входе имеется высокий потенцисш. Импульс с единичного выхода триггера 3 поступает на первый вход элемента 13, что приводит к появлению на его выходе высокого уровня напряжения, так как на его втором входе имеется высокий потенцией. После установления на единичном выходе триггера 3 высокого потенциала импульсный сигнал на выходе формирователя 10 появляется по заднему фронту ближайшего по времени тактового импульса -(фиг. 3л). Этот сигнсш устанавливает триггер 1 в нулевое состояние. Потенциал на его ( нулевом выходе становится высоким,что в свою очередь, приводит к появлению низкого потенциала на выходе элемента 6, который устанавливает триггер 2 в нулевое состояние, и устройство синхр низации возвращается в исходное состо ние. . Таким образом, при воздействии Старт -импульса на выходе устройства формируются целые ИМПУЛЬСЫ, начиная со следующего после момента появления Старт -импульса. При приходе Стоп -импульса во время действия входного импульса формирование выходного импульса продолжается до образования целого импульса.Воздействие Стоп -импульса во время паузы тактовых импульсов соответствует окончанию формирования последовательности выходных импульсов. Правильная и надежная работа устройства (отсутствие неполноценных импульсов) обеспечивается при любых ком бинациях распределения во времени сиг налов управления и тактовых импульсов Формула изобретения Устройство тактовой синхронизации, содержащее два триггера, три элемента совпадения, два логических формирователя импульсов,инвертор, шины тактовых и управляющих импульсов, причем первый вход первого элемента совпадения соединен с шиной управляющих импульсов, а выход соединен с епиничным входом первого триггеоа, единичный выход которого .соединен с логичес ким входом первого логического Фор шpoвaтeля ИМПУЛЬСОВ и с первым вхопом BTODoro эл« мента совпадения, второй вход которого соединен с шиной тактовых импульсов, нулевой выход пер вого триггера соединен с первым входом третьего элемента совпадения, вто рой вход которого через инвертор соединен с шиной управляющих импульсов, а выход- соединен с нулевым входом вто рого триггера, единичный выход которого соединен с третьим входом второго элемента совпадения, а нулевой выход подключен ко второму входу первого элемента совпадения, выход первого логического формирователя импульсов соединен с единичным входом второго триггера, тактовый вход второго логического формирователя импульсов соединен с шиной тактовых импульсов, а его выход подключен к нулевол входу первого триггера, отличающееся тем, что, с целью повышения быстродействия и расширения функциональных возможностей устройства, в него дополнительно введены два элемента совпадения, инвертор, логический элемент И и триггер, единичный и информационный входы которого соединены между собой, а также с информационным входом первого триггера и с выходом первого элемента совпадения, причем первый вход первого дополнительного элемента совпадения соединен с единичным выходом первого триггера второй вход его через дополнительный инвертор соединен с шиной тактовых импульсов, а выход соединен с тактовым входом первого логического формирователя импульсов, при этом первый вход второго дополнительного элемента совпадения соединен с синхровходом первого триггера, второй его вход соединен с нулевым выходом второго триггера, а выход соединен с нулевым входом дополнительного триггера, а его единичный выход соединен с первым входом логического элемента И, второй вход которого соединен с единичным выходом второго триггера, а выход соединен с логическим входом второго логического формирователя импульсов . Источники информации, принятые во внимание при экспертизе 1.Авторскоесвидетельство СССР 457176,кл. Н 03 К 5/13, 1974. 2.Авторское свидетельство СССР № 453791, кл. НОЗ К 5/153, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1978 |

|

SU764112A1 |

| Формирователь импульсов | 1981 |

|

SU1045371A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ИМПУЛЬСОВ | 2002 |

|

RU2238610C2 |

| Устройство для формирования синхронизированных импульсов | 1981 |

|

SU1019610A1 |

| Формирователь импульсов | 1972 |

|

SU437203A1 |

| Формирователь последовательности кодов | 1974 |

|

SU526870A1 |

| Формирователь синхронизированных импульсов по фронту и спаду | 1982 |

|

SU1115211A1 |

| Формирователь одиночного импульса | 1980 |

|

SU892677A2 |

| Формирователь импульсов | 1979 |

|

SU813733A1 |

| БИБЛИОТЕКА I | 1973 |

|

SU369708A1 |

а S

f г

д

е

к

3

и

Авторы

Даты

1980-07-15—Публикация

1978-06-05—Подача