(54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ДЛЯ ПЕРВИЧНОЙ ОБРАБОТКИ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство для первичной обработки информации | 1978 |

|

SU746569A1 |

| Вычислительное устройство для первичной обработки информации | 1978 |

|

SU746605A1 |

| Вычислительное устройство для первичной обработки информации | 1976 |

|

SU643898A1 |

| Устройство для регистрации кардиосигнала | 1982 |

|

SU1097267A1 |

| Устройство для вычисления координат светового пятна | 1975 |

|

SU525037A1 |

| Ультразвуковой дефектоскоп | 1981 |

|

SU1010516A1 |

| Измеритель уровня высокочастотного напряжения | 1981 |

|

SU945812A2 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА СТАРТСТОПНЫХ СООБЩЕНИЙ | 2006 |

|

RU2312465C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УРОВНЯ ЖИДКИХ СРЕД В РЕЗЕРВУАРАХ | 1997 |

|

RU2123172C1 |

| Формирователь импульсов тока | 1985 |

|

SU1287263A1 |

Изобретение относится к вычислитель ной технике и может быть использовано в устройствах преобразования аналоговых величин в цифровой код. Известны устройства, используемые для первичной обработки информации путем сжатия динамического диапазона при измерении амплитуд импульсов, которое необходимо при обработке одиночных импульсов вследствие узкого динамического диапазона детекторов, в частности пиковых. Для этих целей используются логарифмические усилители 1. Наиболее близким к предлагаемому является вычислительное устройство для первичной обработки информации, содержащее п усилительных каскадов, (п-1) элемент задержки, блок выбора порядка, два пороговых блока, ключ и сумматор, каждый элемент задержки включен мезкду (к -1) и к усилительными каскадами, вы ходы последних подключены ко входам сумматора, сигнальный вход ключа подсо динен к выходу сумматора, управляющий вход связан с выходом первого порогово- го блока, а выход подключен ко входу пикового детектора, выходом подсоединенного ко входу первого порогового блока, подключенного своим выходом к первому управляющему входу блока выбора порядка, который вторым управляющим входом связан с выходом второго порогового блока, соединенного своим входом с выходом п -го усилительного каскада, выходы блока выбора порядка являются ци ровыми выходами всего устройства 2. Этому устройству присуща недостаточная точность, обусловленная зависимостью измеренной величины сигнала от параметров усилительных каскадов и элементов задержки (в первую очередь коэффициентов передачи этих узлов), которые могут изменяться вследствие изменения внещних условий (температуры, напряжения источ- нШса и пр.). Цель изобретения - повышение точности при определении амплитуд одиночных импульсов.

Поставленная цель дЬсгигается тем, что в вычислительное устройство,содержа щее п последовательно соединенных усилительных каскадов и (п -1) элементов задержки, каждый из которых включен между соответствующими предыдущим и последующим усилительными каскадами, первый сумматор, входами подключенный к выходам усилифельных каскадов, а , выходом соединенный с входом первого ключа, выход которого подключен к первому пиковому детектору, пороговый блок, вход которого подключен к выходу rt -го усилительного каскада, введены функциональный блок, аналого-цифровой преобразователь, генератор эталонHbtx импульсов, аттенюатор, второй ключ, второй пиковый детектор и второй сумма- тор, первый вход которого является входом устройства, а выход соединен со входом первого усилительного каскада; выход первого сумматора соединен с первым входом функционального блока и с входом второго ключа, выход которого подключен к входу второго пикового детектора, выходы пиковых детекторов подключены к входам аналого-цифрового преобразователя, разрядные выходы которого являются первым цифровым выходом устройства, второй вход функционального блока соединен с выходом порогового блока, первый и второй выходы функционального блока соединены с упр/авляющими входами первого и второго ключей, третий выход функционального блока подключен к входу генератора эталонных импульсоб, выход которого через аттенюатор подключен ко второму входу второго ; сумматора, группа разрядных выходов функционального блока подключена к группе управляющих входов аттенюатора и является вторым цифровым выходом устройства. При этом функциональный блок содержит генератор импульсов, дешифратор, счетчик, регистр, распределитель импульсов и пороговый элемент, вход которого является первым: входом блока, а выход соединен с первым в хо дом распределителя импульсов, второй вход которого является вторым входом блока, первый, второй и третий выходы распределителя импульсов являются первым, вторым и третьим выходами блока, четвертый выход распределителя импульсов через генератор тактовых импульсов соединен со счетчиком, вход уста новки в нуль которого подключен к пятому выходу распределителя импульсов, шестой выход которого соединен с управляющим входом регистра, группа , разрядных входов которого соединена с группой разрядных выходов счетчика; . подключенной к Группе разрядных входов дешифратора, выход которого соединен с , третьим входом распределителя импульсов, группа разрядных выходов регистра является группой разрядных выходов бло-

ка.- .

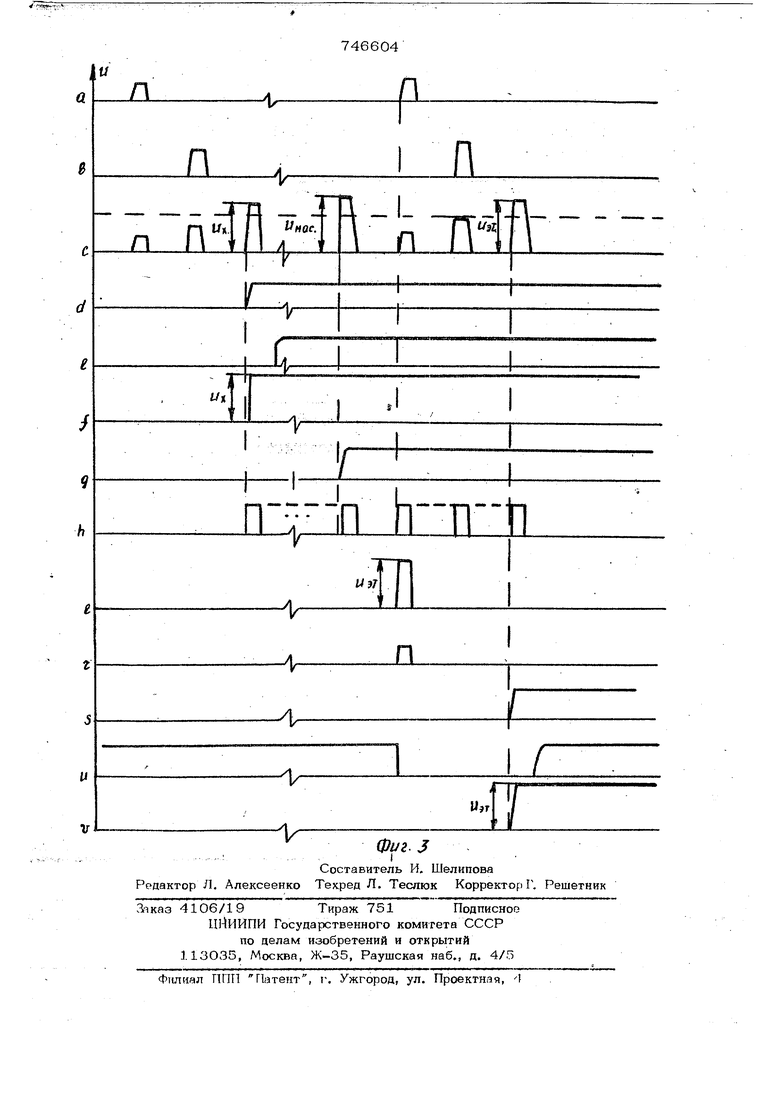

На фиг. 1 изображена блок-схема вычислительного устройства для первичной

обработки информации; на фиг. 2 - схема функционального блока; на фиг. 3 временные диаграммы, поясняющие работу вычислительного устройства.

Вычислительное устройство содержит первый сумматор 1, п усилительных каскадов 2, последовательно соединенных

ДРУГ с другом через элементы 3 задержки. Выходы усилительных каскадов 2 подключены ко входам сумматора 1.

Вход первого усилительного каскада соединен с выходом второго сумматора

4, вход которого является входом устройства, а выход последнего усилительного каскада соединен с входом порогового блока 5. Выход сумматора 1 соединен с сигнальными входами первого 6

и второго 7 ключей.

Выходы ключей б и 7 через пиковые детекторы 8 и 9 соответственно подключены к первому и второму входам аналого-цифрового преобразователя (АЦП) 10,

разрядные выходы последнего являются цифровым выходом мантиссы измеряемого сигнала. Первый вход функционального блока 11 соединен с выходом сумматора 1, а второй вход - с выходом порогового блока 5. Функциональный блок 11 первыми тремя выходами соединен с управляющими входами ключей 6 и 7 и со входом генератора 12 эталонных импульсов соответственно, группа разрядных вы-

ходов блока 11 является цифровьп выходом порядка измеряемого сигнала. Генератор 12 через ,аттенюатор 13 соединен со вторым входом сумматора 4. Группа управляющих входов .аттенюатора 13 подключена к группе разрядньгх выходов : функционального блока.

Функциональный блок 11 содержит пороговый элемент. 14, вход которого является первым входом блока 11; распределитель 15 импульсов, первый вход которого сЬединен с выходом порогового элемента 14, а второй вход является вторым входом блока 11. Первые три выхода распределителя 15 импульсов йвляются соо ветственно тремя первыми выходами бло ка 11, четвертый выход блока 15 через генератор 16 тактовых импульсов соединен со сметным входом счетчика 17, выходы которого соединены с установоч ными входами регистра 18. Пятый выход распределителя 15 соединен с входом установки в нуль счетчика 17, группа выходов которого соединена с группой входов дешифратора 19, выход которого соединен с третьим входом рас пределителя 15, Группа выходов регистр 18 является группой выходов блока 11, управляющий вход регистра 18 соединен с шестым выходом распределителя 15. Вычислительное устройство для первичной обработки информации работает следующим образом.. Входной сигнал через сумматор 4 поступает на цепочку усилительных каскадов 2 и элементов 3 задержки и усиливается ею. Время задержки элемента 3 задержки выбирают больше Длительности измеряемого импульса.. С выхода первого усилительного каск да 2 усиленный импульс сразу поступает навход сумматора 1 (фиг. За), с выход второго- через врьмя равное t . f Зв), а с п -ного каскада - че- рез (п-1) . Таким образом, на выходе сумматора 1 получаем последовательность равномерно разнесенных , во времени импульсов , причем два ближайших отличаются по амплитуде в К у раз, если напряжение на входе каскада не превышает U ос К g . Здесь К у - коэффициент усиления каждого каскада, ицас. -.которое напряжение насыщения каскада. В противном случае амплитуда на выходе (к -1) и к усилительных каскадов различается в число раз, меньшее К у, а напряжения на выходе последующих каскадов равны икас(фиг« 3с). Эта пачка импульсов поступает на пороговой элемент 14 блока 11, а также через ключ 6, который открыт в исходном положении, на пиковый детектор 8; Ключ 7 в исходном положении закрыт и не пропускает импульсы йа вход пикового детектора 9. При приходе импульса с амплитудой U , превышающей минимально допустимое измеряемое напряжение, срабатывает пороговый элемент, 14, сигнал срабатывания поступает на распределитель 15 импульсов, который . вырабатывает импульс запуска генератора 16 тактовых импульсов (фкг. 3d). Через время задержки, необходимое для обработки импульса пиковым детектором 8, распределитель 15 импульсов выраба- тывает импульс, закрьшающий ключ 6, блокируя таким образом прохождение последующих импульсов на вход пакового детектора 8.. На выходе пикового детектора 8 образуется квазипостоянное напряжение, равное Uj (фиг. 3i). Пороговый блок 5 срабатывает через время, равное (r(-N)-t3a9c Taia до момента срабатывания элемента 14 (фиг. Зд), где М -номер усилительного каскада 2, на выходе которого ймплитуда импульса равна U В счетчике 17 происходит вычисление времени ( ) достигается тем, что на счетный вход счетчика 17, предварительно установленного в нуль, после запуска генератора 16 тактовых импульсов .начинают поступать импульсы с периодом следования срабатывании блока 5 распределитель 15 импульсов выделяет сигнал на срыв генерации генератора 16 (фиг. ЗЬ). Одновременно с распределителя 15 импульсов подается управляющий сигнал на регистр 18 для запоминания содержимого счетчика 17. Информация в регистре 18 есть код порядка напряжения сигнала. Через некоторое время задержки импульсом с блока 15 снова запускается генератор 16 (фиг. зЬ ), а также открывается ключ 7 (фиг. Зи) и запускается генератор 12 эталонных импульсов, который вырабатывает импульс эталонной амплитуды иэт- (фиг. ЗВ). Величина Ugr. выбирается приблизительно равной среднему значению рабочих напряжений пикового, детектора. Эталонный импульс, проходя через аттенюатор 13, ослабляется в KJ раз. Далее ослабленный импульс через сумматор 4 поступает на цепочку усилительных каскадов 2 и элементов 3 задержки. На выходе сумматора 1 снова обра зуется пачка, но уже эталонных импульсов. Амплитуда импульса на выходе к -го каскада равна УЭТ , и UHCTC. если . В это время счетчик 17 производит дальнейший счет импульсов генератора. 16. Когда содержимое счетчика 17 становится равным п , рабатывает дешифратор 19, настроенный а этот код (фиг. 3S). К этому времени талонный импульс проходит столько же лементов задержки, сколько прошел изеряемый импульс до срабатывания блока 14. Амплитуда импульса-на выходе сумматора 1 в момент срабатывания деравна иэ-т .Ку шифратора 19 Этот импульс проходит через открыты ключ 7 на ШКовый детектор 9 и 6ёраба ть1вается им, ключ 7 через задержку, необходимую для этой обработки, вакры« ра ется сигналом с распределителя 15 им пульсов (фиг. Зи). На выходе пикового детектора образуется квазипостоянное напряжерие, равное Ug-r .{фиг. 3U). К данному моменту времени на выхрд ах пиковых детекторов 8 и 9 . присутству- ют напряжения (Jx и Ugr, которые по даются соответственно на первый и второй входы блока 10. На выходе послед него образуется код нормированной мантиссы. Все описанные формулы справедливы в случае, если сигналы обрабатываются устройством без искажений. Однако параметры блоков 1, 2, 3, 4 (коэффициенты передачи, дрейф нуля и др.) могут ме Кяться из-за изменений температуры, давления и других внешних условий В результате этгрго соответствующим образом изменяются характеристики измеряемого сигнала, однако характеристики эталонного сигнала измеряются аналогич ным образом. Так реалируется независимость величины измеренного сигнала ст изменений внешних условий. Благодаря введению новых узлов и связей вычисленное мантисса и порядок выдаются в цифровом коде и точность вычисления амплитуд одиночных сигналов с большим динамическим диапазоном, а также стабильность работы устройства при колебаниях температуры, давления и др., значительно повышаются Экономический эффект от применения предлагаемого устройства выражается в повьхшении точности вычисленияв уст ройствах для первичной обработки информации, в которых предлагаемое устройство мрисет быть использовано. Формула изобретения 1. Вычислительное устройство для пе вичной обработки информации, содержащее п последовательно соединенных усилительных каскадов и (п - 1) элементов задержки, каждый из которых включен .между соответствующими предыдущим и последующим усилительным каскадами, первый сумматор, входами подключенный к выходам усилительных Каскадов, авы ходом соединенный с входрм первого клю ча, выход которого подключён к первому пиковому детектору, пороговый блок, вход которого подключен к выходу п -го усилительного каскада, отличаю.Щ е е с я тем, что с целью повышения точности, в устройство введены функцио- нальный блок, аналого-цифровой преобразователь, генератор эталонных импульсов, аттенюатор, второй ключ, вторрй пиковый детектор и второй сумматор, первый вход которого является входом устройства, а выход соединен со входом первого усилительного каскада; выход первого сумматора соединен с первым входом функционального блока и с входом второго ключа, /выход которого подключен к входу второго пикового детектора, выходы пиковых детекторов подключены аналого-цифрового преобразователя, разрядные выходы которого являются первым цифровым выходом устройства, второй вход функционального блока соединен с выходом порогового блока, первый и второй выходы функционального блока соединены с управляющими входами первого и второго ключей, третий выход функционального блока подключен к входу генератора эталонных импульсов, выход которого через аттенюатор подключен ко второму входу второго сумматора, группа разрядных выходов функционального блока подключена к группе управляющих входов аттенюатора и является вторым цифровым выходом устройства,, 2. Устройство по п. 1, о т л Ич а - ю щ е е с я тем, что функциональный блок содержит генератор импульсов, дешифратор, счетчйк, регистр, распределитель импульсов и пороговый элемент, вход которого является, первым входом блока, а выход соединен с первым входом распределителя импульсов, второй вход которого является вторым входом блока, первый, второй и третий выходы распределителя являются первым, вторым и третьим выходами блока, четвертый выход распределителя импульсов через генератор тактовых импульсов соединен со счетчиком, вход установки в нуль которого подключен к пятому выходу распределителя импульсов, шестой выход которого соединен с управляющим входом регистра, группа разрядных входов которого соединена с группой разрядных выходов счетчика, подключенной к группе разрядных входов дешифратора , выход которого соединен с третьим входом рас- пределителя импульсов, группа разрядных; выходов.регистра является группой раз-, рядных выходов блока. Источники шформации, принятые пп п.гммяние при экспертизе . 746

t

фи. 4 1.Патент США № 3662274, кл. 329-192, 1972. 2.Авторское свидетельство СССР по заявке № 2430928/24, кл. G 06 G 7/1 197R УППОТОТИП).

Авторы

Даты

1980-07-05—Публикация

1978-04-21—Подача