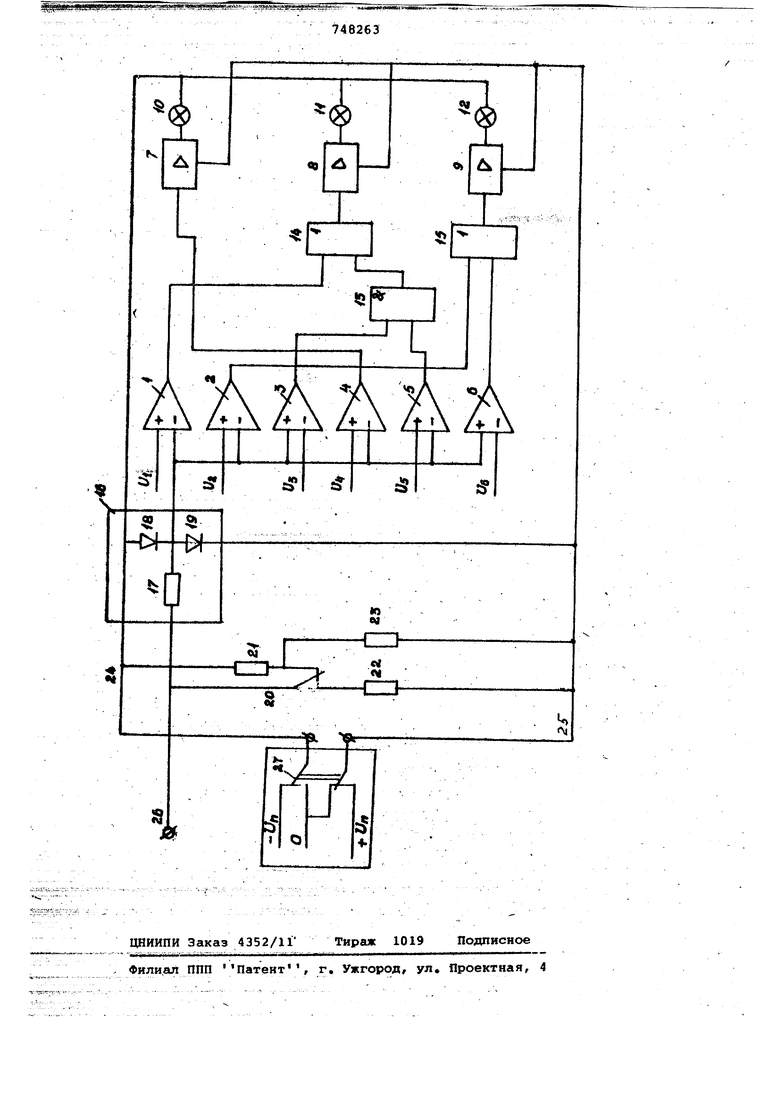

. 1 , Изобретение относится к электроизмерительной технике и может быть использовано для проверки схем, пос троенных на дискретных логических элементах. .Известны логические тестеры, содержащие myij,. два регулируемых исто ника опорного напряжения, дополнительный источник опорного напряжени .ис 6чник напряжения смещения, два блока сравнения , логический преобразоватёль и индикатор уровней И. Недостаток известных логических тестеров - относительно ограниченные функциональные возможности. Наиболее близким по технической сущности является логический тестер содержащий три компаратора, одни вхо да которых соединены с соответствующими источниками опорного напряжения, а другие входы - со входом логического тестера, блок защиты, (усилители,индикаторы и элемент И t2 Однако этот логический тестероб ладает относительно ограниченными функциональными возможностями, так как предусмотрен для проверки только одного типа: логических элементов например ТТЛ - схемой не обеспечй вает воз1можндсти прозвонки контропируо ых цепей под напряжением, а также отыскание согласукядих резисторов в ЭСЛ-схемах (резисторов в цепи эми тера транзистора выходного каскада ЭСЛ-схемы). Цель изобретения - расширение функциональных возможностей. Эта цель достигается тем, что в логический тестер, содержащий первый, второй, третий компараторы, один вход каждого из которых соединен с соответствующим источником опорного напряжения, а другие входы соединены со входом тестера через блок защиты, первый, второй, третий усилители,пер вый и второй индикаторы,соединенные с выходами соответственно первого и второго усилителей, третий индикатор, элемент И, введен четвертый, пятый и шестой компараторы, элементы ИЛИ, резисторы и переключатель режимов, /причем один из входов четвертого, пятого и шестого компараторов соеди;нен с соответствующим источником опорного напряжения, а другие входы ; соединены с выходом блока защиты,BiaxojUJ третьего и пятого , коипараторов соединеньЭ соответстве но со входами элемента И, выходы п вого компаратора и элемента И соединены соответственно со входами пе вого элемента ИЛИ,выходы второго и того компараторов соединены соответ венн.о со входами второго элемента И выход четвёртого компаратора соедин со входом первого усилителя,выходы Аервого и второго элемен- сов ИЛИ сое Г;;шены соответственно со входами второго и третьего усилителей, выхбй третьего усилителя соединен с третьим индикатором, первый и второ резисторы соединены последовательно и включены между шинами питания вход тестера соединенс подвижным контактом переключателя режимов, один контакт которого соединен через третий резистор с одной из щин питания, а второй контакт соединен с ОДНИМ ИЗ выводов первого резистора . На чертеже приведена блок-схема устройства. Логический .тестер содержит компараторы 1-6, усилители 7 - 9, индикаторы 10 - 12, элемент 13 И, элементы ИЛИ 14, 15, блок 16 защиты, содержащий резистор 17 и диоды 18, 19, переключатель 20 режимов, резисторы 21, 22, 23, шины 24, 25 питания, входную клемму 26 и источники опорного напряжения (н чертеже не показаны). Логический тестер работает следующим образом. При проверке ЭСЛ-схем (на чертеже не показаны) на шину 24 питания от источника питания 27, не входящего в состав логического тестера, подается отрицательный потенциал (-Up),a на. шину 25 питания нулевой потенциал Сземля). Величина опорных напряжений U, Uz U.,, U Uj, J соответствующих источников опорного напряжения выбраны такими, чтобы обеспечивалась дифференциация tioУр ням напряжений всех возможных испра .. « . -ч .ш«г ч т1«П тaoч1ulГ ЖM JV ных и неисправных состояний ЭСЛ-схе земля,логический О дефект уровень (между логическим О и л гической , логическая , обрыв и напряжение питания, & тан;жё отсутствие согласующего резистора (на чертеже не показан) в цепях ЭСЛ-схем, наличие одного согласунхцего резистора, наличие двух и более согласующих резисторов. При этом предусмотрены два режииа работы логического тестера: измерение уровней напряжения и отыскание согдйсуютих резисторюв. В первом р ежймё переключатель 20 режима находится в положении, указанном на чертеже, при котором -вход ная клемма 26 соединена со средней ,точкой делителя, образованного резисторами 21, 23,и на .ней устанавливается напряжение /вкояртакое,что Js UB.orjp Js .При этом активен только Компаратор 3 (на его выходе присутствует сигнал логической ),а индикаторы 10-12 не горят.Для определенния состояния исследуемой точки контролируемой ЭСЛ-схемы входную клемму 26 соединяют с этой точкой. При этом потенциал входной клеммы 26 принимает значение потенциала исследуемой точки, и в зависимости от его величины срабатывают соответствующие из компараторов 1 - 6 и горит определенная комбинация индикаторов 1012. Например, состояние земля характеризуется потенциалом входной клеммы 26 (, срабатывают компараторы 1, 2, 4, 5, и горят все индикаторы 10-12. Состоянию логичес. кого О соответствует VJ e, Uj, активны компараторы 4, 5 и горит индикатор 10. При дефектном уровне. потенциала исследуемой точки ЭСЛ-схема и, Uex 4 , срабатывают компараторы 3, 4, 5 и загораются Индикаторы 10, 11. Уровню логической соответствует Мд . на выходах компараторов 3, 5 присутствуют сигналы логической 1и горит индикатор 11. При обрыве потенциала входной 26 J , срабатывает только компаратор 3 и ни один из индикаторов 10 - 12 не горит. Состояние питания характеризуется уровнем Ugy Ug активны ком-параторы 3, 6 и горит индикатор 12гВ режиме отыскания согласующих резисторов переключатель 20 режимов переводится в положение, при котором входная клемма 26 через резистор 22 соединяется с шиной 25 питания , и на ней устанавливается напряжение, близкое к нулю 0Ug,U. Когда входная клемма 26 соединяетря с выходом испытуемой схемы, то в ЗависШёсти от наличия или отсутствия согласующих резисторов на входе логического тестера устанавливаются различные уровни напряжений. -олллтч ст гчя о utja T/r ta-tJt tia итл При отсутствии согласующего резистора на входной клемме 26 сохраняетое к нулю( и, ся напряжение, близкое -12 зажжены . и все индикаторы 10 При наличии одного согласующего резистора на входной клемме 26 устана1вливаё &я напряжение, определяемое делителем, образованным зтим резистором и резистором 22 (u, , и за жжены индикаторы io, 12. При наличии двух согласующих резисторов на входной клемме 26 устанавливается напряжение в пределах , и горит только индикатор 10. При Нсшичии бЙлеё двух согласующих резисторов напряжение на входной клемме 26 пределах DI-UJили и,-Uj, , и го РИТ индикатор 10 или индикаторы 10, 11 вместе.

Возможность дифференциации наличия двух и более согласующих резисторов от других состояний позволяет выявить замыкания между цепями ЭСЛсхем, так как замыкания фактически

эквиваленты наличию двух и более резисторов.

Проз вонка логических цепей в ЭСЛсхемах без отключения питающих напряжений производитсяследующим образом. Один конец исследуемой цепи

землей

соединяют с

через вспомогательный резистор (на чертеже не показан) с сопротивлением, равным сопротивлению резистора 22. При этом на исследуемой цепи устанавливается потенциал между U и U , определяемый делителем напряжения,, образованным согласующими и вспомогательными резисторами. Логический тестер переключателем 20 режи-. мов устанавливается в режим измерения уровней напряжений. При соприкосновении входной клеммы 26 с исследуемой цепью загораются индикаторы 10, 12.

При проверке ТТЛ-схем на шину 25 питания подается положительный потенциал от источника 27 питания , а на шину 24 питания нулевой потенциал (земля). Переключатель режимов 20находится в положении,, указанном на чертеже. При этом логический тестер обеспечивает дифференциацию следующих состояний ТТЛ-схЬм: логический О , дефектный уровень и пять градаций уровня логической , максимальный из которых представляет уровень напряжения источника 27.питания. Наличие нескольких градаций уровня логической 1 облегчает поиск неисправностей при наладке ТТЛсхем.

Блок 16 защиты исключает попадание на входы компараторов 1-6 напряжений обратной полярности, а также повышенного напряжения той же полярности. Например, при проверке ЭСЛ- схем, если на входную клем.му 26 подается положительное напряжение, открывается диод 19, чем закорачивается вход компараторов 1-6.

При поступлении на входную клемму 26 повышенного напряжения той же полярности, открывается-диод 18 чем исключается попадание этого напряжения на входы компараторов 1 6

Схема логического тестера позволяет просто проверять исправность индикаторов 10 - 12. Для этого достаточно переключатель 20 режимов перевести в положение, соответствующее режиму отыскания согласующих

резисторов. При этом должны загореть ся все три индикатора 10 - 12,

Логический тестер обладает широкими функциональными возможностями при проверке как ЭСЛ-, так и ТТЛсхем, что облегчает работу по наладке устройств вычислительной техт ,ники, построенных на этих схемах.

Формула изобретения

10

Логический тестер, содержащий первый, второй, третий компараторы, один вход каждого из которых соединен с соответствующим источником

5 опорного напряжения, а другие входы соединены со входом тестера через блок защиты, первый, второй, третий усилители, первый и второй индикаторы, соединены с выходами

0 соответственно первого и второго усилителей, третий -индикатор, элемент И, отличающийся тем, что с целью расширения функциональных возможностей, в него введены четвертый, пятый, шестой компараторы, элементы ИЛИ, резисторы и переключатель режимов, причем один из входов четвертого, пятого и шестого компараторов соединен с соответствующим источником опорного напряжения, а другие входы соединены с выходом блока защиты, выходы третьего и; пятого компараторов соединены соответственно со входами элемента

5 1 выходы первого компа ратора и

элемента И соединены соответственно со входами первогоэлемента ИЛИ,выхо; второго и шестого компараторов соеденены соответственно со входами.вто рого элемента ИЛИ,выход четвертого

0 компаратора соединен до входом первого усилителя, выходы первого и второго элементов ИЛИ соединены соответственно со входами второго и

C третьего усилителей, выход третьего усилителя соединен с третьим индикатором. Первый и второй резисторы соединены последовательно и включены между шинами питания, вход тестера соединен с подвижным контак .том переключателя режимов, один кои такт которого соединен через третий резистор с одной из ,шин питания, а второй контакт соединен с одним из выходов первого резистора.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР Г) 513330. кл. 2 С 01 И 31/28.1976. 0 2, Акцептованная заявка Великобритании W 1447291, кл.б И, 1967, (прототип) .,

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ТЕСТЕР | 1997 |

|

RU2133475C1 |

| Пробник для проверки логических устройств на микросхемах эмиттерно-связанной логики | 1983 |

|

SU1108373A1 |

| Устройство для контроля сопротивления | 1983 |

|

SU1147987A1 |

| Пороговый логический элемент | 1975 |

|

SU600711A1 |

| Устройство для автоматического контроля параметров электрических цепей | 1988 |

|

SU1638670A1 |

| Устройство для измерения токовых шумов двухполюсников | 1987 |

|

SU1495836A1 |

| Устройство для ускоренного заряда аккумуляторной батареи | 1988 |

|

SU1557630A2 |

| Устройство для контроля логических схем | 1984 |

|

SU1191847A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1654823A1 |

| Устройство для автоматического контроля электрических цепей с конденсаторами | 1984 |

|

SU1239654A1 |

Мш«мьММ,.ли

Авторы

Даты

1980-07-15—Публикация

1978-05-12—Подача